信号质量边沿、振荡、串扰及时序处理剖析

电子说

1.4w人已加入

描述

随着市场更高的需求,现在的设计者不得不考虑提高时钟频率,缩短信号的上升边沿。

对于市面上大多数电子产品而言,普遍认为当时钟频率超过100 mhz或上升边沿小于1ns时,信号质量因素就必须考虑。

在模拟电路中,设计者主要考虑物理源引发的噪声,物理源通常包括热噪声、短噪声等。

一方面,这些噪声源决定了所能放大信号的最小下限;另一方面也决定了所能放大信号的最大上限。

在数字电路中,噪声不是来自于基本的物理源,而是来自于运行着的电路本身,尤其是其他信号频繁翻转所产生的噪声。

高度化的互连密度导致了每个网络与其余网络相隔更近,从而引起了相邻网络的容性耦合。

从而接上文接着讲信号质量边沿、振荡、串扰及时序处理的相关技术处理及解决。

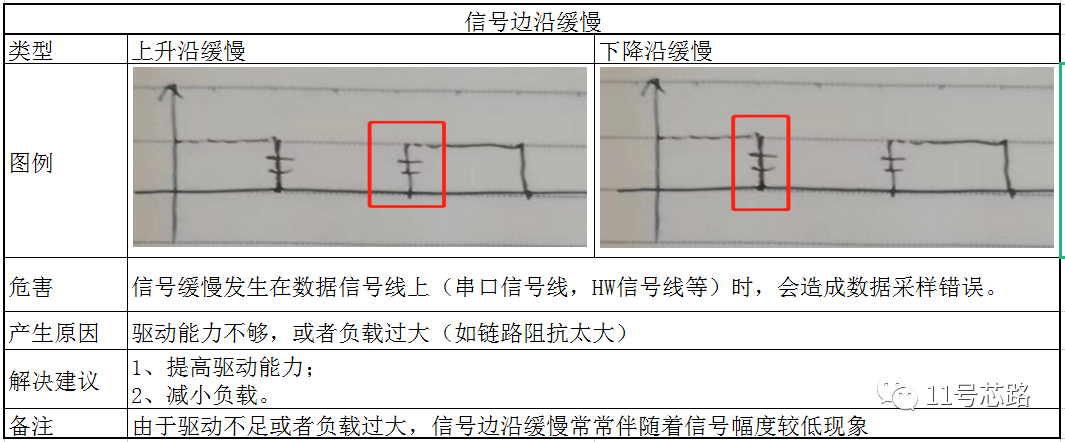

1、信号边沿缓慢

2、信号振荡

3、信号的建立和保持时间

4、信号串扰

阅读 21

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

信号完整性仿真三个重点:信号质量、串扰和时序2023-04-03 2673

-

信号完整性-串扰的模型2023-09-25 3678

-

信号的串扰介绍2024-09-12 5250

-

PCB设计中如何处理串扰问题2009-03-20 5085

-

高速互连信号串扰的分析及优化2010-05-13 2796

-

信号串扰的原理、实例以及实现步骤2023-07-03 5718

-

pcb上的高速信号需要仿真串扰吗2023-09-05 1674

-

PCB布线减少高频信号串扰的措施都有哪些?2023-10-19 2802

-

什么是串扰?该如何处理它?2023-12-05 1878

全部0条评论

快来发表一下你的评论吧 !