DDR3和DDR4存储器学习笔记

存储技术

描述

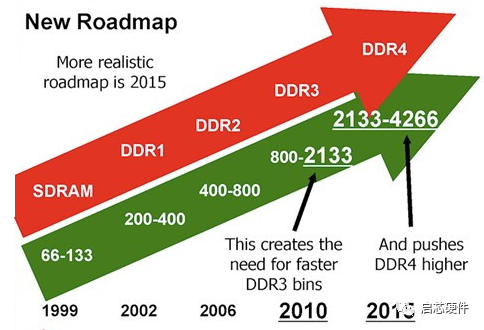

DDR存储器发展的主要方向一言以蔽之,是更高速率,更低电压,更密的存储密度,从而实现更好的性能。

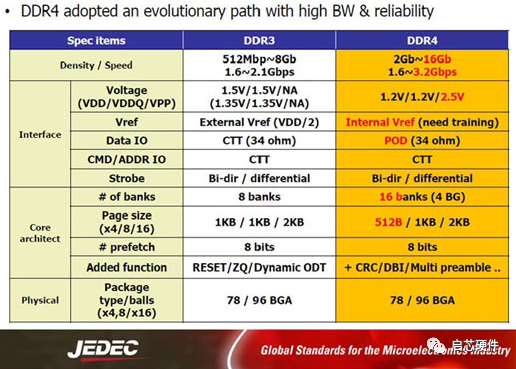

DDR4 SDRAM(Double Data Rate Fourth SDRAM):DDR4提供比DDR3/ DDR2更低的供电电压1.2V以及更高的带宽,DDR4的传输速率目前可达2133~3200MT/s。DDR4 新增了4 个Bank Group 数据组的设计,各个Bank Group具备独立启动操作读、写等动作特性,Bank Group 数据组可套用多任务的观念来想象,亦可解释为DDR4 在同一频率工作周期内,至多可以处理4 笔数据,效率明显好过于DDR3。 另外DDR4增加了DBI(Data Bus Inversion)、CRC(Cyclic Redundancy Check)、CA parity等功能,让DDR4内存在更快速与更省电的同时亦能够增强信号的完整性、改善数据传输及储存的可靠性。

以下两张图可以清晰对比DDR3以及DDR4的参数差异:

POD 和SSTL的比较

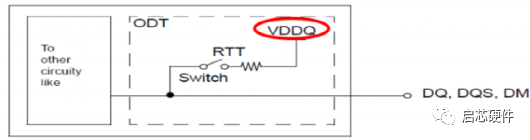

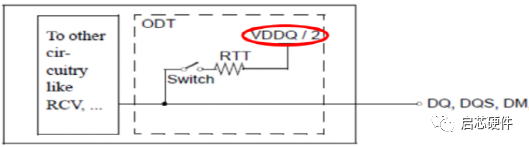

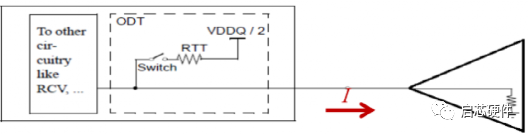

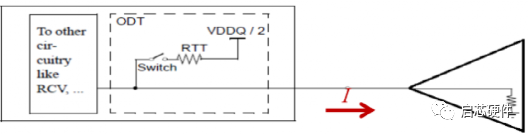

POD作为DDR4新的驱动标准,最大的区别在于接收端的终端电压等于VDDQ,而DDR3所采用的SSTL接收端的终端电压为VDDQ/2。这样做可以降低寄生引脚电容和I/O终端功耗,并且即使在VDD电压降低的情况下也能稳定工作。其等效电路如图1(DDR4), 图2(DDR3)。

图1 POD ((Pseudo Open Drain)

图2 SSTL(Stub Series Terminated Logic)

这样修改的优点是:

可以看出,当DRAM在低电平的状态时,SSTL和POD都有电流流动

图3 DDR4

图4 DDR3

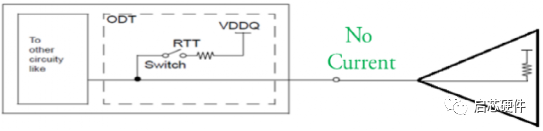

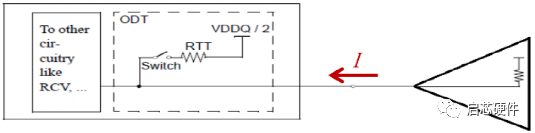

而当DRAM为高电平的状态时,SSTL继续有电流流动,而POD由于两端电压相等,所以没有电流流动。这也是DDR4更省电的原因

图5 DDR4

图6 DDR3

BG设计原因

到了DDR4的时代,JESD组织认为,数据预取的增加变得更为困难,所以推出了Bank Group的设计。

Bank Group架构是什么样的,有何优势呢?

具体来说就是每个Bank Group可以独立读写数据,这样一来内部的数据吞吐量大幅度提升,可以同时读取大量的数据,内存的等效频率在这种设置下也得到巨大的提升。DDR4架构上采用了8n预取的Bank Group分组,包括使用两个或者四个可选择的Bank Group分组,这将使得DDR4内存的每个Bank Group分组都有独立的激活、读取、写入和刷新操作,从而改进内存的整体效率和带宽。如此一来如果内存内部设计了两个独立的Bank Group,相当于每次操作16bit的数据,变相地将内存预取值提高到了16n;如果是四个独立的Bank Group,则变相的预取值提高到了32n。

DDR3 Multi-drop bus

DDR4 Point to Point

在DDR3内存上,内存和内存控制器之间的连接采用是通过多点分支总线来实现。这种总线允许在一个接口上挂接许多同样规格的芯片。我们都知道目前主板上往往为双通道设计四根内存插槽,但每个通道在物理结构上只允许扩展更大容量。这种设计的特点就是当数据传输量一旦超过通道的承载能力,无论你怎么增加内存容量,性能都不见的提升多少。这种设计就好比在一条主管道可以有多个注水管,但受制于主管道的大小,即便你可以增加注水管来提升容量,但总的送水率并没有提升。

因此在这种情况下可能2GB增加到4GB你会感觉性能提升明显,但是再继续盲目增加容量并没有什么意义了,所以多点分支总线的好处是扩展内存更容易,但却浪费了内存的位宽。(通过这个理解带宽)

数据总线倒置 (DBI)

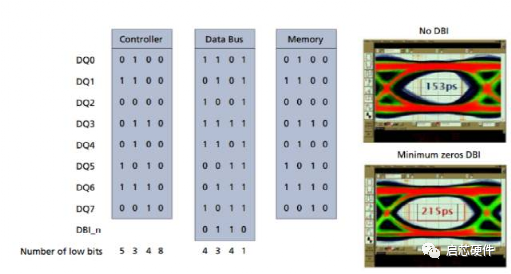

如上面描述,根据POD的特性,当数据为高电平时,没有电流流动,所以降低DDR4功耗的一个方法就是让高电平尽可能多,这就是DBI技术的核心。

举例来说,如果在一组8-bit的信号中,有至少5-bit是低电平的话,那么对所有的信号进行反转,就有至少5-bit信号是高电平了。DBI信号变为低表示所有信号已经翻转过(DBI信号为高表示原数据没有翻转)。这种情况下,一组9根信号(8个DQ信号和1个DBI信号)中,至少有五个状态为高,从而有效降低功耗。

图7 DBI Example

参考电压Vref

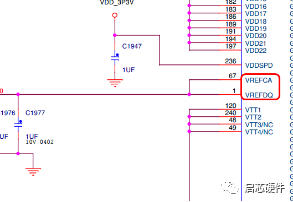

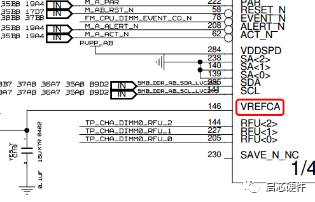

众所周知,DDR信号一般通过比较输入信号和另外一个参考信号(Vref)来决定信号为高或者低,然而在DDR4中,一个Vref却不见了,先来看看下面两种设计,可以看出来,在DDR4的设计中,VREFCA和DDR3相同,使用外置的分压电阻或者电源控制芯片来产生,然而VREFDQ在设计中却没有了,改为由芯片内部产生,这样既节省了设计费用,也增加了Routing空间。

图9 DDR3设计

图10 DDR4设计

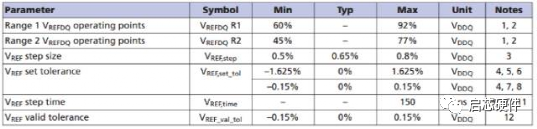

DRAM内部VREFDQ通过寄存器(MR6)来调节,主要参数有Voltage range, step size, VREF step time, VREF full step time ,如下表所示。

表4 参考电压

每次开机的时候,DRAM Controller都会通过一系列的校准来调整DRMA端输入数据信号的VREFDQ,优化Timing和电压的Margin,也就是说,VREFDQ 不仅仅取决于VDD, 而且和传输线特性,接收端芯片特性都会有关系,所以每次Power Up的时候,VREFDQ的值都可能会有差异。

总结:

DDR4内存具有更高的运行速度和更低的电压需求,从而提高了计算机的性能和能效。DDR4的主要特点和优势是:

速度和带宽提升: DDR4相对于DDR3来说,提供更高的数据传输速度和内存带宽。它的速度通常以MT/s(兆传输每秒)来衡量,而不是DDR3中的MHz。DDR4的速度通常从2133MT/s开始,并可以高达3200MT/s或更高。这意味着DDR4能够提供更快的数据访问速度,有助于改善计算机性能。

低电压: DDR4采用1.2伏的低电压供电,相对于DDR3的1.5伏来说,能够降低能耗,减少热量产生,提高电池寿命。这对于笔记本电脑和移动设备尤为重要。

更高的密度:DDR4允许更高密度的内存模块,这意味着单个内存模块可以容纳更多的存储容量。这对于需要大量内存的服务器、工作站和高性能计算任务非常有用。

排队和流水线技术: DDR4引入了排队和流水线技术,使内存控制器能够更高效地管理数据传输,降低延迟,提高性能。

错误校验与纠正(ECC): DDR4支持ECC,这是一种错误检测和纠正技术。它有助于提高内存的可靠性,防止数据损坏或丢失,特别是在对数据完整性要求很高的应用中。

总之,DDR4内存是当前计算机领域的一种重要技术,它具有更高的速度、更低的电压需求、更高的存储密度和更好的性能,从而提高了计算机的性能和能效。

-

JEDEC发布DDR3存储器标准的DDR3L规范2010-08-05 4339

-

DDR4与DDR3的不同之处 DDR4设计与仿真案例2023-09-19 6737

-

5V 输入、10A负载DDR3/DDR4通用电源解决方案2018-12-24 4510

-

新版的UltraScale用户手册指导FPGA与DDR3和DDR4 SDRAM连接2017-02-08 2236

-

ddr3及ddr4的差异对比2017-11-07 56627

-

ddr4和ddr3内存的区别,可以通用吗2017-11-08 32692

-

SDRAM,DDR3,DDR2,DDR4,DDR1的区别对比及其特点分析2017-11-17 28461

-

DDR3和DDR4的设计与仿真学习教程免费下载2019-10-29 1768

-

DDR4相比DDR3的变更点2021-11-06 1505

-

PI2DDR3212和PI3DDR4212在DDR3/DDR4中应用2023-07-24 842

-

DDR4和DDR3内存都有哪些区别?2023-10-30 15069

-

具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表2024-03-13 550

-

如何选择DDR内存条 DDR3与DDR4内存区别2024-11-20 13389

-

DDR3、DDR4、DDR5的性能对比2024-11-29 23584

-

三大内存原厂或将于2025年停产DDR3/DDR42025-02-19 4421

全部0条评论

快来发表一下你的评论吧 !