SRAM的基础电路及原理分析

存储技术

描述

硬件面试的时候,看到应聘者简历上写着,有过AMD工作或实习经历,熟悉CPU和内存。于是我问,那请你画一下SRAM和DRAM的基本cell出来,然后简要说一下工作原理及特点,但是没能说出来。

有不少人这两个基本单元画不出来,不能算熟悉CPU和内存,这两个深究下来就太复杂了,不展开说,本文主要分析SRAM相关的基础电路及原理分析,便于大家更好的理解。

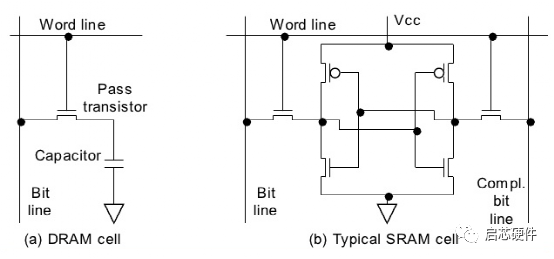

先上SRAM和DRAM的电路基本单元,如下图

从上图可以看到二者最明显的区别就是,SRAM的结构比DRAM的要复杂很多,这也就造成了SRAM会比DRAM贵很多。对比二者,区别如下

大家都知道,CPU是负责运算和处理的,而存储器则是负责交换数据的。有人是这么比喻的(场景是工程师的工作),说CPU就是工程师本人,内存就像是工作台,需要及时处理的东西需要先拿到工作台上才方便处理。那么硬盘是什么呢?硬盘就像柜子,存放电子器件仪器用的仓库,存东西。

存储器有两个基本的构成单元,SRAM 和 DRAM,充分理解这两个概念以及电路原理,对于学习应用CPU构架以及DDR非常有用。DRAM就是动态(Dynamic)随机存储器,SRAM是静态(Static)随机存储器。这一动一静的本质是什么呢?先说静态随机存储器,它是利用如D触发器的结构来完成数据的读取与写入的,资料的写入不需要刷新动作,这样不需要刷新动作的就成为静态。同时,这样使得控制器设计很简单,存取的速度比DRAM快很多。适合于高速存储的应用场景比如CPU的cache缓存。

理解了静态随机存储器之后,动态随机存储器就好理解了。动态就是指利用电容的充放电来实现资料的写入与读取动作,因为电容会慢慢放电,如果放电到阈值以下,数据可能就会丢失了,因此需要每隔一段时间来做刷新的动作,以保持资料的完整性。最常见的就是手机和电脑的内存了。

1 第一层认识—一个D触发器构成最简单 SRAM

首先,可以从最基础数字电路开始。有一个很基本但是深刻且直接的认识:SRAM cell最简单的构成单元就是一个D触发器,如下图所示,D触发器是数字电路系统里面的一个基本单元。

1 bit的SRAM单元的核心电路就是一个D触发器。当有power存在的时候,因为D触发器的特性,数据可以保存,不需要刷新。触发器是具有记忆功能的,具有两个稳定的信息存储状态。D触发器的特性方程是:Q(n+1)=D;也就是记忆前一个状态,可以从RS触发器出发,写一下真值表,推算就很好理解了。波形图如下所示:

2 第二层认识—4个单管构成的SRAM

然后,可以用基本晶体管层面来搭建一个简单的SRAM单元,仅仅由4个NMOS管和两个电阻构成的。

【电路详细分析】

SRAM的整个单元具有对称性。其中除了Q1和Q2的部分,是用来锁存1位数字信号。Q1,Q2是传输管,它们在对存储器进行读/写操作时完成将存储单元与外围电路进行连接或断开的作用。

对单元的存取通过字线WL(Word Line)使能,字线WL为高电平时传输管导通,使存储单元的内容传递到位线BL(Bit Line),单元信息的反信号传递到位线BL#,外围电路通过BL和BL#读取信息。

写操作时,SRAM单元阵列的外围电路将电压传递到BL和BL#上作为输入,字线WL使能后,信息写入存储单元。

3 第三层认识--6管单管构成的SRAM

最后,可以从IC的制造层面来看。其实,大部分与第二层差不多,只是M2与M4用PMOS代替。SRAM中的每一bit存储在由四个场效应管(M1, M2, M3, M4)构成两个交叉耦合的反相器中。另外两个场效应管(M5,M6)是存储基本单元到用于读写位线(Bit Line)的控制开关。

一个SRAM基本单元有0和1两个电平稳定状态。SRAM 基本单元由两个CMOS反相器组成。两个反相器的输入、输出交叉连接,即第一个反相器的输出连接第二个反相器的输入,第二个反相器的输出连接第一个反相器的输入。这就能实现两个反相器的输出状态的锁定、保存,即存储了一个位的状态。分析简图:

【详细的电路分析】

SRAM的基本单元存在三种状态:standby(空闲),read(读)和write(写)。

第一种状态:standby

如果WL没有选为高电平,那么M5和M6两个作为控制用的晶体管处于断路状态,也就是基本单元与位线BL隔离。而M1-M4组成的两个反相器继续保持其状态。

第二种状态:read

首先,假设存储的内容为1,也就是Q处为高电平。读周期初始,两根位线BL, BL#预充值为高电平,因为读写状态时,WL也会为高电平,使得让作为控制开关的两个晶体管M5, M6导通。

然后,让Q的值传递给位线BL只到预充的电位,同时泄放掉BL#预充的电。具体来说,利用M1和M5的通路直接连到低电平使其值为低电平,即BL#为低;另一方面,在BL一侧,M4和M6导通,把BL直接拉高。

第三种状态:write

写周期开始,首先把要写入的状态加载到位线BL,假设要写入0,那么就设置BL为0且BL#为1。然后,WL设置为高电平,如此,位线的状态就被载入SRAM的基本单元了。具体分析过程,可以自己画一下。

总结:

SRAM和DRAM之间的区别在于它们的工作原理和存储方式。

SRAM是静态随机存取存储器,它使用触发器来存储数据,速度快但容量较小。

而DRAM是动态随机存取存储器,它使用电容来存储数据,速度较慢但容量较大。

此外,SRAM不需要刷新操作,而DRAM需要定期刷新以保持数据的有效性。

根据应用需求,选择适合的存储器类型是非常重要的。

-

sram读写电路设计2023-12-18 5057

-

DRAM和SRAM对比分析哪个好?2022-01-20 2195

-

对SRAM时序进行分析2022-01-07 1454

-

考虑栅氧化层SBD,NBTI和MOSFET的SRAM稳定性分析2021-03-29 1036

-

两种SRAM的电路结构2020-09-19 9502

-

SRAM存储器具有较高的性能,它的优缺点分析2020-07-16 7649

-

单端口SRAM与双端口SRAM电路结构2020-07-09 6826

-

SRAM存储器写操作分析2020-04-30 2279

-

基于28nm工艺低电压SRAM单元电路设计2020-04-01 2884

-

浅谈异步SRAM存储器接口电路图2020-03-08 4575

-

基于SRAM的可重配置电路PLD2019-02-23 1481

-

SRAM,SRAM原理是什么?2010-03-24 9270

-

基于SRAM的可重配置电路2009-06-20 1240

-

sram电路图2008-10-14 3807

全部0条评论

快来发表一下你的评论吧 !