集成逻辑分析仪(ILA)的使用方法

描述

大家好,这里是程序员 杰克 。一名平平无奇的嵌入式软件工程师。

在日常FPGA开发过程中,逻辑代码设计完成后,为了验证代码逻辑的正确性,优先使用逻辑仿真(modesim)进行验证。仿真验证通过后进行板级验证时,使用逻辑分析仪进行分析和验证逻辑是否正确。FPGA两大主流厂商的软件集成逻辑分析仪供使用,Altera的Quartus自带SignalTap、Xilinx的Vivado自带ILA逻辑调试工具。

本篇总结和分享在Xilinx编译工具Vivado环境下,使用内嵌的逻辑分析仪(ILA)的4种方法:

- HDL代码实例化ILA IP核

- Block Design添加ILA IP核

- Synthesis后对Nets执行Mark Debug操作

- 在HDL代码中使用属性关键字mark_debug

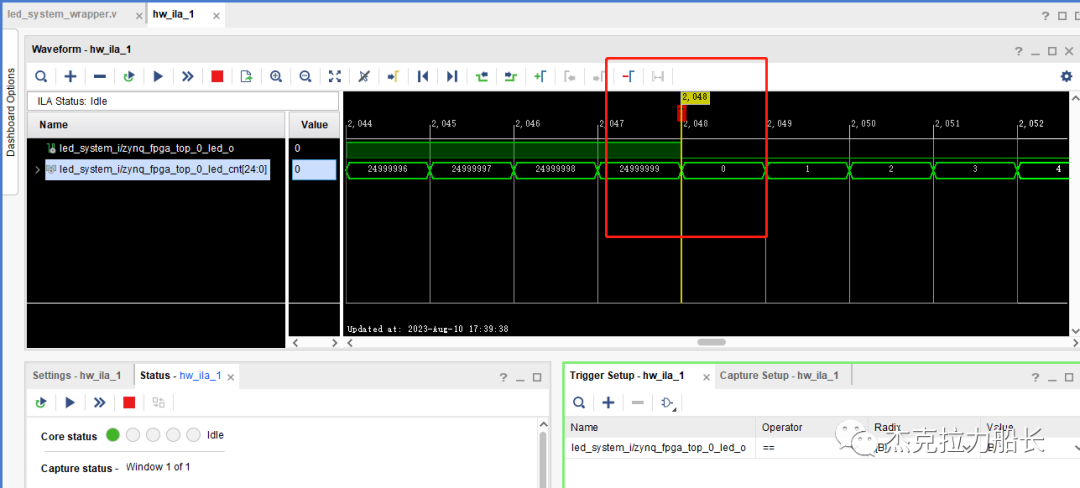

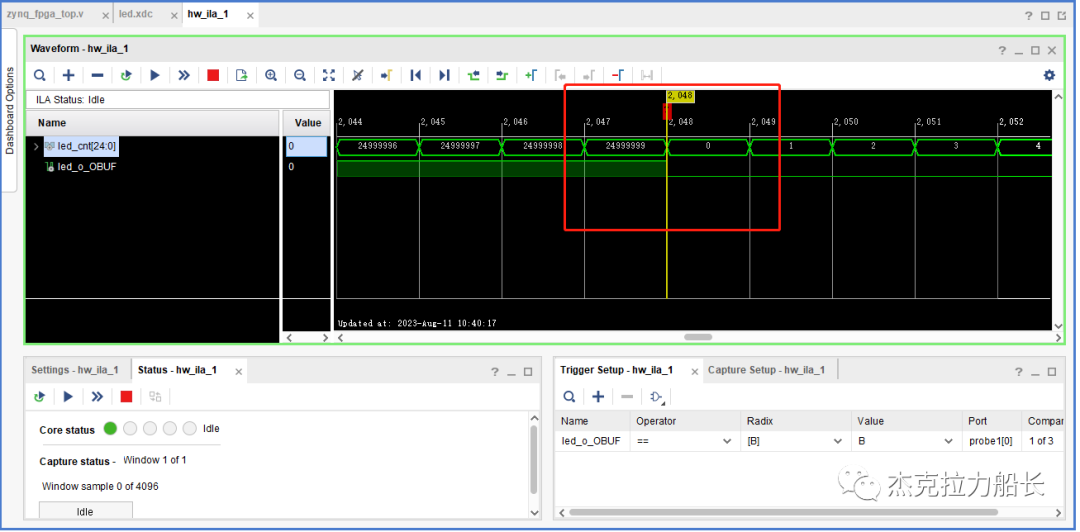

本文以"LED每0.5s间隔亮灭"工程为例,观测 led[0]信号以及led_cnt[24:0]时钟计数信号 ,演示ILA使用的4种方法以及相关的注意事项。

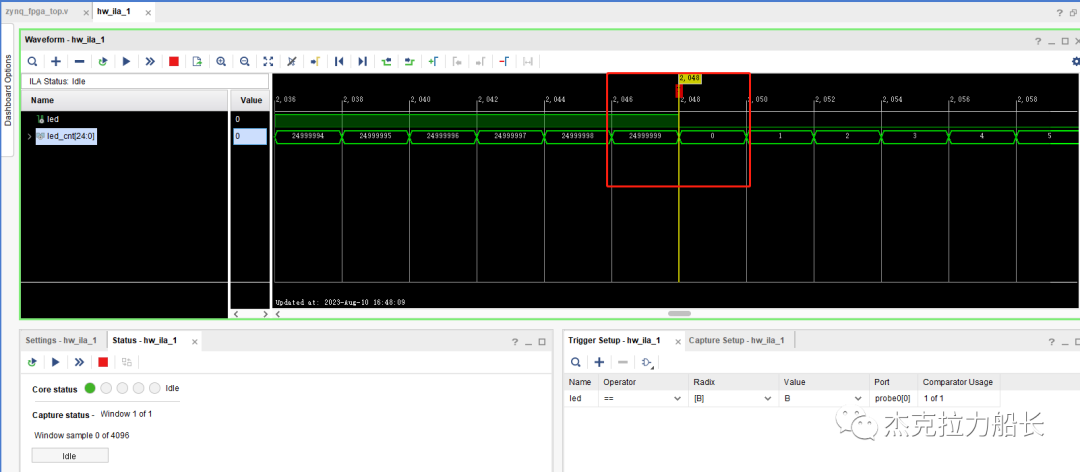

01 HDL代码实例化ILA IP核

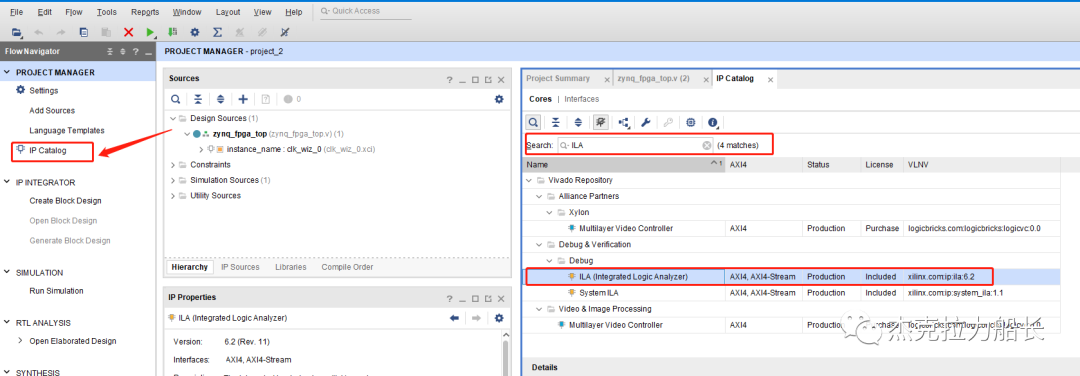

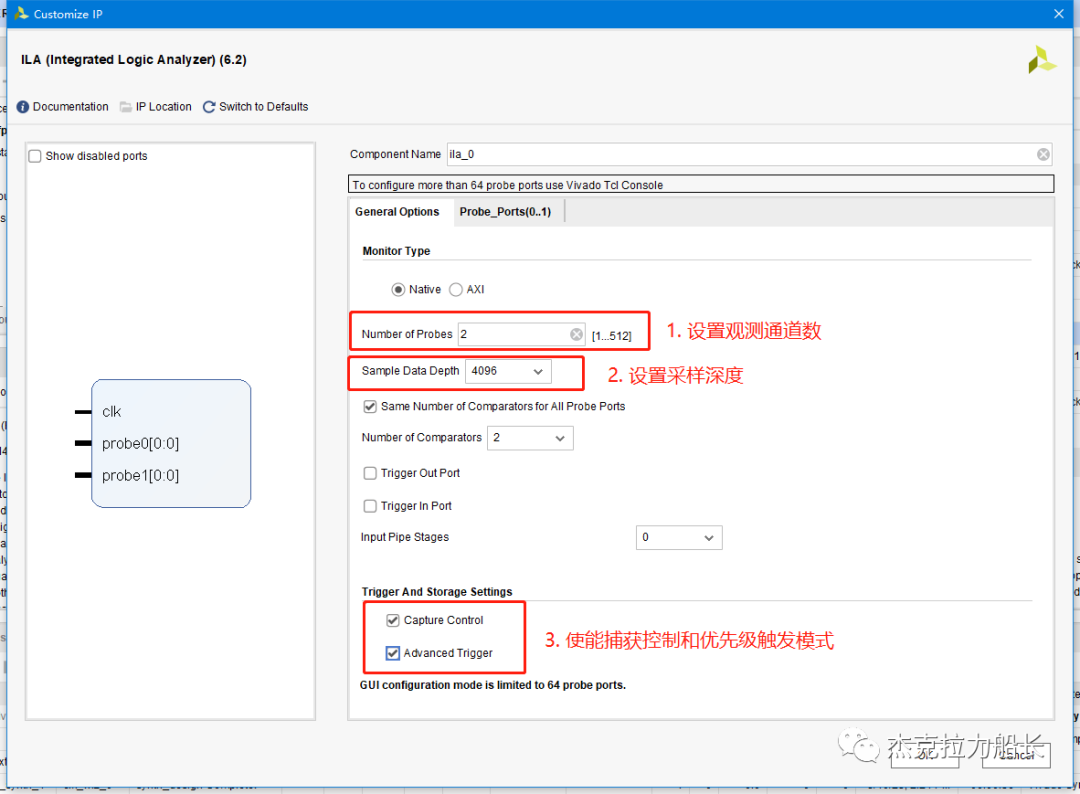

在IP Catalog中搜索ILA,然后双击该IP核进行配置。

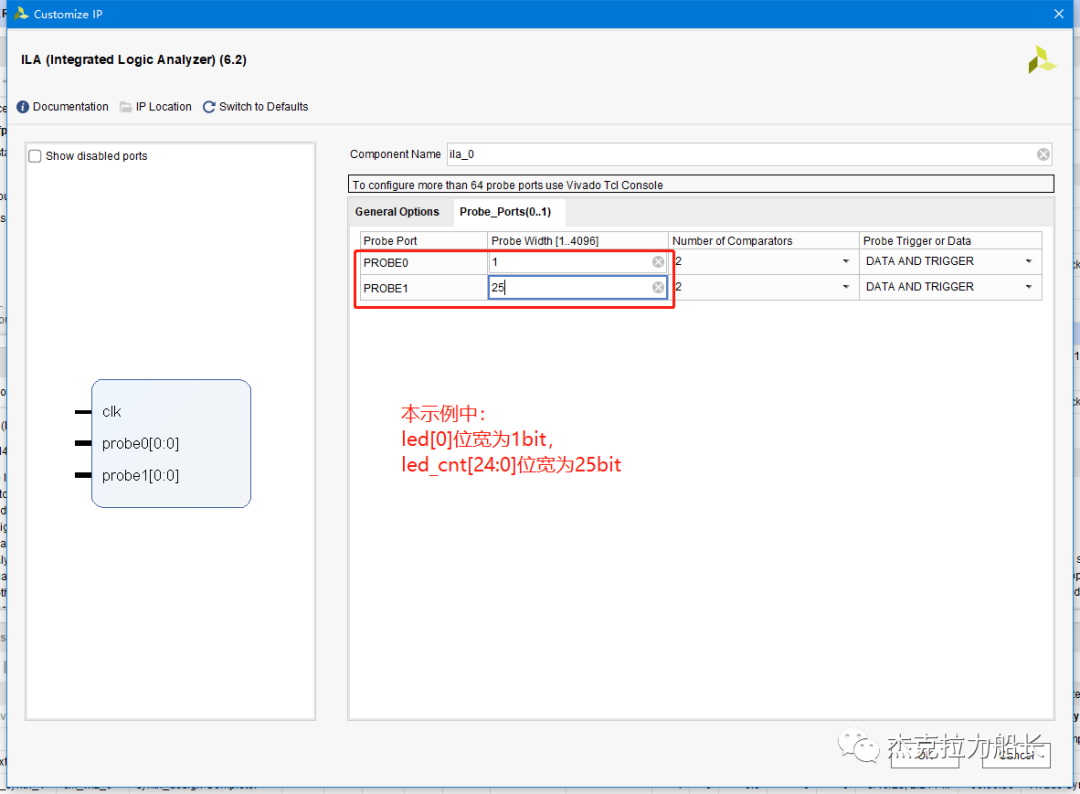

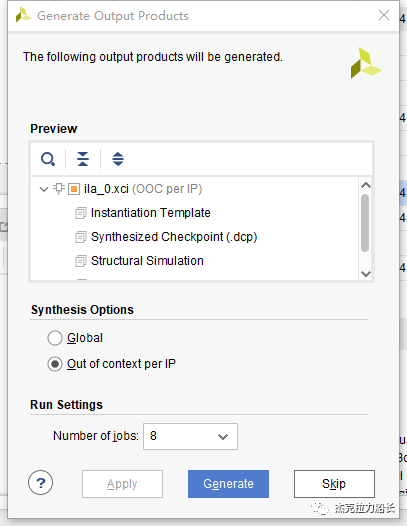

本示例中led[0]、led_cnt[24:0]信号位宽分别为1、25bit,具体配置如下所示;配置完成后,点击“OK”;在弹出的界面点击“Generate”完成IP核的配置和生成。

在Verilog代码中对刚生成的ILA核进行实例化,在具体代码添加例化代码,如下所示:

ila_0 ila_0_inst0 (

.clk (clk ), // input wire clk

.probe0 (led ), // input wire [0:0] probe0

.probe1 (led_cnt) // input wire [24:0] probe1

);

综合、实现、生成bit后写到FPGA芯片便可观测到信号(此处不做演示)。

特别说明:对于纯FPGA工程,杰克推荐该方式去使用ILA;

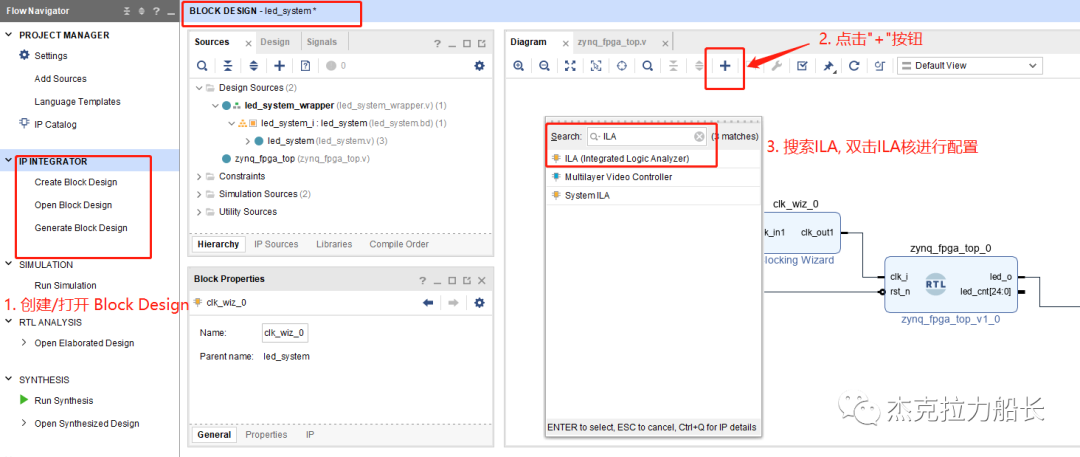

02 Block Design添加ILA IP核

在Vivado中,除了使用HDL语言去描述设计,还可以通过Block Design图形化连接的方式进行设计。7系列的软核MicroBlaze、带硬核的SOC芯片(ZYNQ、MPSOC等)的设计都是通过Block和HDL相结合来描述设计。本文仍以纯FPGA方式来说明在Block Design中使用ILA核(纯FPGA开发不建议)。ILA使用操作如下:

创建/打开Block Design,在Diagram界面,点击“+”按钮,搜索ILA,然后双击该IP核进行配置。

参数配置的方式与上一小节一致,这里不作赘述。不同之处是在Block Design中使用ILA核,ILA核的实例化HDL代码会自动生成到Block Design文件中。

综合、实现、生成bit后写到FPGA芯片便可观测到信号(此处不做演示)。

特别说明:

带MicroBlaze软核/ARM硬核的FPGA的复杂设计中,模块接口的信号观测ILA使用该方法;模块内部信号的观测ILA使用上一小节的方式;两者可结合使用。

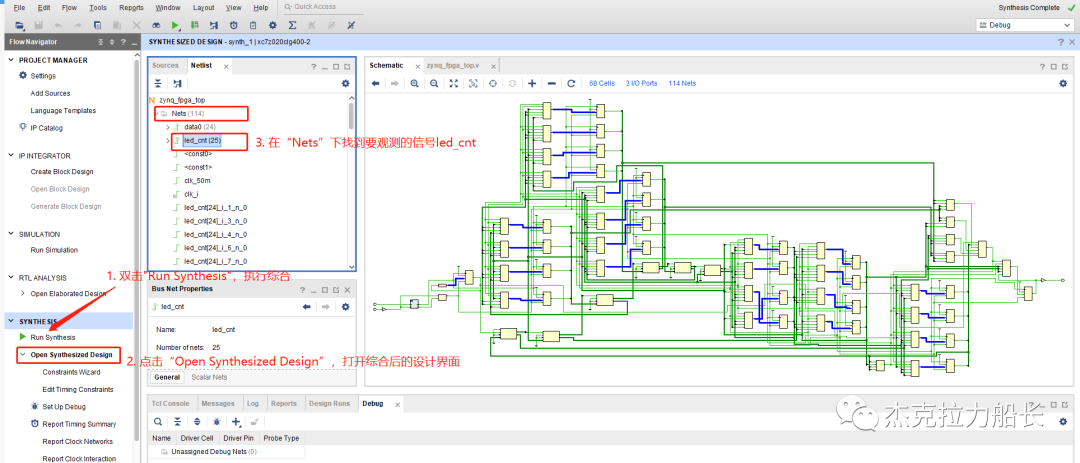

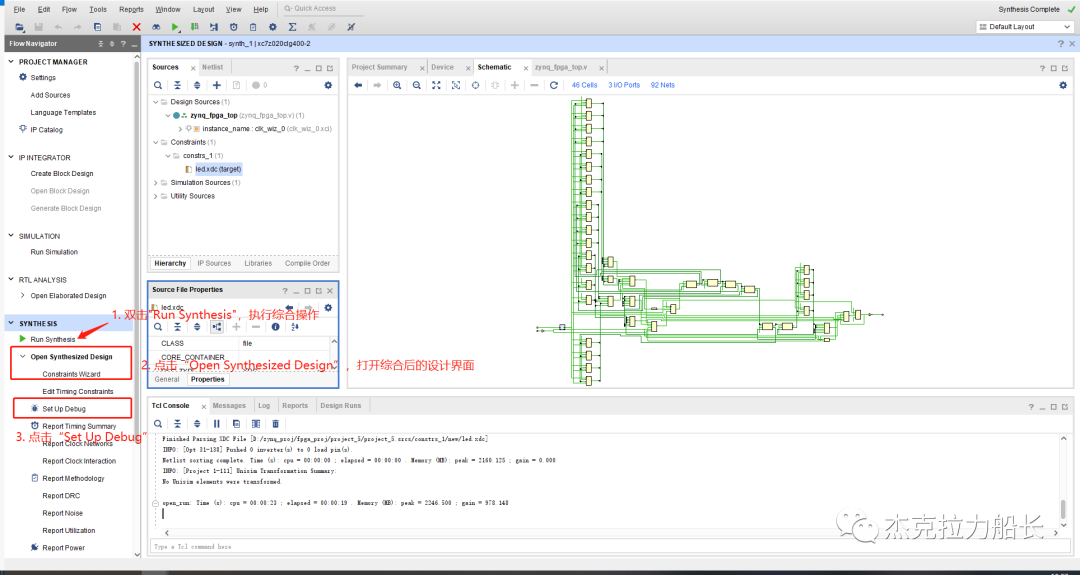

03 综合后添加Mark Debug

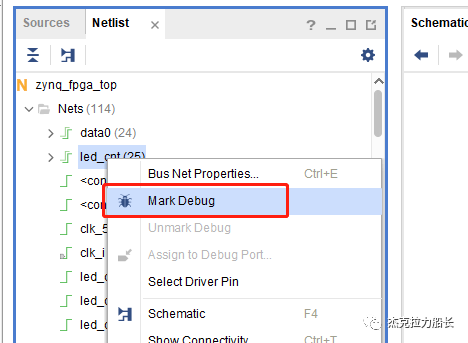

对工程执行综合,综合完成后,找到要观测的信号的Nets,右键选择“Mark Debug”;

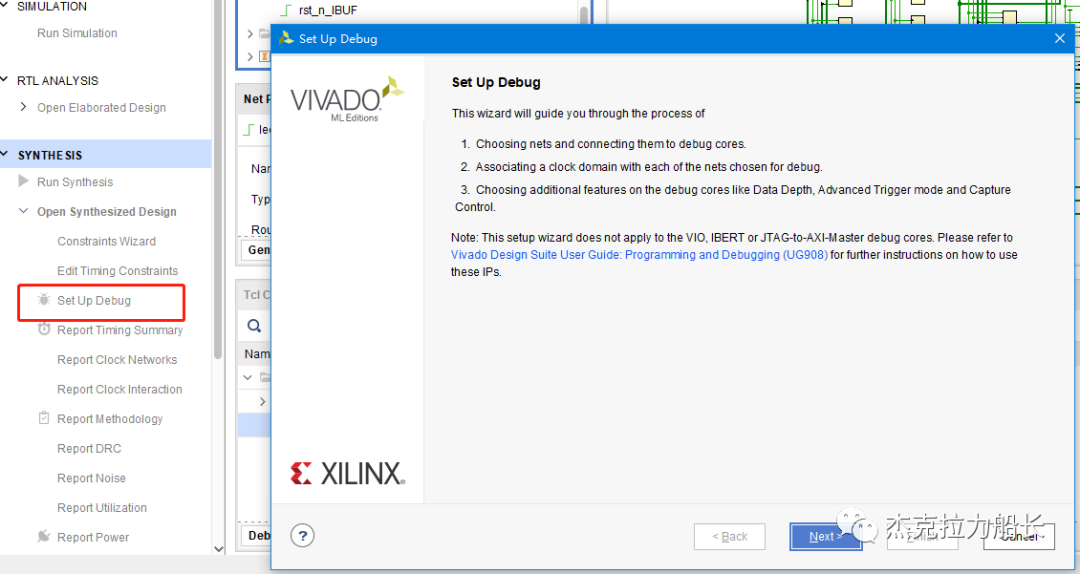

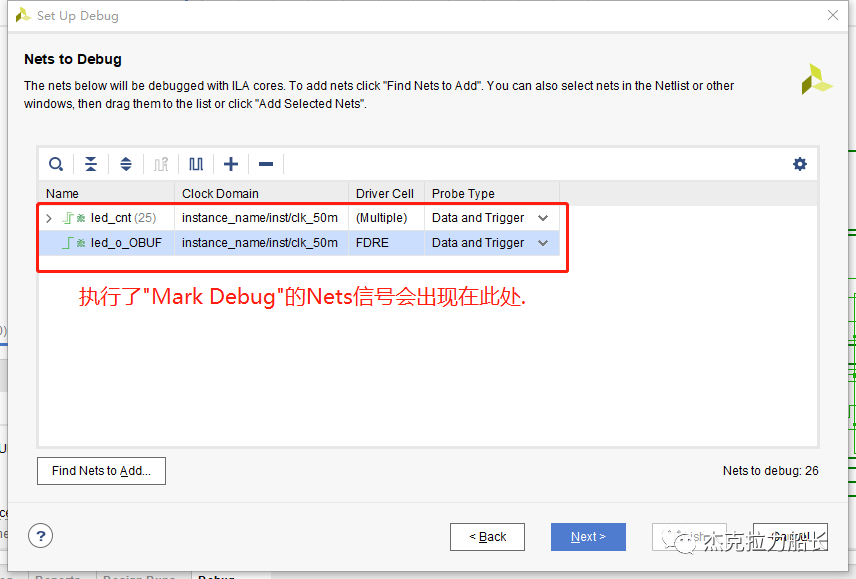

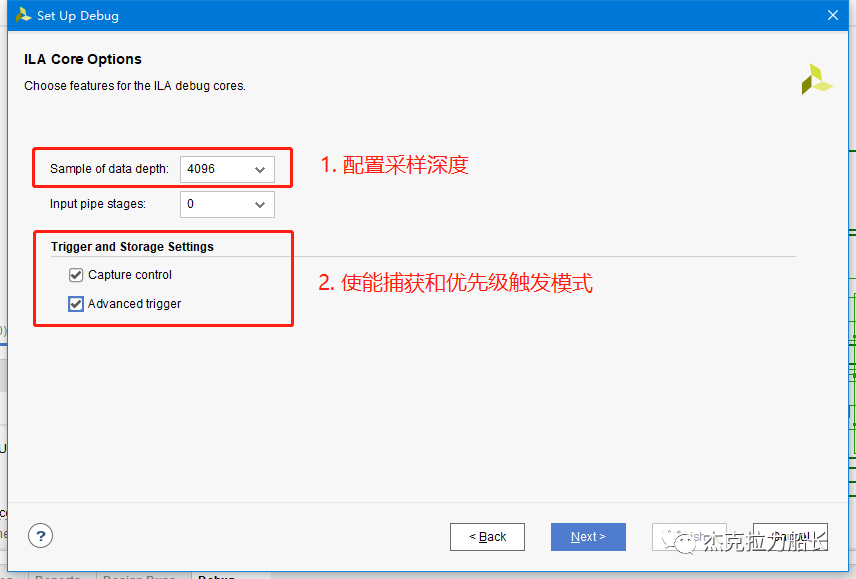

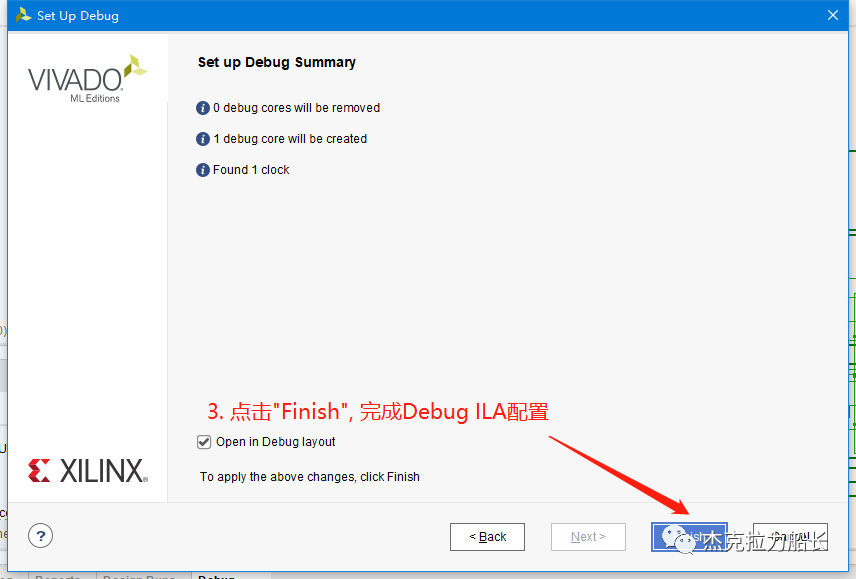

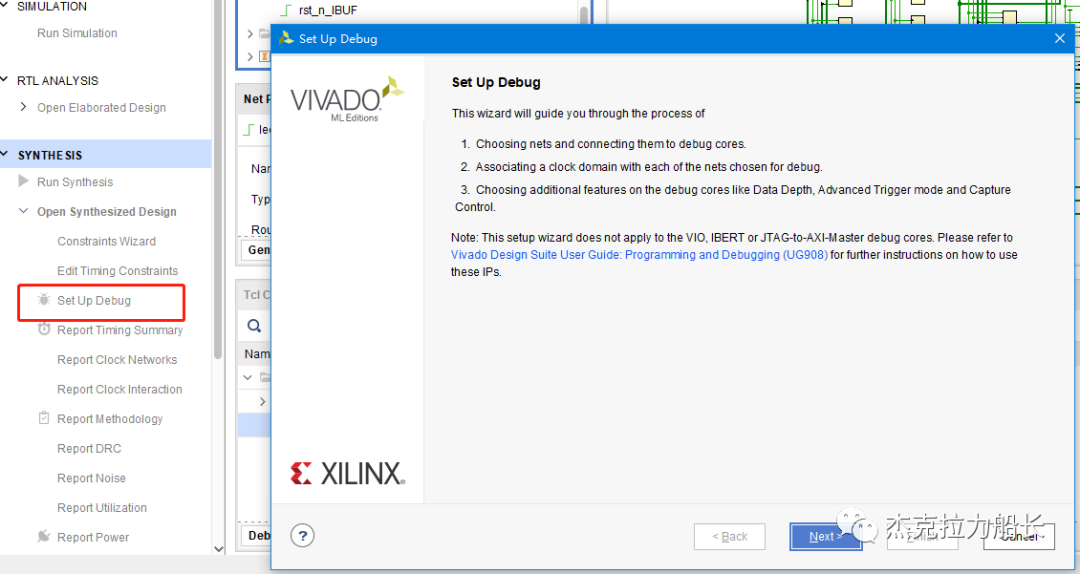

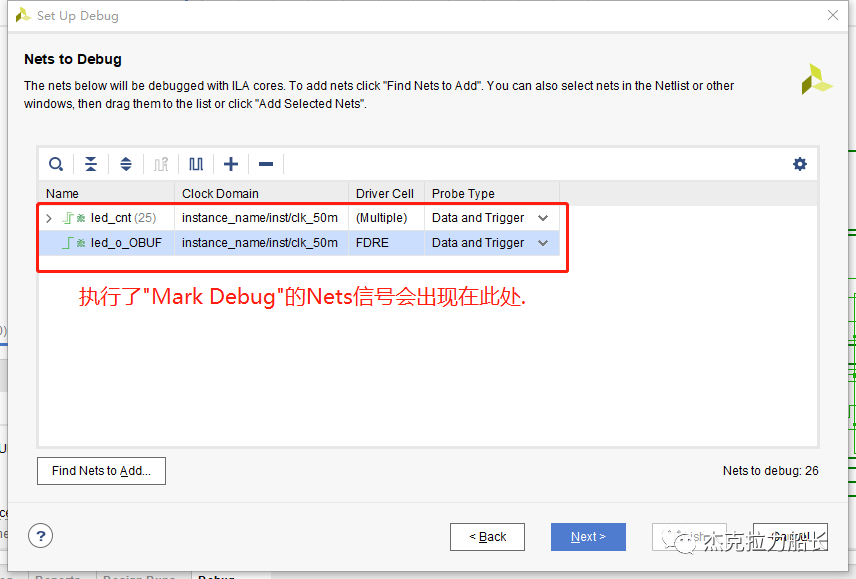

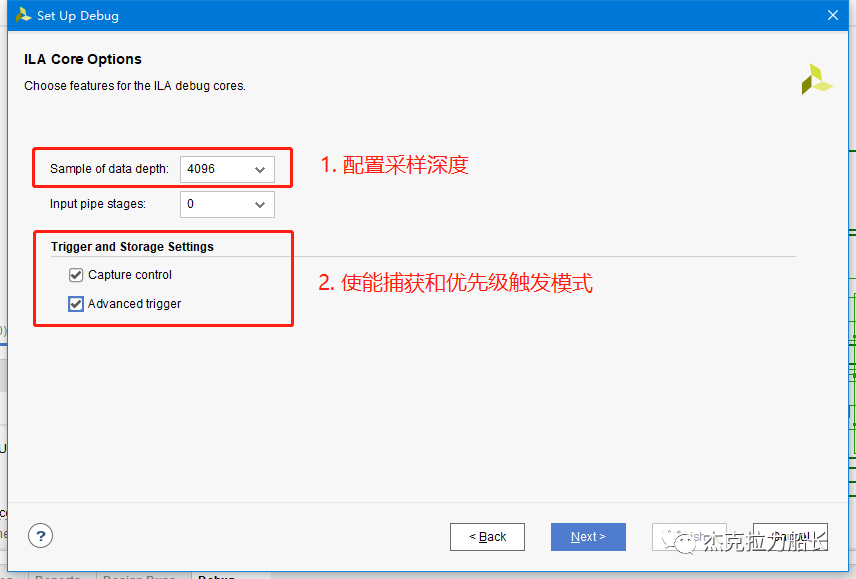

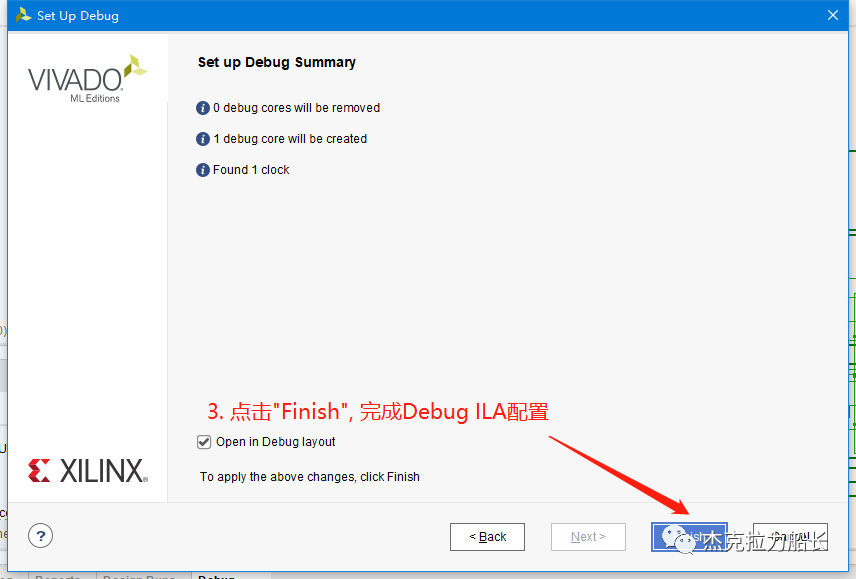

要观测信号的Nets选择并设置完成后,点击“Set Up Debug”;按照下面步骤配置Debug ILA参数;

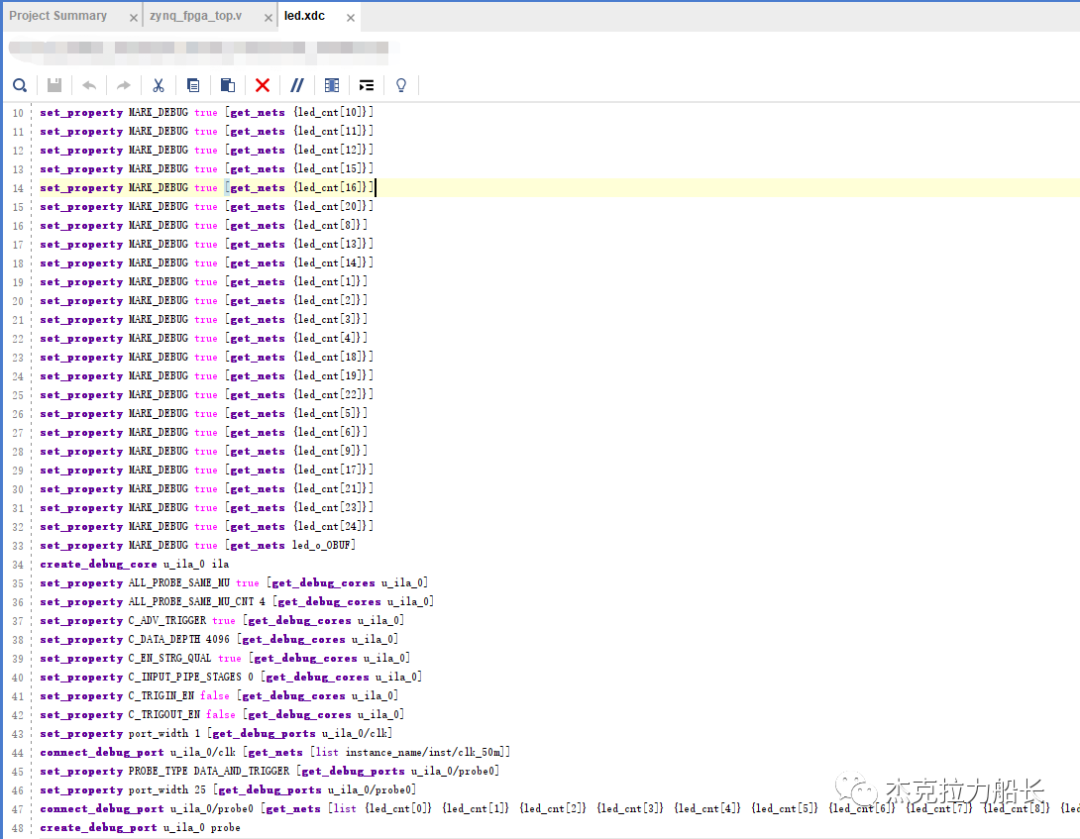

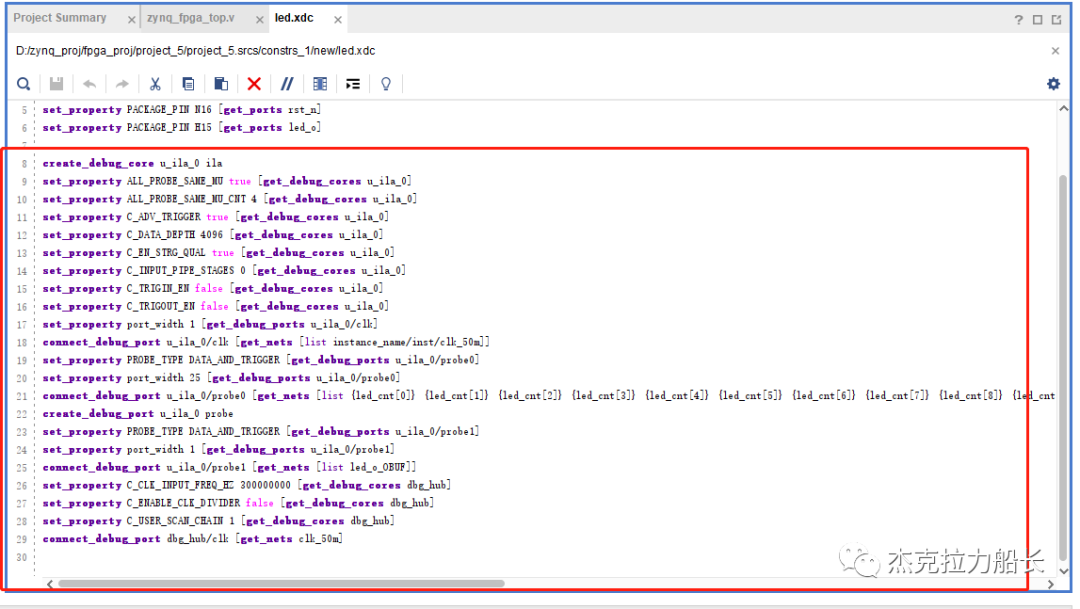

Debug ILA配置完成后,保存SYNTHESIZED DESIGN后会在约束文件(.xdc)中生成ILA的配置约束,如下图所示:

综合、实现、生成bit后写到FPGA芯片便可观测到信号(此处不做演示)。

特别说明:mark_debug仅可以对Nets类型进行操作,不能对Cells操作;

04 HDL中使用MARK_DEBUG

MARK_DEBUG描述

vivado设计IDE提供了一些属性供开发者使用,本篇推文主要是描述MARK_DEBUG属性约束的使用和注意事项。详细可参考UG912文档的内容。使用MARK_DEBUG的条件如下:

约束对象必须是Nets类型

在Nets信号的顶端声明处进行约束

vivado提供了包括Verilog、VHDL、XDC三种语法。三种语法如下所示:

//Verilog语法

约束语法:

(* MARK_DEBUG="value" *)

#value = true/flase

使用示例:

(* MARK_DEBUG="true" *) output wire led;

(* MARK_DEBUG="true" *) reg [24:0] led_cnt;

//VHDL语法

约束语法:

声明: attribute MARK_DEBUG : string;

语法: attribute MARK_DEBUG of signal_name : signal is "value";

//signal_name-内部信号, value = TRUE/FALSE

使用示例:

signal led : std_logic;

attribute MARK_DEBUG : string;

attribute MARK_DEBUG of led : signal is "TRUE";

//XDC语法

约束语法:

set_property MARK_DEBUG value [get_nets < net_name >]

#value = TRUE/FLASE

#net_name-是信号名

使用示例:

set_property MARK_DEBUG TURE [get_nets led];

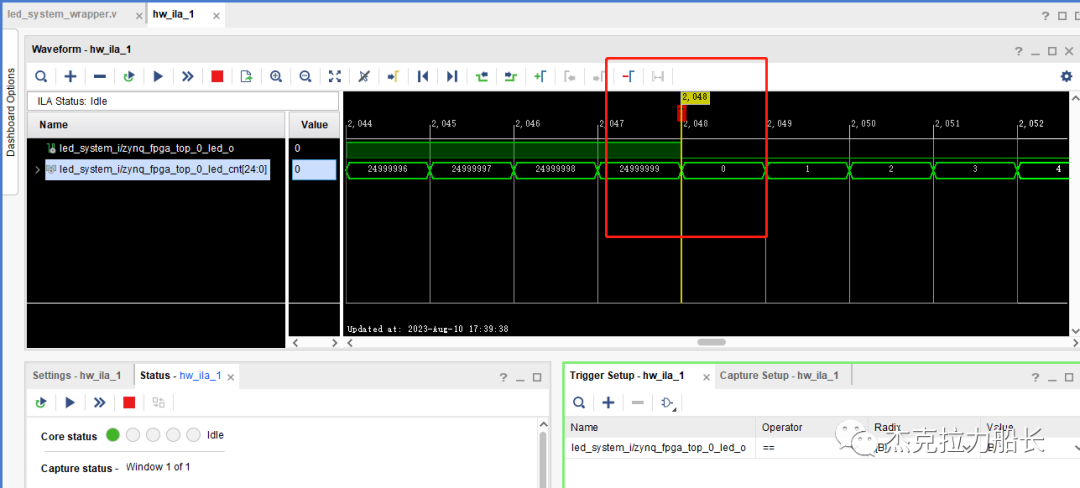

使用MARK_DEBUG标记生成ILA观测信号步骤

在led[0]、led_cnt[24:0]信号的顶端声明处进行约束,省略代码如下:

module led_top(

input wire clk_i,

input wire rst_n,

(* MARK_DEBUG="true" *) output wire led_o

)

;

...

(* MARK_DEBUG="true" *) reg [24:0] led_cnt;

...

endmodule

执行综合操作,综合完成后,打开综合设计,然后点击“Set Up Debug”;

按照下面步骤配置Debug ILA参数;

* Debug ILA配置完成后,保存SYNTHESIZED DESIGN后会在约束文件(.xdc)中生成ILA的配置约束,如下图所示:

* Debug ILA配置完成后,保存SYNTHESIZED DESIGN后会在约束文件(.xdc)中生成ILA的配置约束,如下图所示:

综合、实现、生成bit后写到FPGA芯片便可观测到信号(此处不做演示)。

特别说明:

MARK_DEBUG约束标记会阻止Vivado对该信号以及下级信号的优化。因此,在逻辑验证完成后,要删除Mark_DEBUG约束标记或者将其失能。

05 文章总结

上面总结和分享了4种Vivado下使用ILA的方法。杰克更推荐使用前面两种实例化的方法去使用ILA IP核。对于 纯FPGA HDL开发 ,配置生成ILA核并在HDL代码中实例化使用便可;对于带软核/硬核的FPGA开发 ,在Block模块外部接口信号通过添加ILA核,Block模块内部信号则在HDL代码中实例化ILA核,两者结合使用。

-

逻辑分析仪是干啥用的 逻辑分析仪的主要用途 逻辑分析仪的应用场景2023-09-19 5653

-

在Vivado中使用逻辑分析仪ILA的过程2023-06-29 8353

-

Vivado逻辑分析仪使用教程2023-04-17 1713

-

逻辑分析仪的计量说明2021-01-14 1465

-

Based逻辑分析仪的应用特点、优势及使用方法2020-10-28 1615

-

逻辑分析仪的作用_逻辑分析仪怎么用_逻辑分析仪的使用方法(教程)2017-12-20 55996

-

什么是逻辑分析仪?逻辑分析仪的使用方法是什么?逻辑分析仪和示波器有什么区别2017-05-09 7311

-

频谱分析仪的工作原理和使用方法2014-07-16 3966

-

SignalTapⅡ逻辑分析仪2013-03-07 8079

-

逻辑分析仪的使用2008-11-27 2936

全部0条评论

快来发表一下你的评论吧 !