RK3588 VDD_LOGIC电源PCB设计注意事项

描述

RK3588 VDD_LOGIC电源PCB设计

1、VDD_LOGIC的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚路径都足够。

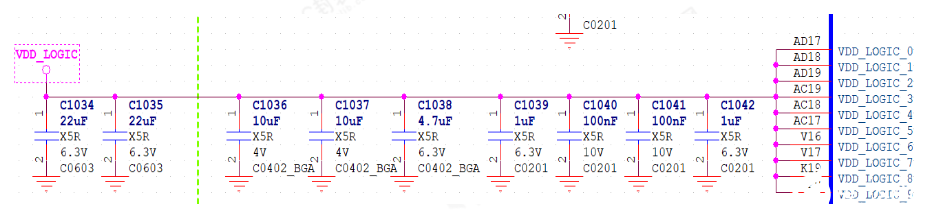

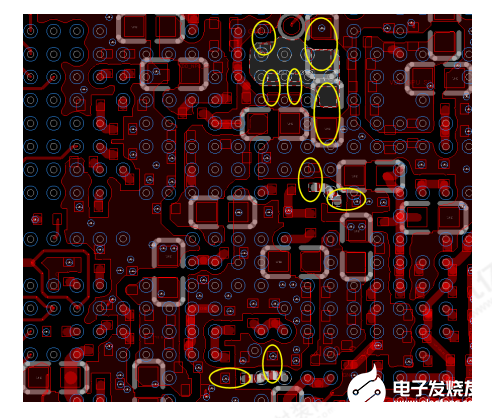

2、如图1所示,原理图上靠近RK3588的VDD_LOGIC电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND管脚尽量靠近芯片中心的GND管脚放置,如图2所示。其余的去耦电容尽量摆放在RK3588芯片附近,并摆放在电源分割来源的路径上。

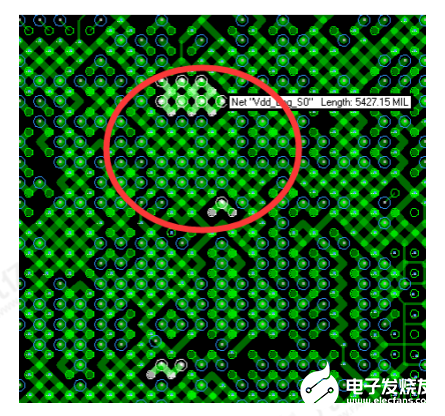

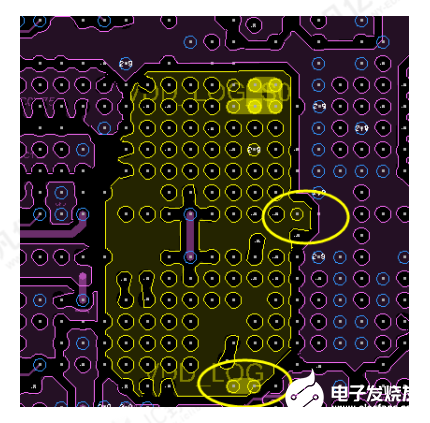

3、RK3588芯片VDD_LOGIC的电源管脚,每个管脚需要对应一个过孔,并且顶层走“井”字形,交叉连接,如图3所示,建议走线线宽10mil。

图1 RK3588 芯片VDD_LOGIC的原理图电源管脚去耦电容

图2 VDD_LOGIC背面去耦电容放置

图3 VDD_LOGIC“井”字形链接

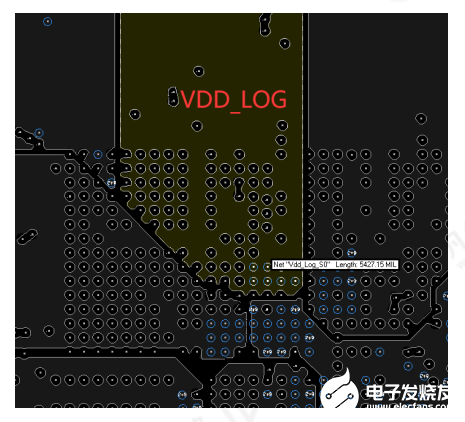

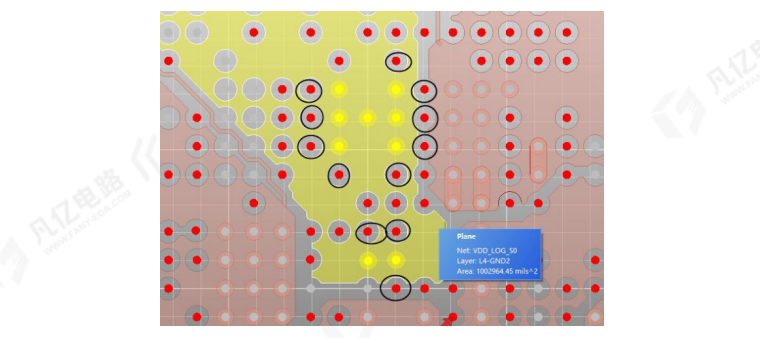

4、VDD_LOGIC电源在CPU区域线宽不得小于120mil,外围区域宽度不小于200mil,尽量采用覆铜方式,降低走线带来压降(其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜),如图4所示。

5、VDD_LOGIC的电源在外围换层时,要尽可能的多打电源过孔(8个以上10-20mil的过孔),降低换层过孔带来的压降;去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用,如图5所示。

图4 VDD_LOGIC电源层覆铜

图5 VDD_LOGIC芯片底下电源换层覆铜

6、电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧11个,如图6所示。

图6 LOGIC 电源地过孔放置图

-

迅为RK3588开发板Android系统烧写及注意事项2025-12-03 7373

-

RK3588 EVB开发板原理图讲解【八】 RK3588 power Tree2025-03-01 2300

-

RK3588S处理器硬件设计的要点及注意事项2024-05-23 1232

-

用这份PCB设计实战手册轻松搞定RK35882023-12-25 9788

-

VGA OUT 的PCB设计注意事项2023-11-23 1936

-

RK3588 VDD_CPU_LIT电源PCB设计2023-09-27 2193

-

RK3588 VDD_NPU电源PCB设计注意事项2023-09-26 1526

-

RK3588 VDD_CPU_BIG0/1 电源PCB设计注意事项2023-09-24 2401

-

RK806电源方案的PCB设计注意事项2023-09-23 2533

-

RK3588电源电路PCB设计方案2023-09-14 4132

-

RK3588 PCB推荐叠层及阻抗设计2023-08-10 2021

-

电源PCB设计汇总(上)2023-08-09 2123

-

【全是干货】《RK3588 PCB设计指导白皮书》线上发布&实战解读2023-05-08 7414

全部0条评论

快来发表一下你的评论吧 !