高速电路信号完整性学习笔记2

电子说

描述

高速数字设计和低速数字设计相比,高速数字设计强调无源电路元件的作用。一些无源元件包括构成数字产品的互连线,电路板,集成电路组件。在低速时,无源电路元件仅是产品包装的一部份。在高速时它们直接影响电路的性能。

高速数字化的设计研究的是无源电路元件怎样影响信号的传播(发射和接收),在信号间相互干扰(串扰) ,和电磁波在空间的相互作用(电磁干扰)。

1 时间和频率

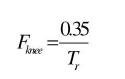

在低频时,普通电线可有效地将两电路短路。在高频时,仅有宽而平的物体能短路两个电路。相同的一根导线在低频情况下能有效地短路电路,而在高频时这根导线会产生太大的电感以至于它不能用来使电路短路。我们可以用它作为高频电感线圈但不能作为高频短路电路。任何数字信号的拐点频率与它的上升(和下降)时间有关,而与时钟频率无关:

Fknee=数字脉冲大部份能量集中在低于它的频段内;

Tr=脉冲上升时间;

上升时间越短, Fknee 越高;上升时间越长, Fknee 越低。任何数字信号的时域的重要特征主要由低于Fknee 的频谱决定。

当然拐点频率只是把数字信号的时间和频率联系起来,是一种近似估算的方法,它不能精确预料系统的性能,甚至不能精确测定上升的时间。它不能代替完备的边界分析,也不能预言电磁辐射,电磁辐射的性质取决于频率远远超过拐点频率的更详细的频谐。

2 时间和距离

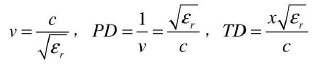

电信号在导线中或在电路中传导的速度与周围的介质有关。传播延迟通常用米/秒或英寸/皮秒来度量,它是传播速度的倒数。传输线的传播延迟按周围介质系数的平方根的比例增加。传输线的时间延迟仅指信号传播过整个线长所用的时间总量。以下等式表示了介电系数、传播速度、传播延迟和时间延迟之间的关系:

其中v为传播速度, C为光速, εr 为介电常数, X为传输线长度, PD为传输延时, TD为信号在传输线上传播X长度的时间。

布线的几何尺寸决定了电场是否留在电路板里或者进入到空气中。当电场存在于板子内部时,有效的电介常数要大一些,而且信号传播得更慢。密封在两平面间的布线周围的电场存留在电路板内,它产生一个有效的介电常数。

。印刷电路板顶层或底层布线的电场一部分存在于空气中,另一部分存在于FR-4 的材料中,巾此产生了大约1~4.5 的电介质常数。外层PCB 的布线传播速度比内层的要快。

3 集总系统与分布系统

任何导体系统对于输入信号的响应很大程度上取决于系统是否比信号中最快电特征的有效长度短, 或正好相反。电特性的有效长度就像上升沿一样,它取决于特征的持续时间和它的传播时延。

如果一系统的长度足够小使得所有的点有相同的电位,则这一系统被称为集总系统。集总系统中的每一部分的电压都大致相同。

一个系统被认为是集总系统或分布式系统取决于通过它的信号的上升时间。通常用系统尺寸和上升时间的比值来确定一个系统是集总系统还是分布系统。对于印刷电路板的导线,点对点导线和总线结构, 如果导线比上升沿有效长度的1/6 小, 则电路表现为集总系统。

4 SI基本概念

信号完整性( SI, Signal Integrity )主要讨论的是信号沿导线传输后的质量和时序问题。随着高速电路的迅速发展,信号完整性问题变得越来越突出,越来越引起关注。在高速系统中,一段导线不仅仅是导体,也己成为具有分布参数的传输线。能否处理好系统的信号互连( PCB布线),解决信号完整性问题,是系统设计成功的关键。同时, 信号完整性。也是解决电源完整性(PI) 、电磁兼容与电磁干扰( EMC/EMI ) 的基础和前提, 三者之间有着紧密的联系。通常,需要解决的信号完整性问题包括:

1)反射( reflection ) , 由于阻抗不匹配引起。

2)串扰( crosstalk ) , 由相邻信号稍合产生。当信号边缘速率低于lns 时,串扰问题就不可避免,甚至会引起高频谐振。

3)) 过冲( overshoot)和下冲( undershoot ),过冲与下冲来源于走线过长或者信号变化太快两方面的原因。

4)振铃( ringing ) ,表现为信号反复振荡,可以通过适当的端接来抑制。

5)地平面反弹噪声( ground bounce ) 与同时开关噪声(SSN ) 。对于高速器件,大量数据总线信号快速翻转,通过地回路的电流变化导致非理想的地平面。

6)电源分配。对于高速电路来说,控制好电源/地平面的阻抗是系统设计的关键。

7)时序问题。对于高速设计,信号的传播延时、时钟偏移( skew )和抖动等因素足以导致系统无法正确判断数据。

8)EMI 问题。EMI 包含电磁辐射和抗扰性两个方面的问题。解决PCB 设计中的EMI 问题是系统EMI 控制中最为重要的环节,成本最低。

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。差的信号完整性不是出某一单一因素导致的,而是板级设计中多种因素共同引起的。主要的信号完整性问题包括反射、振荡、地弹、串扰等。

-

高速电路中的信号完整性和电源完整性研究2024-09-25 486

-

高速电路信号完整性分析与设计—端接与拓扑2022-02-10 857

-

高速PCB电路板的信号完整性设计2017-11-08 1677

-

高速电路信号完整性2015-04-16 4237

-

高速信号的电源完整性分析2012-08-02 3612

-

高速电路信号完整性分析与设计—高速信号完整性的基本理论2012-05-25 2111

-

高速电路信号完整性设计培训2010-04-21 4177

-

高速电路信号完整性分析与设计—信号完整性仿真2009-09-12 44442

-

高速电路的信号完整性分析2008-10-15 1387

-

高速电路信号完整性分析之应用篇2006-05-28 1125

全部0条评论

快来发表一下你的评论吧 !