信号完整性学习笔记之CML

电子说

1.4w人已加入

描述

CML即Current Mode Logic,也就是电流模式逻辑,CML电路主要靠电流驱动,可以说CML是所有高速数据接口形式中最简单的一种,它的输入与输出是匹配好的,从而减少了外围器件,使用时直接连接就可以,基本上不需要在IC外面做匹配,此特点使单板硬件设计更简单,单板看起来更简洁,CML的摆幅较小,功耗比较低。

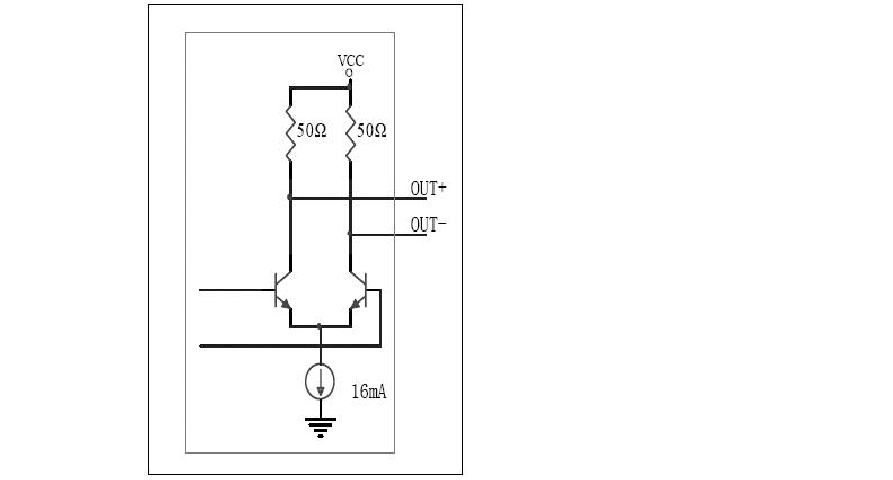

CML输出结构:

如上图所示,CML的输出电路形式是一个差分对,该差分对的集电极电阻为50ohm,输出信号的高低电平切换是靠共发射极差分对的开关控制的,差分对的发射极到地的恒流源典型值为16mA,假定CML的输出负载为一50ohm上拉电阻,则单端CML输出信号的摆幅为VCC~VCC-0.4V。

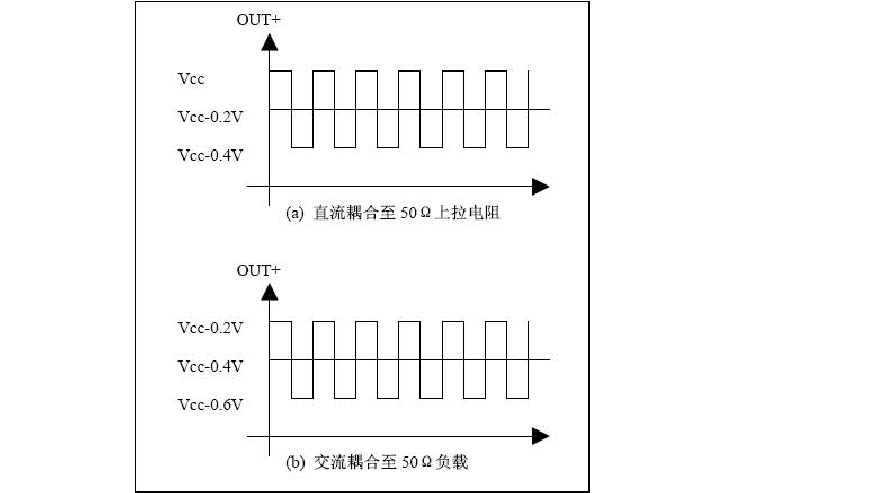

在这种情况下,差分输出信号摆幅为800mV,共模电压为VCC-0.2V。若CML输出采用交流耦合至50ohm 负载,这时的直流阻抗由集电极电阻决定,为50ohm,CML输出工模电压变为VCC-0.4V,差分信号摆幅仍为800mV。

CML波形:

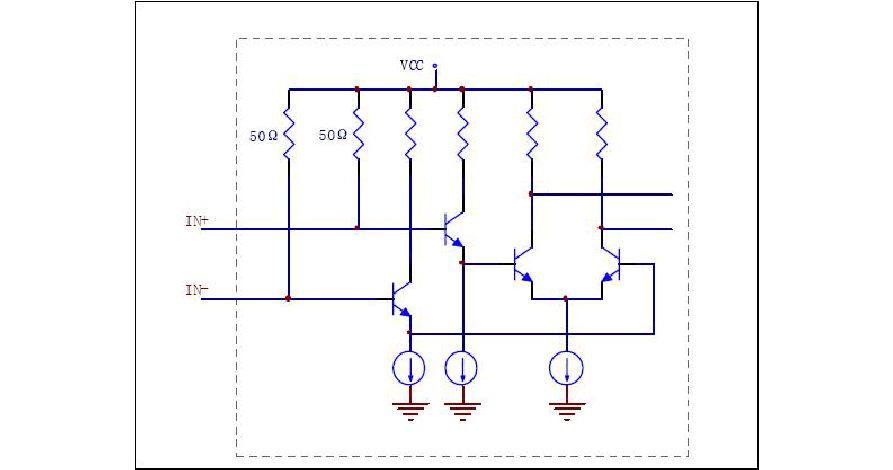

CML的输入一般都是片内匹配好的,50ohm上拉到VCC,而且大部分是交流耦合。

CML的输入结构:

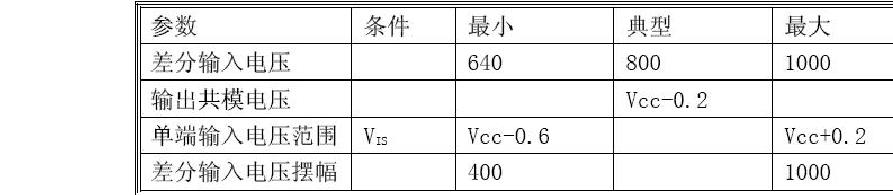

CML的摆幅一般在600mV-100mV之间,典型值为800mV。 CML逻辑参数:

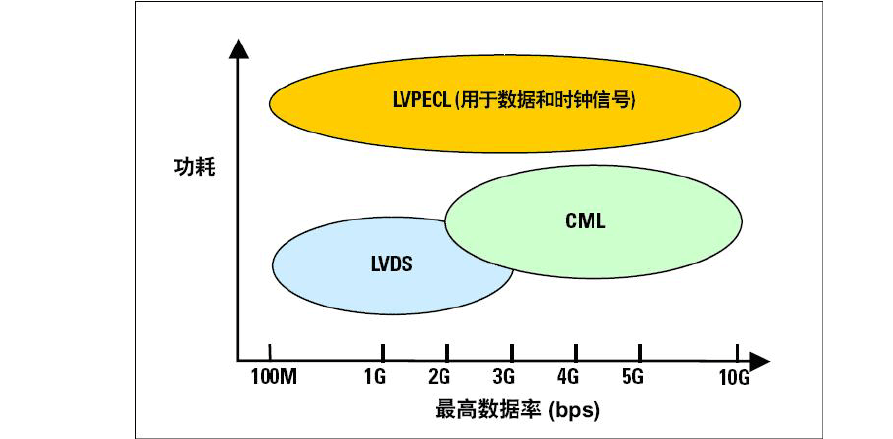

CML的优点是功耗低,速度高,但是驱动能力不如LVPECL,传输距离也没有ECL远。

LVPECL/LVDS/CML三种逻辑比较:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

信号完整性学习笔记2023-12-01 3837

-

何为信号完整性?信号完整性包含哪些2021-12-30 2872

-

高速电路信号完整性分析之应用篇2006-05-28 1125

-

信号完整性原理分析2009-11-04 1287

-

什么是信号完整性2009-06-30 5874

-

信号完整性与电源完整性仿真分析2011-11-30 2109

-

电地完整性、信号完整性分析导论2016-02-22 1357

-

信号完整性与电源完整性的仿真分析与设计2016-12-14 2137

-

信号完整性设计中的5类典型问题(于博士信号完整性)2017-01-22 1244

-

信号完整性系列之信号完整性简介2021-01-20 2588

-

信号完整性系列之“信号完整性简介”2021-01-23 2599

-

信号完整性与电源完整性的仿真2021-09-29 1646

-

信号完整性分析科普2023-08-17 9236

-

信号完整性与电源完整性-电源完整性分析2024-08-12 3274

-

听懂什么是信号完整性2024-12-15 1385

全部0条评论

快来发表一下你的评论吧 !