双端输入单端输出CMOS运放设计实例

模拟技术

描述

双端输入单端输出CMOS运放设计实例

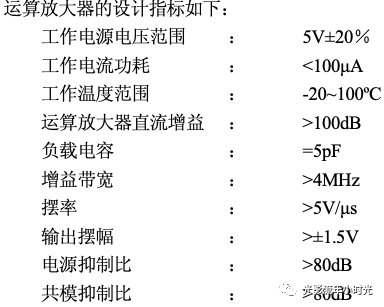

1.运算放大器性能指标

2.性能指标到电路参数指标之间的转化和分析

(1)直流增益和电路结构

由于设计的运算放大器的电压增益在 100dB 以上,因此通过前面各种电路结构的分析, 可以选择折叠式共源共栅电路和一个简单放大器级联的结构来设计所需的电路。这样可以保证在较高的增益下,保证其他参数的实现。电路结构如图6- 19所示。

(2)频率补偿,相位裕度和补偿电容大小安排

在两级放大器级联运放结构中,在两级放大器的输出端都有可能产生较低频的极点,因此需要频率补偿。通常频率补偿的方式是采用米勒补偿或带调零点电阻的米勒补偿。

(3)摆率 SR>5V/μs

所谓摆率是指各级电路对其负载电容的最大驱动能力。对于第一级放大器:

考虑到过小的电流导致如果需要得到较大的 gm 时,需要更大的 MOS 管宽长比值。我们由此可以将指标规定的100μA 电流分配到两级放大器中,一种比较合理的分配方法是第一级放大器分配 40μA,第二级放大器分配40μA,剩下20μA 作为余量备用。在第一级放大器中,分配给 M1,M2 差分对管各10μA 电流,M7~M12 管各10μA 电流,M4, M5 电流源分配20μA电流。

(4)共源共栅(Cascade)管和电流镜管的宽长比计算

(5)偏置电路的设计

放大器主电路的设计,但是并没有说明共源共栅管和电流镜的栅端偏置电压从何而来。在实际设计中往往是给一个模块电路提供一个由带隙基准(Bandgap Reference)产生的电流,或者由经过温度补偿的稳定的电流源电路提供的一个电流,并由 该模块自身产生各管的偏置电压。

在上面的计算过程中,使用了大量的理想条件和简单计算,很显然在实际的设计中还需要对电路的参数优化,同时要严格考虑版图的匹配性。在完成基本计算后,我们可以通过 Cadence 软件进行仿真验证。

-

如何使用THS4531A运放实现交流信号的单端转差分输出?2024-08-15 1157

-

集成运放的一输入端悬空,对输出有什么影响?2024-08-29 1509

-

有没有合适的带宽能达到20M,满足差分输入单端输出的运放呢?2024-08-30 609

-

是否可以直接通过双运放简单缓冲输出单端到PCM1804?2024-09-27 310

-

LM358双运放前级放大输入端IN离运放较远2019-03-20 2869

-

请问运放的单端输入电压范围与共模输入电压范围该怎么理解?2019-06-11 6331

-

运放是差分信号输入单端信号输出?运放有什么用呢?2023-04-25 1434

-

运放输出端的保护电路图2009-07-17 3110

-

差分放大电路单端输出和双端输出区别以及应用2017-11-18 201250

-

应用于电机驱动的隔离运放单端和差分输出对采样性能的影响2022-10-31 889

-

运放的同相输入端和反相输入端之间的电阻怎样设置?2023-10-26 8608

-

差分放大电路中,单端输入和双端输入两种输出值是否相同?为什么呢?2023-11-20 7019

-

单端输入和双端输入的区别是什么2024-07-31 6650

-

放大器单端双端输出的区别2024-10-08 4966

全部0条评论

快来发表一下你的评论吧 !