流水线ADC的内部结构和工作原理是什么

描述

点击上方蓝字关注我们

低采样速率ADC仍然采用逐次逼近(SAR)、积分型结构以及最近推出的过采样ΣΔADC,而高采样速率(几百MSPS以上)大多用闪速ADC及其各种变型电路。然而,最近几年各种各样的流水线ADC已经在速度、分辨率、动态性能和功耗方面有了很大的提高。对于几Msps到100Msps的8位高速和16位低速模数转换器(ADC),流水线已经成为最流行的模数转换器结构,它可以涵盖很广的应用范围,包括CCD成像、超声成像、数字接收、基站、数字视频(如HDTV)、xDSL、线缆调制解调器以及快速以太网。本文介绍了流水线ADC的内部结构和工作原理。

一、流水线ADC结构

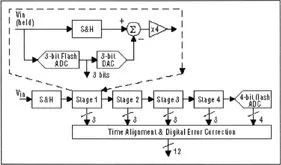

图1为12位流水线ADC的结构图。输入Vin首先被采样/保持(S&H)电路所采样,同时第一级的闪速ADC把它量化为3位,此3位输出送给一3位的DAC(具有12位精度),输入信号减去此DAC的输出,放大4倍送给下一级(第二级),继续重复上述过程,每级提供3位,直到最后一级4位闪速ADC。对应某一次采样,由于每级在不同的时间得到变换结果,因此在进行数字误差校正前用移位寄存器对各级的结果先按时间对准。注意只要某一级完成了某一采样的变换,得到结果并把差值送给下一级,它就可以处理下一个采样。因此流水线操作提高了处理能力。

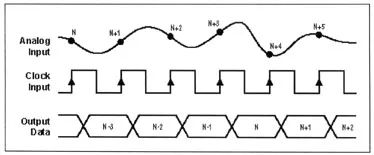

1. 延迟时间

由于每个采样必须通过整个流水线才能得到数字误差校正所需的各个位,因此流水线ADC有数据延迟。在图1的例子中,大约要延时3个周期(见图2)。

2. 数字误差校正

大多数现代流水线ADC采用“数字误差校正”技术来大大降低对闪速ADC(即内部的每个比较器)的精度要求。图1中,3位的差值输出其动态范围是输入信号Vin的1/8,然而随后的增益只有4,因此给第二级的输入只有第二级ADC 3位范围的一半(在第一级的3位变换没有误差的情况下)。

如果第一级的3位闪速ADC的某一个比较器有很大的失调,同时输入电压又正处于此比较点上,那么就会产生不正确3位码和不正确的3位DAC输出,此时产生了不同的差值。可以证明,只要放大后的差值没有超出后续的3位ADC的范围,以后产生的LSB码加上前面不正确的3位MSB码同样能产生正确的ADC结果。实际上,四级流水线中的第一级3位闪速ADC只需4位的精度。数字误差校正不能修正最后4位闪速转换器产生的误差。但是,这里产生的任何误差要除以前面的累积增益(44),因此只要求最后一级的精度大于4位。

在图1的例子中,虽然每级产生3位,但由于级间的增益是4,每级(第一级至第四级)的有效分辨率为2位。额外的位只是用于使尾数减半,使下一级3位ADC有额外的范围进行数字校正。这种方法被称之为级间“1位重叠”。因此整个ADC的有效位数是2+2+2+2+4=12位。

3. 元件精度

数字校正不能修正每个DAC和增益放大器的增益和线性特性。特别是前端的采样保持电路,DAC需要12位的精度。但是随后各级的元件只需较低的精度(如,第二级10位精度,第三级8位,等等),因为他们的误差要除以前面的级间增益。通常利用这一事实把流水线逐级做小来进一步降低功耗。

在大多数采用CMOS和BiCMOS技术的流水线ADC中,采样/保持、DAC、加法器和增益放大器通常用乘法DAC(MDAC)的单开关电容电路来实现。限制MDAC精度的主要因素是内在的电容不匹配。纯双极型实现方法更加复杂,主要受电流源DAC和级间增益放大器中电阻不匹配影响。通常12位或更高精度都需要阻容修正和数字校正,特别是第一级。

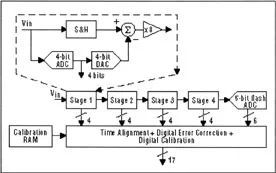

4. 数字标定

MAX1200/MAX1201/MAX1205系列(16位1Msps、14位1Msps和2Msps ADC)采用数字标定来保证其优越的精度和动态性能。MAX1200系列是CMOS流水线ADC,它由四级4位(其中一位重叠)和最后的5位闪速ADC构成,总位数是3+3+3+3+5=17位(参见图3)。额外的1到3位是数字标定用来量化误差项来达到更高的精度,舍掉它们后,最后得到14位或16位的精度。

标定从第三级的MDAC开始。第三级以上的MDAC误差已经足够小,不必标定。第三级的输出经剩余的流水线ADC数字化后,误差项存入片内的RAM中,第三级标定后,就可以用同样的方式由第三级来标定第二级,同样,第二级标定后,再标定第一级。为了使标定免受噪声的影响,采用取平均的方法(特别是第一和第二级的MDAC)。在正常转换期间,从RAM中取出标定的误差项来调整数字误差校正后的输出结果。

二、各种变型电路

从图1可以看出:根据每级的分辨率多少、最后闪速ADC的位数、是否采用数字标定和修正来提高最初几级的精度可以衍生出各种各样的流水线ADC。采样速率和分辨率部分地决定了每级采用的位数。通常,高速CMOS流水线ADC每级一般用于低位数(甚至每级只有一位,级间增益只有2),原因是CMOS比较难实现很高增益的宽带放大器。低采样速率的CMOS流水线ADC和双极型流水线ADC(即使采样速率很高)每级常采用多位数,这同时也带来了更小的数据延迟。

CMOS MAX1425/MAX1426 (10位10Msps和20Msps)系列使用流行的每级1.5位结构,每级只有1位分辨率和“0.5位重叠”,每级有一个1.5位的闪速ADC(只有2个比较器)。可以证明,利用数字误差校准,可以达到2位闪速ADC和DAC的标准MDAC同样的效果,这些转换器以20Msps速率采样10MHz输入信号时可以达到高达59dB的SNR。

MAX1444/MAX1446/MAX1448/MAX1449系列(10位40/60/80/105Msps)是最新的采用每级1.5位结构的高速甚低功耗10位ADC。它们组合了宽带低失真采样保持放大器,在整个奈奎斯特频率内以及高于奈奎斯特频率内保证了卓越的动态性能。该系列产品可用于数字接收机中的欠采样设计。

三、流水线ADC和其它ADC的比较

1. 与逐次逼近型比较

在逐次逼近(SAR)ADC中,用一个高速高精度比较器将模拟输入和前一次得到的模数转换结果通过DAC后的输出相比较,依次得到MSB到LSB的每一位,逐渐逼近输入模拟信号。SAR的这一串行工作方式从本质上限制了它的工作速度,最高约为几Msps左右,对更高的分辨率(14到16位)速度就更低。流水线ADC则不同,它是并行结构,各级同时以逐次方式得到1位或几位。虽然SAR中只需一个比较器,但是这个比较器必须高速工作(速率约为总位数×采样速率),其精度必须与ADC本身一样高,相反,流水线ADC内的比较器则不需要这一速度和精度。

当然,流水线ADC通常比相同位数的SAR占据更多的硅片面积。SAR只需一周期的延迟时间(=1/Fsample)就得到结果,而流水线ADC需要3或更多周期的延迟。与流水线ADC一样,12位精度以上的SAR也需要某些形式的校正和标定。

2. 与闪速型比较

尽管流水线ADC是并行机制,但它还需要DAC的精密转换和级间增益放大,因此存在建立时间问题。纯闪速型ADC不同,它有大量的比较器,每个比较器由宽带,低增益前置放大和锁存器构成。该前置放大器不像流水线ADC中的放大器,它只需提供增益,不需要线性和精度,只是比较器的触发点要很精确。因此流水线ADC速度根本比不上设计得很好的闪速型ADC.

虽然超高速8位闪速ADC(及各种合并/插值变体)的采样速率高达1.5Gsps(比如MAX104/MAX106/MAX108),但是很难找到10位的闪速ADC,特别是12位及高于12位的ADC还没有商用化。这是因为闪速ADC分辨率每增加1位,比较器数量就增加1倍,同时每个比较器的精度必须增加1倍。流水线ADC则不同,它的复杂性随分辨率线性增加,不是指数增加。

在相同的采样速率下,流水线ADC比闪速ADC消耗功率少得多。流水线ADC不易受比较器亚稳态的影响。闪速ADC中的比较器亚稳态会导致火花码错误(即ADC输出不可预测、不稳定结果的情况)。

3. 与Σ-Δ型比较

过采样/Σ-Δ型ADC多用于带宽限于22KHz以内的数字音响中。但是最近一些Σ-Δ型转换器已经在12到16位的分辨率下达到了1至2MHz的带宽。它们通常是高阶的Σ-Δ调制器(比如4阶或更高),同一个多位的ADC和多位的DAC一起工作,主要应用于ADSL。Σ-Δ型转换器无需校正/标定,即使是16到18位分辨率,也不需要模拟输入前的陡峭滚降的抗混叠滤波器,因为它的采样频率远远高于有效带宽,它由后端的数字滤波器来处理混叠问题。Σ-Δ型转换器的过采样本质还把模拟输入中的任何系统噪声“平均滤除”。

但是Σ-Δ型转换器是以牺牲速度换取分辨率的。每输出一次采样结果都需要对输入采样很多次(比如至少16次,甚至更多),这就需要Σ-Δ调制器中模拟元件的工作速率要比最终数据输出速率快很多。数字滤波器的设计比较繁琐,另外,它也占据了一些硅片面积。目前,最快的高分辨率Σ-Δ型转换器还达不到几MHz的带宽。像流水线ADC一样,Σ-Δ型转换器也有延迟。

四、结论

流水线ADC结构适合于几Msps到100Msps采样速率,其复杂性随分辨率的增加只是线性(而不是指数)增加,具有高速、高精度和低功耗特性,适用于各种场合,特别是数字通讯领域,在这些领域中转换器的动态性能经常比微分非线性(DNL)和积分非线性等传统的ADC特性更重要。在大多数的应用中,流水线ADC的数据延迟都无关紧要。

MAXIM一直致力于发展新型转换器来增强其流水线ADC业务,包括马上就要公布的高性能的12位20/40/60Msps转换器MAX1420/MAX1421/MAX1422。MAXIM的流水线ADC使整个MAXIM的ADC系列更加丰富和完整。

有你想看的精彩 至芯科技FPGA就业培训班——助你步入成功之路、9月23号北京中心开课、欢迎咨询! 解析高速ADC和DAC与FPGA的配合使用 基于FPGA的图像实时处理系统设计

扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

原文标题:流水线ADC的内部结构和工作原理是什么

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- FPGA

-

流水线ADC结构解析 流水线ADC和其它ADC的比较2023-09-26 2757

-

什么是流水线 Jenkins的流水线详解2023-05-17 1774

-

了解流水线型ADC2023-02-25 7220

-

科普下CPU流水线的工作原理2021-12-15 2404

-

各种流水线特点及常见流水线设计方式2021-07-05 10063

-

如何设计一种适用于流水线ADC的运算放大器?2021-04-22 1581

-

CEA技术的原理特点及在流水线ADC中的应用2019-05-17 4918

-

一种改进运放共享结构的11位流水线ADC设计2017-01-07 750

-

基于VHDL_AMS的流水线ADC结构式建模方法与仿真2017-01-03 1016

-

流水线ADC的行为级仿真2012-04-05 1013

-

什么是流水线技术2010-02-04 4408

-

周期精确的流水线仿真模型2009-12-31 1398

-

流水线ADC2009-02-08 10547

-

一种流水线结构AD转换器的速度分析方法2008-12-03 876

全部0条评论

快来发表一下你的评论吧 !