电源设计—差模滤波原理

电源/新能源

描述

一 前言

电源基本是每个电子电路的核心部分之一,怎么做好一个电源的EMC设计,却是一个能困扰大部分硬件工程师很长时间的难题。一般的BUCK电路中,芯片的工作频率都会在几十KHz到几MHz,而这也是BUCK电路产生EMI问题的关键。(本文主要以BUCK电路为模型来分析差模滤波该怎么去设计!干货满满,请耐心看完,收获不浅)

二 差模滤波原理

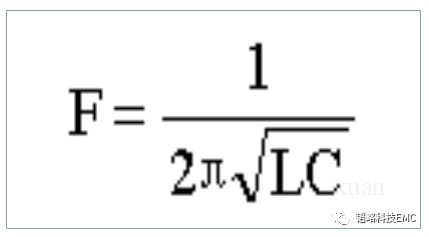

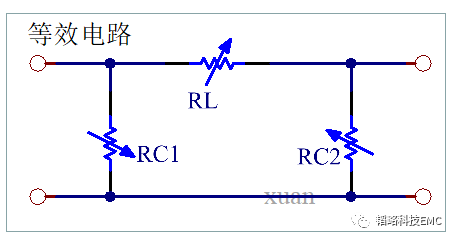

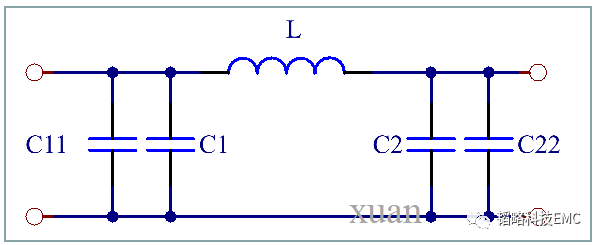

能实现差模滤波的电路有很多,这里就以L式“π型滤波电路”为例进行分析;此差模电路为什么能实现滤波的原因:若L为1uH,(即10^-6);C为1uF,则F约为159KHz。

串联滤波器件选择L是因为(XL=2πfL)电感通低频阻高频,BUCK电路的输入一般都是直流,频率较低,而BUCK电路自身的开关频率在整个频域上不是特别高,但是对于电感L来讲,是比较高的一个频率,能使得L在几十KHZ到几MHz下,呈现为一个高阻状态;反之,电容通高频阻低频,在这个频率范围下,电容会呈现一个低阻状态。

三 参数设计

因为此电路是一个低通滤波器,电感是串联器件,对于电流的大小比较敏感,而电感的通流能力越大,线径就需要越粗,因此在设计差模滤波电路的时候,建议先确定合适的L,再去计算合适的电容C。

这里计算LC的振荡频率的时候,不能直接让F=1/2π√LC等于BUCK电路的开关频率!一是因为振荡频率在这么高的频率不仅没有滤除原来的噪声,甚至滤波电路自身还会成为噪声源;二是因为我们测试频率是从几百KHz到几GHz,为了让滤波能力最大化,所以LC电路的频率需要“小于”电路的开关频率!

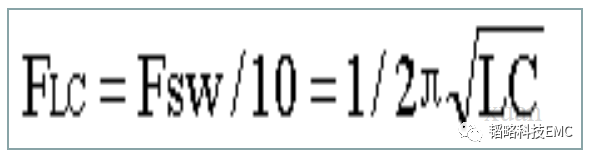

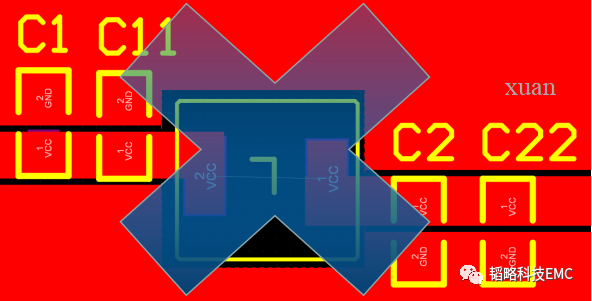

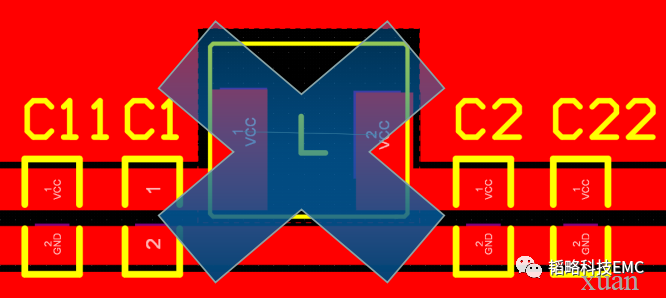

为了让电源输出的纹波比较稳定的同时,电源前端的LC滤波效果最大化,有关资料会推荐将LC的谐振频率取BUCK开关频率1/10来计算,因此计算L与C参数的时候,其计算公式与常规的算法上略有不同为“FLC=FSW/10=1/2π√LC”一般在此基础上,还对此滤波电路的滤波做加强,也就是在外围再加一对匹配电容,此电容为LC里的4倍容值大小(C11=4C1,C22=4C2)。

四 电路设计

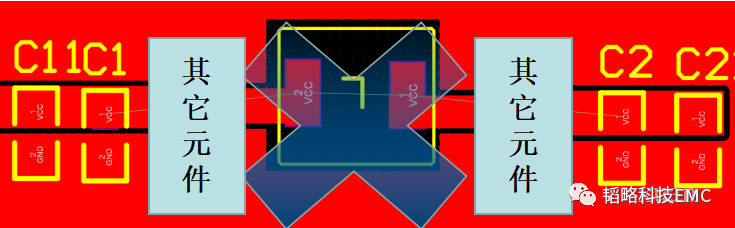

前面描述了那么多,但是最关键的地方还是在PCB的Layout上面,布局不合理,有时候怎么调整都不会有明显的变化:

1.滤波不供地,左右电容的GND被迫分离,滤波效果不理想;

2.模块不紧凑,布局导致模块电路被迫分散,滤波效果不理想;

3.分地不彻底,后级GND绕过滤波电路回前级,滤波效果不理想;

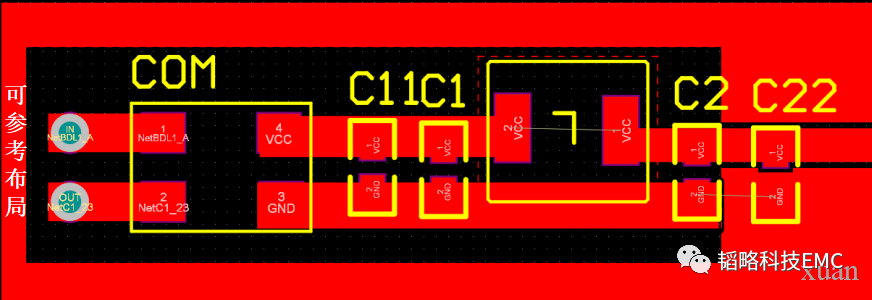

想要让电源的EMI测试顺利,且测试数据漂亮,在Layout上不能少花时间。下图为一个实际测试,EMI效果良好的PCB布局,前端共模起抑制与隔离效果,因此共模底部与周边不可以放置铜皮;而差模滤波电路为例确保噪声的滤波效果最大化,放置GND的铜皮位置(也就是GND铺铜网络),选择在差模滤波后端,靠近电源芯片处,且前端布局不要让铜皮离滤波电路过近,这个位置的滤波电感最好选择屏蔽电感,可进一步优化滤波效果。

(此图为参考与推荐布局,实际布局还需自行根据结构、器件大小等其他因素来调整布局。)

五 实际案例

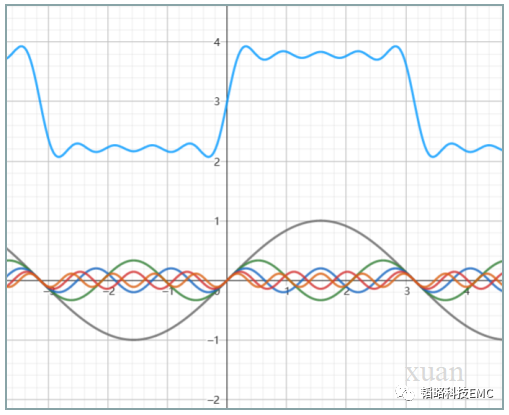

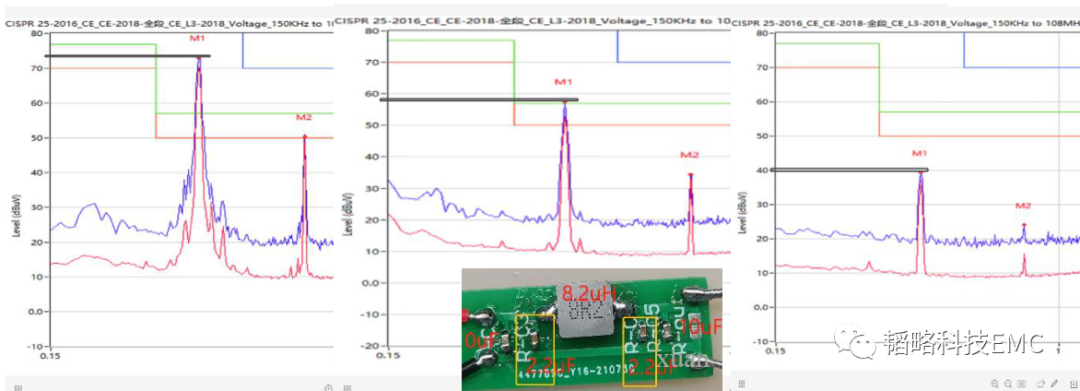

这是某个车载客户在测试VCE的时候,发现BUCK电路的400KHz频率超标,由于客户板内PCB没有差模滤波电路,所以飞了一个DEMO板来测试,最左侧数据是没有加措施的在75dB的位置;中间数据是加了一个8.2uH电感、左右各并一个2.2uF电容的测试数据,在58dB的位置;最右侧的数据是在上一个措施上再在左右两侧弥补一个10uF电容,在40dB的位置,测试得出的效果!

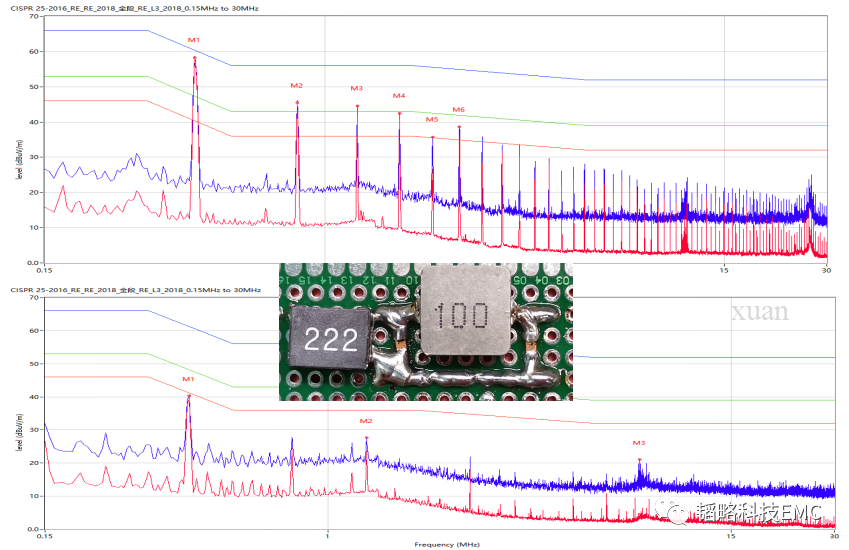

这是另一个车载客户在测试RE单极子天线的时候,发现测试BUCK电路的频率整体都比较高,这个电源芯片的工作频率也是400KHz,因为电源模块是客户外购的,电路部分当时不方便整改,也是在外围飞的DEMO板进行测试!

六 总结

电源EMI设计,这些滤波电路你在测试的时候,可以用不上或者用不着,但是不能没有,不然后期测试想调整的时候,没有位置也没有空间。此外,在考虑电源PCB布局的时候,一定要规划好电源的回路,不能给电源的回路过于开放,导致噪声路径不可控!

审核编辑:刘清

-

电源滤波器的差模抑制能力会受哪些因素影响2025-01-09 687

-

电源滤波器是如何对共模和差模干扰进行滤波的?2024-12-05 2078

-

电源滤波器共模和差模的滤波效果2024-11-29 2745

-

开关电源差模传导发射分析2024-01-22 2735

-

请问AC220V与直流电源的滤波究竟是采用共模滤波还是差模滤波?2019-08-13 3506

-

大电流共模滤波器——差共模滤波器2018-05-16 26157

-

基于差共模滤波器滤波电感集成的研究2009-10-14 1067

-

共模和差模信号与滤波器2009-07-10 7912

-

差模滤波器电路图-原理图2009-03-29 9582

全部0条评论

快来发表一下你的评论吧 !