DDR3带宽的计算方法

存储技术

描述

1. 前言

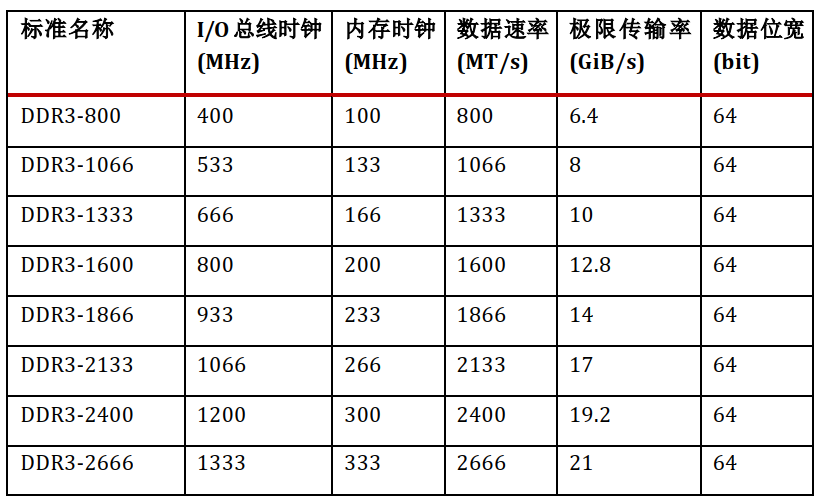

我们在买DDR内存条的时候,经常会看到这样的标签DDR3-1066、DDR3-2400等,这些名称都有什么含义吗?请看下表。

显然,DDR3-1066,DDR3是指第三代双倍数据率同步动态随机存取内存,1066是指该内存条的工作频率为1066MHz。由于DDR是通过时钟上升沿+下降沿来实现存取数据率双倍的,因此内存条接口上的I/O时钟只有工作时钟频率的一半。

2. DDR颗粒型号

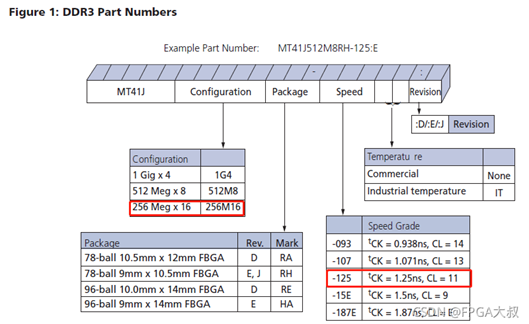

DDR内存条是由多个DDR颗粒级联组成的,以型号为MT41J256M16RH-125 DDR颗粒为例

位宽: 通过256M16RH可知,该DDR颗粒的位宽为16bit。

内存容量: 颗粒型号为MT41J256M16RH-125,容量的计算方式为256M*16bit,即容量为512MB。

I/O****时钟频率: 根据Speed Grade中的“-125”我们可以找到图中的tCK = 1.25ns,对应算出DDR颗粒支持的最大I/O时钟频率:1/1.25ns = 800Mhz。此处的IO时钟频率也就是DDR3内存条的I/O频率。

核心频率: DDR3 I/O接口的时钟频率是核心频率的4倍,因此DDR3的核心频率为200MHz。DDR2芯片内核每次预读取4倍的数据至IO Buffer中,为了进一步提高外传速度,芯片的内核时钟与外部接口时钟不再是同一时钟,外部Clock时钟频率变为内核时钟的2倍。同理,DDR3每次预读取 8倍的数据,其芯片Clock频率为内核频率的4倍。

数据速率: 数据在DDR模式下进行传输,即在时钟的上升沿和下降沿都进行数据传输。因此,对于芯片上的每条数据线,传输速率为800MHz的时钟频率的两倍,即1600MT/s。MT/s是Million Transfers Per Second的缩写,表示每秒钟进行的传输次数为一百万次。

传输速率: 由于DDR上升和下降沿都传输数据的缘故,因此单根数据线实际的传输速率 = 2*800MHz = 1600Mbit/s。

理论带宽: 理论带宽 = 传输速率 * 位宽 * 级联颗粒片数 = 1600 Mbit * 16bit * 4片 = 12.8GB/s。

有效带宽: 有效带宽 = 理论带宽 * 0.8 = 10.24GB/s。

这个有效带宽只是理想状态下,读写DDR能达到的最大带宽。实际使用时,实际的实时带宽和读写DDR的寻址方式有关。

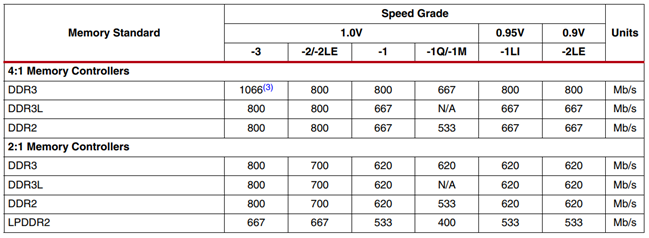

3. Xilinx 7系列FPGA支持的DDR速率表

Artix-7系列FPGA支持的最大DDR速率表

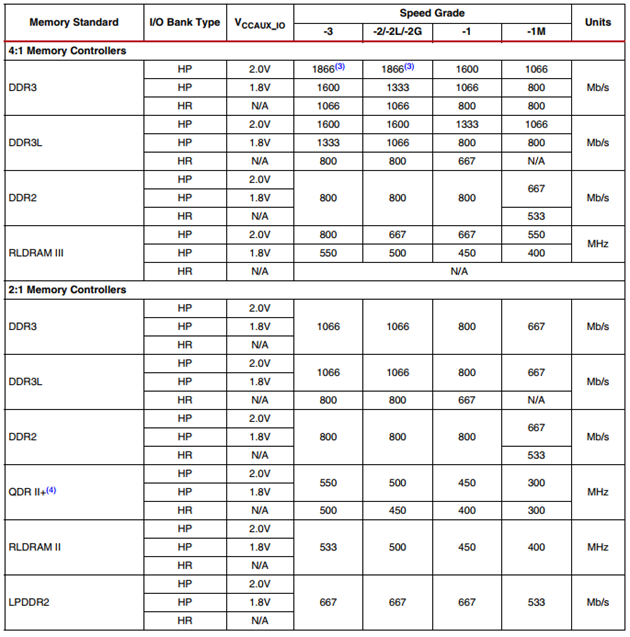

Kintex-7系列FPGA支持的最大DDR速率表

Virtex-7系列FPGA支持的最大DDR速率表

4. 总结

本文向大家总结了下DDR3带宽的计算方法,如果觉得我们原创或引用的文章写的还不错,帮忙点赞和推荐吧,谢谢您的关注。

-

DDR3 SDRAM配置教程2025-04-10 4409

-

DDR3、DDR4、DDR5的性能对比2024-11-29 23026

-

DDR4和DDR3内存都有哪些区别?2023-10-30 14904

-

阐述DDR3读写分离的方法2023-10-18 2245

-

DDR3带宽计算方法 FPGA所支持的最大频率2023-09-15 14509

-

FPGA学习-DDR32022-12-21 5641

-

一文探讨DDR3内存的具体特性和功能2021-02-09 15004

-

DDR3基本知识2019-05-22 1912

-

关于AM3359的DDR3的参数设计2018-05-15 3298

-

ddr4和ddr3内存的区别,可以通用吗2017-11-08 32657

-

ddr3的读写分离方法有哪些?2017-11-06 9640

-

FPGA外接DDR3,带宽怎么计算?2016-02-17 14766

-

如何提高DDR3的效率2015-08-27 9451

-

【小知识分享】SDR/DDR1/DDR2/DDR3的接口区别2014-12-30 3356

全部0条评论

快来发表一下你的评论吧 !