什么是LDO?LDO中的噪声和PSRR介绍

电子说

描述

在本文中,我们将介绍噪声和电源抑制比 (PSRR) 在低压差 (LDO) 稳压器中的影响。让我们简要讨论一下什么是 LDO。

低压降稳压器

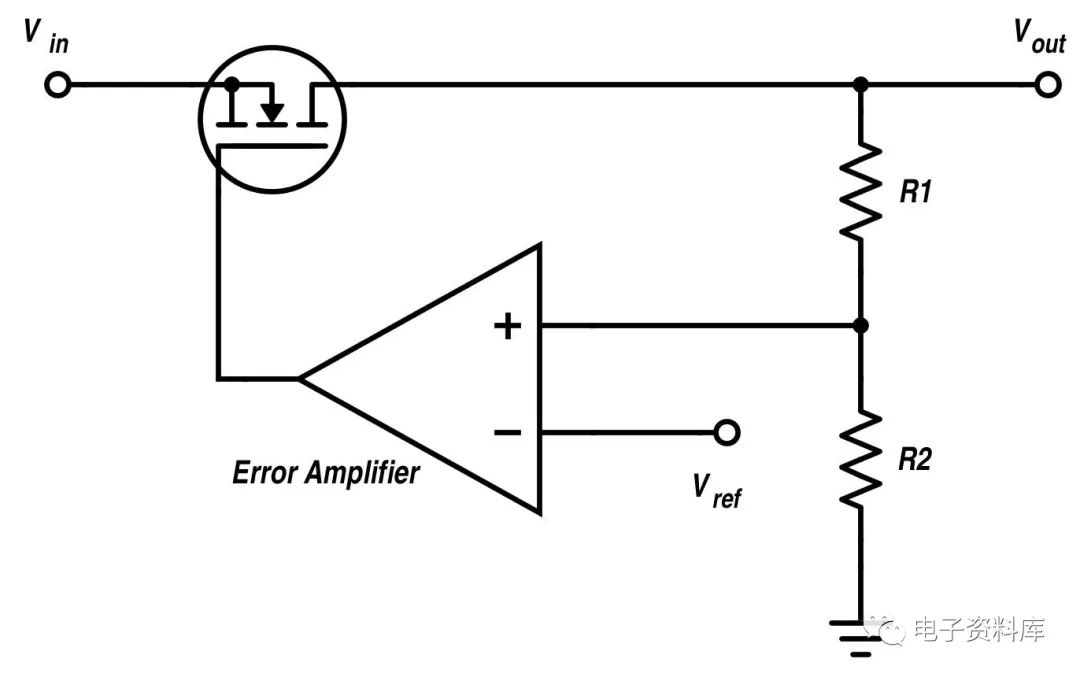

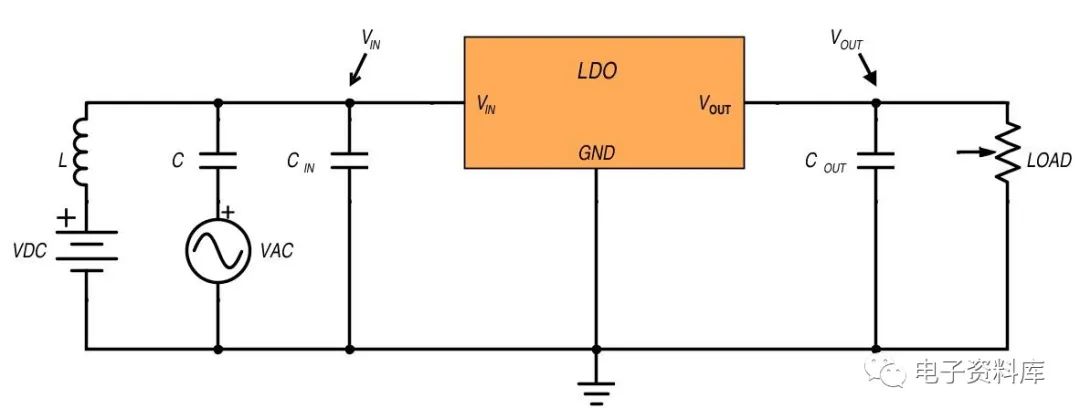

低压差或 LDO 稳压器是一种直流线性稳压器,即使提供给它的输入电压几乎等于输出电压,也可以通过它来控制输出电压。LDO 有两个组件——功率 FET 和一个差分放大器(误差放大器)。LDO的配置见下图:

低压降稳压器 (LDO) 中的噪声

低压差 (LDO) 稳压器中的噪声源可分为两大类,即固有的和外部的。LDO 中的固有噪声有两个主要来源:

- 内部参考电压。

- 误差放大器。

而外部噪声就像喷气式飞机的噪声,是从电路外部的源传递的。

为了获得 15 μA 或更低的静态电流,现代 LDO 使用几十纳安的内部偏置电流进行管理。

降低 LDO 中的噪声

降低 LDO 噪声的两种主要方法是:

- 滤波参考电压(基准电压)

- 降低误差放大器的噪声增益

在某些 LDO 中,使用外部电容器对基准进行滤波。现实情况是,为了达到低噪声条件,许多所谓的超低噪声 LDO 需要一个外部噪声衰减电容器。不幸的是,由于没有进入反馈节点的权利,因此无法降低固定输出 LDO 的输出噪声。如果误差放大器的噪声贡献大于参考噪声的贡献,则可以通过降低误差放大器的噪声增益来降低 LDO 的整体噪声。

确定误差放大器是否是主要噪声贡献者的唯一方法是将固定版本的噪声与特定 LDO 的可变版本的噪声进行比较。如果固定 LDO 的噪声量小于可变 LDO,那么我们可以说误差放大器是主要的噪声源。

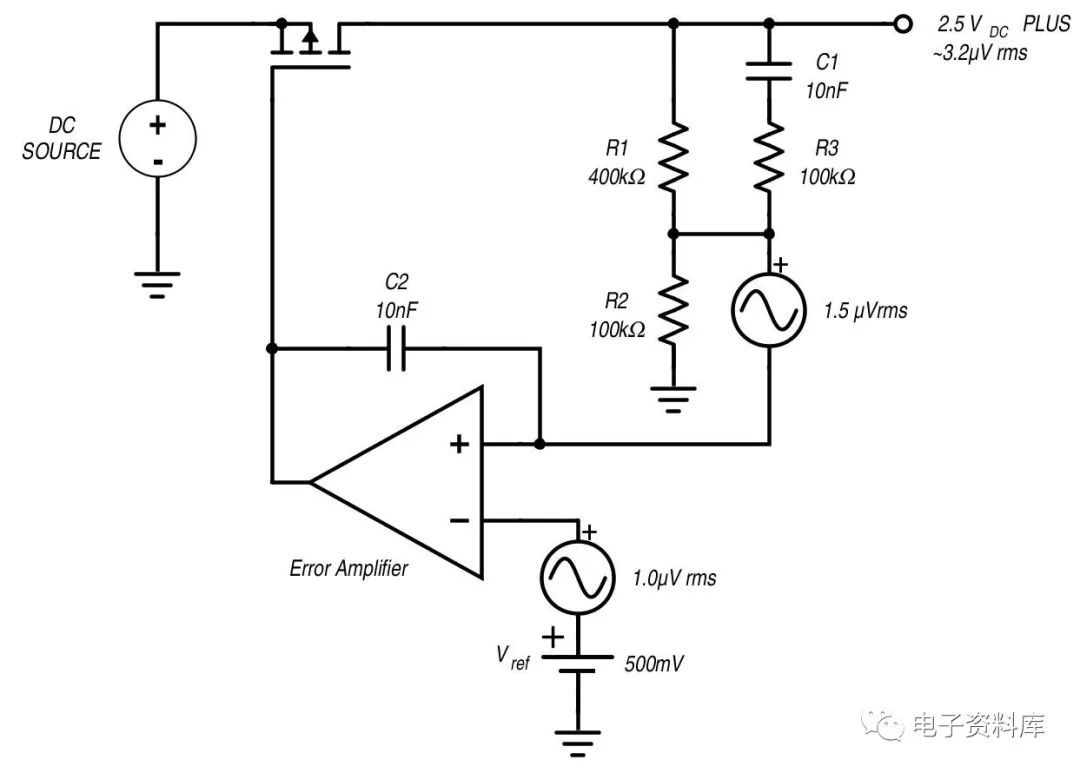

该图显示了一个 2.5 V 输出可修改 LDO,其中 R1、R2、R3 和 C1 是外部组件。

R3 用于将放大器的高频增益设置为 1.5 倍至 2 倍。而C1则用于将降噪系统(C1、R1和R3)的低频零位设置在10Hz和100Hz之间,以确保将噪声降低到1/f。

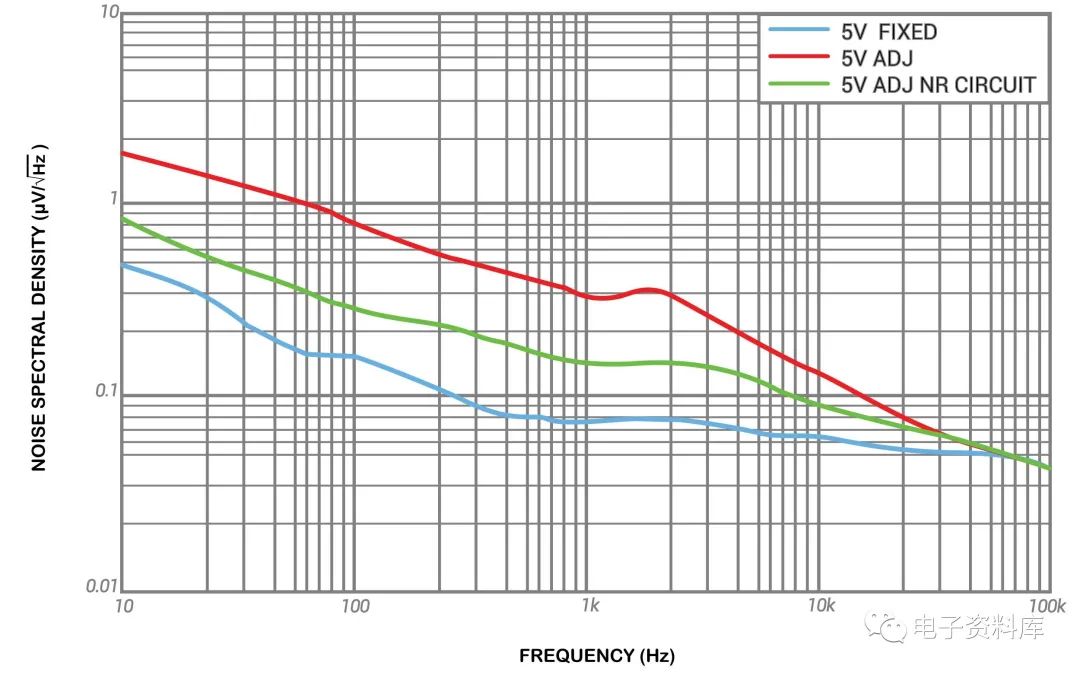

降噪 (NR) 网络对高压自适应 LDO 的噪声频谱密度的结果如下图所示。

在上图中,可以看出,在 20 Hz 和 2 kHz 之间,噪声性能提高了大约三倍 (~10 dB)。

LDO 中的电源抑制比

PSRR 代表“电源抑制比”,随着集成水平的提高,它在现代片上系统 (SoC) 设计中逐渐成为越来越重要的参数。

PSRR 是两个传递函数之间的比率:

• 电源节点到输出节点的传递函数,即 (Asupply(ω))

• 输入节点到输出节点 A(ω) 的传递函数。A(ω) 也称为开环传递函数。

PSRR(ω) = 20 · log [A(ω) /Asupply(ω)] [dB]

在哪里,

1/ Asupply(ω) 是电源增益的倒数,称为 PSR。

从上面的等式可以明显看出,PSRR 与 A(ω) 成正比,与 Asupply(ω) 成反比。因此,如果 Asupply(ω) 减小而开环增益 A(ω) 增大,则 PSRR 将增大。PSRR 基本上是 LDO 抑制输入侧出现的纹波的能力。在理想的 LDO 中,直流频率将是唯一的输出电压。然而,由于高频下出现的小尖峰,误差放大器并不具有完美的功能。考虑到纹波,PSRR 表示如下:

PSRR=20 xlog RippleinputRippleoutput

实际例子

LDO 具有:

PSRR= 55 分贝

频率 = 1 MHz

输入纹波 = 1mV

它可以将该频率下的 1 mV 衰减至输出端仅 1.78 µV。因此,PSRR 增加了 6dB,这等于衰减增加了 2 倍。

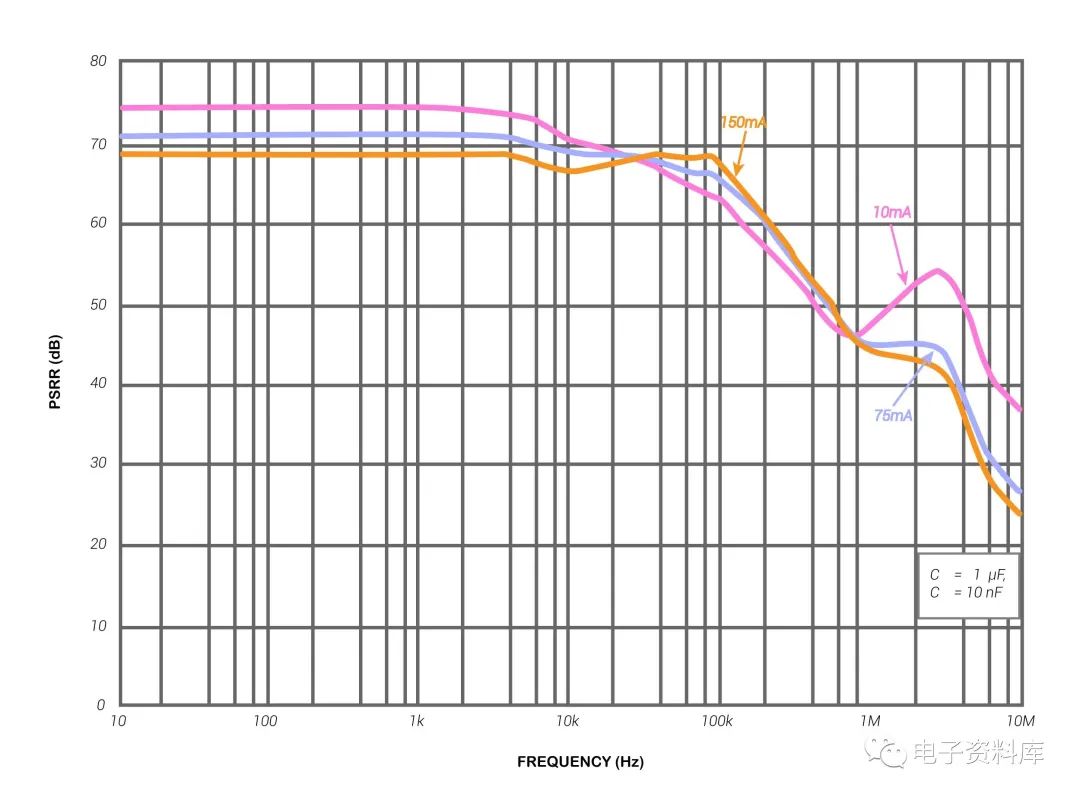

大多数 LDO 在较低频率(通常为 10 Hz – 1 kHz)下具有相对较高的 PSRR。在宽带上具有高 PSRR 的 LDO 可以抑制非常高频的噪声,就像开关产生的噪声一样。

PSRR 会随着频率、温度、电流、输出电压和电压差等一些参数而波动。PSRR 应为负值,因为它用于计算拒绝。但是,该图表将其显示为正数,因此图表中的最高数字表示更高的噪声抑制。

测量 LDO 的 PSRR

有多种测量 LDO 的 PSRR 的方法:

- 使用LC求和节点测量PSRR:

测量 LDO 的 PSRR 的基本方法如下图所示。

在这种方法中,两个电压(直流和交流)加在一起并施加到 LDO 的输入端。工作点偏置电压为 VDC,VAC 为噪声源。在上图中,电容 C 用于防止 VAC 短路 VDC,电感 L 防止 VDC 短路噪声源。

在低频下测量 PSRR 由电感器 L 和电容器 C 创建的高通滤波器决定。该滤波器的 3dB 点由以下

公式决定:Fmin=12ΠLCFmin=12ΠLC

当频率低于 3dB 点时,测量 PSRR 变得困难他们开始减弱。

- 使用加法放大器测量 PSRR

为了获得改进的 PSRR 测量,描述了另一种方法,其中使用高带宽放大器作为求和节点来插入信号,从而在 VAC 和 VDC 之间提供隔离。这种方法可以在下图中看到:

在这种方法中,PSRR 是在无负载条件下测量的。

使用此方法时,在测量 PSRR 时必须牢记以下因素。

- 输入电容可能是高速放大器进入不稳定状态的原因;在测量 PSRR 之前应移除该电容。

- 为了减少电感效应,Vin 和 Vout 应立即用示波器或网络分析仪测量。

- 长线会增加电感并影响结果。这就是为什么测试装置不应该有任何长线。

- 选择 AC 和 DC 输入值时应考虑以下条件:

• VAC(最大值)+ VDC < LDO 的 VABS(最大值)

• VDC – VAC > LDO 的 VUVLO

如果满足以下条件,将获得最佳结果:

• VDC–VAC > Vout + Vdo + 0.5

其中:

Vout 是 LDO 的输出电压

Vdo 是工作点的特定压降电压。

5. 放大器的结果将开始衰减施加到 LDO 的非常高频率的 VAC 信号。

6. MOSFET输出阻抗与漏极电流成反比,导致LDO开环输出阻抗降低,负载电流增加,增益降低。

-

为什么运放和ADC的PSRR不能把LDO输出的内部噪声抑制的干干净净呢?2024-09-03 773

-

什么是LDO?浅析低压差稳压器 (LDO) 中的噪声及电源抑制比2024-03-15 7473

-

浅谈LDO的噪声与PSRR之间的差异2024-03-05 2387

-

LDO的PSRR该如何测量呢2022-11-11 803

-

LDO的PSRR测量2022-11-01 718

-

LDO的PSRR与什么有关?有没有性能较好的LDO推荐。2022-03-21 8120

-

LDO的噪声与PSRR之间的差异2021-05-13 5488

-

一文介绍LDO噪声及分类2020-10-27 1751

-

LDO噪声到底是什么2020-09-08 1610

-

什么是LDO噪声?LDO噪声是如何分类的?2019-08-01 3805

-

LDO噪声简介2019-07-26 1838

-

和电源噪声说「拜拜」!因为这颗具有超高PSRR的LDO2019-07-02 5734

-

LDO噪声消除2018-05-23 1190

-

LDO稳压器的PSRR和输出噪声在RF电路中的选择2009-09-25 1137

全部0条评论

快来发表一下你的评论吧 !