使用集成降压式 DC/DC 模块实现具有较低 EMI、高密度、高效率电源转换

描述

作者:Jeff Shepard

随着电子设备的集成度越累越高、使用数量越来越多,设计人员不断面临着提高效率,同时降低成本、减小尺寸和电磁干扰 (EMI)的压力。虽然电源在功率密度和效率方面也有所提高,但设计人员现在还面临着为异构处理架构开发多轨电源解决方案的难题,这些架构可能由 ASIC、DSP、FPGA和微控制器组成。

传统上,降压式 DC/DC 转换器用于为此类架构供电,但随着电源轨数量的不断增加,使用传统分立降压式 DC/DC 转换器与、控制 IC、内部或外部功率MOSFET,再加上外部电感器和电容器,可能会变得既复杂有耗时。相反,设计人员可以使用具有多轨和可编程定序的自足式降压 DC/DC转换器模块。这种模块可以更好地控制 EMI,发热更少,且所需面积更小。

本文将回顾嵌入式设计的电源系统需求,讨论各种方法和设计人员需要考虑的问题,然后介绍自足式降压 DC/DC 模块的概念。然后,以 MonolithicPower Systems 的器件为例,简要回顾设计人员需要牢记的设计和布局考虑因素,以便最大限度地发挥这些模块的性能优势。

为什么嵌入式系统需要很多电源轨

诸如 5G基站等嵌入式设计旨在支持智能手机、智能互联设备不断增加的数据要求,其应用涵盖家居和工业自动化、自主驾驶车辆、医疗保健和智能可穿戴设备等。这类基站通常使用 48伏输入电源,经 DC/DC 转换器降至 24 伏或 12 伏,然后进一步降至 3.3 伏至 1 伏以下的许多子电源轨,为基带处理阶段的

ASIC、FPGA、DSP 和其他设备供电。通常,电源轨需要对启动和关断进行排序,这会进一步增加电源系统的复杂性。

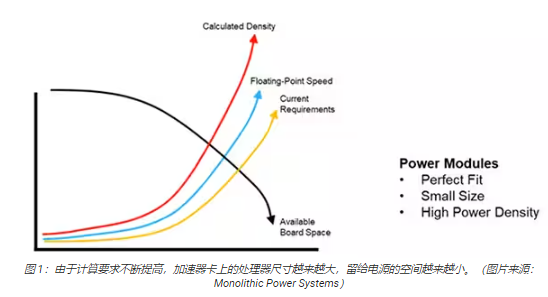

以 5G 基站为例,传统的 CPU 本身已经不能满足处理要求。但是,使用加速卡与 FPGA配合使用,在系统可重构性、灵活性、开发周期短、高度并行计算、低延迟等方面都占有优势。但 FPGA 电源的空间越来越小,而且对电源轨的性能要求也很复杂(图1)。

输出电压失调:电压轨的输出电压偏差必须小于 ±3%,设计时应留有足够裕量。通过优化控制回路,提高带宽,保证其稳定性,应谨慎使用和设计去耦电容器。

单调启动:所有电压轨的初始值必须单调上升,在设计上应阻止输出电压回到起始值。

输出电压纹波:稳态运行时,所有电压轨的输出电压纹波(模拟电压轨除外)必须最高达到 10 毫伏(mV)。

时序:FPGA 在启动和关断期间必须满足特定的时序要求。

随着数据处理带宽要求越来越高,处理器对电流和功率的要求也愈加苛刻。加速器卡的计算密度和浮点速度的要求也越来越难以满足。加速器卡槽一般都采用 PCIe标准,所以板卡的尺寸是固定的。由于计算要求不断提高,处理器尺寸不断增大,留给电源的空间已经变得很小。

电源系统设计替代方案

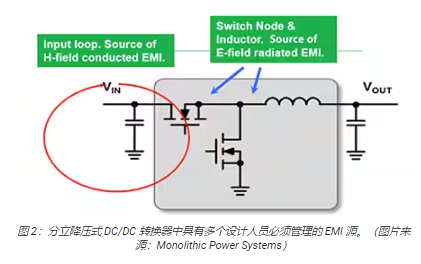

使用传统的分立降压式 DC/DC 转换器,配以控制 IC、内部或外部功率MOSFET,再加上外部电感和电容,组成了嵌入式系统供电的一种方法。如上所述,当需要多轨电源解决方案时,对设计人员来说是一个复杂、耗时的过程。除了考虑效率最大化和解决方案尺寸最小化外,设计人员还必须谨慎对待滤波器元件的布局和放置,以最大限度地减少转换器和电感电路中的开关电流引起的传导和辐射EMI(图 2)。

DC/DC 转换器通常会通过输出功率 MOSFET 开关节点对地和输入电容对地之间形成的电流环路的磁场产生传导 EMI。同时,这种转换器还通过MOSFET 开关节点到电感连接处产生辐射电场 EMI,因为该器件连续从高输入电压水平切换到地,所以具有很高的dV/dt,同时会通过电感内产生的电磁场产生辐射电场 EMI。如果设计不当,往往会导致耗时的 EMI 实验室重新测试和多次设计迭代。

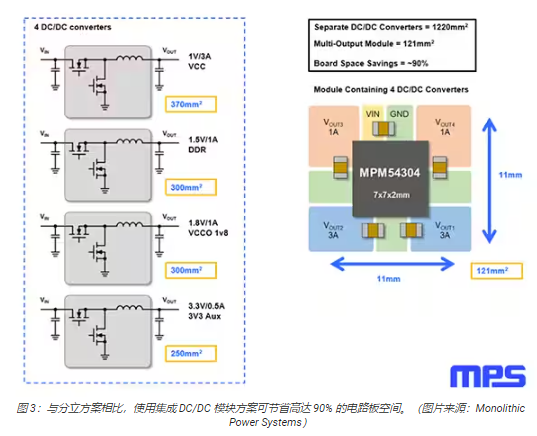

使用分立降压式 DC/DC 转换器向 ASIC 或 FPGA 供电的四轨解决方案可占用 1220 平方毫米 (mm2)(图 3)。使用基于电源管理 IC(PMIC) 的解决方案可以将这一数字降低至约 350mm2。作为替代方案,设计人员可以使用独立的四输出 DC/DC 转换器模块,将解决方案的尺寸缩小到只有121 mm2,同时还可以简化设计流程,加快产品上市速度。半导体工艺技术和封装结构的进步意味着最新一代的 DC/DC模块在较小的外形内实现了非常高的功率密度、高效率和良好的 EMI 性能。

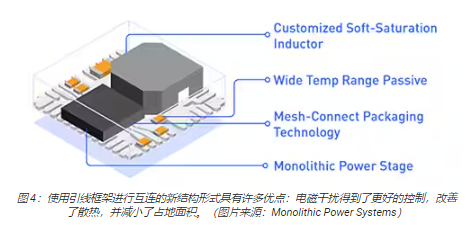

新的构建技术,如封装内倒装芯片和“网状连接”引线框架技术,意味着 IC、电感器和无源器件可以直接安装在引线框架上,而不需要导线键合或额外的内部 PC板(图 4)。与使用内部 PC 板基板或导线键合的老式结构相比,这些新技术可以最大限度地减少印制线长度,并且与无源元件直接连接可以保持低电感,从而最大限度地减少EMI。

使用接点栅格阵列 (LGA) 封装形式,直接贴装至目标 PC 板上,比起其他引线可辐射 EMI 的单线 (SIL) 或 SIL 封装 (SIP)式转换器具有更低的 EMI 曲线。

四路输出可编程集成 DC/DC 模块

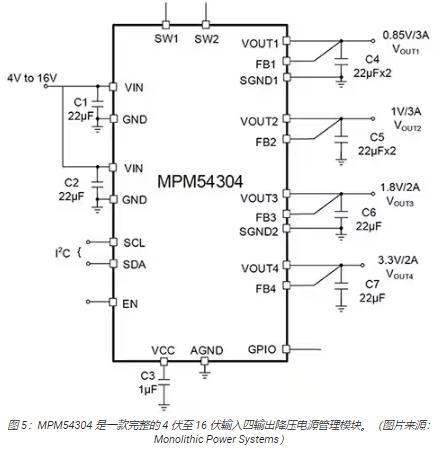

为了满足嵌入式系统的多轨、高功率密度需求,设计人员可以使用 Monolithic Power Systems 的 MPM54304(图 5)。MPM54304 是一个完整的电源管理模块,集成了 4 个高效率、降压式 DC/DC 转换器、电感器和一个灵活的逻辑接口。MPM54304 在 4 伏至16 伏的输入电压范围内工作, 可支持 0.55 伏至 7 伏输出电压。四条输出轨分别可以支持高达 3 安培 (A)、3 A、2 A 和 2 A的电流。其中,两条 3 A 轨和两条 2 A 轨可以并联,分别提供 6 A 和 4 A电流。设计人员应注意,并联模式下的最大输出电流也受到总功率耗散的限制。这样,我们就可灵活地选择几种输出配置(但受总功率耗散限制)。

3 A、3 A、2 A、2 A

3 A、3 A、4 A

6 A、2 A、2 A

6 A、4 A

MPM54304 还提供了启动和关断的内部排序。可以通过多时可编程 (MTP) 电子保险丝或通过 I2C 总线对导轨配置和排序进行预编程。

这款固定频率恒定时间 (COT) 控制式 DC/DC 转换器可具有快速瞬态响应能力。其默认 1.5 兆赫 (MHz)开关频率大大减小了外部电容器的尺寸。在连续电流模式 (CCM) 工作期间,开关时钟锁定并从降压 1 到降压 4 移相。输出电压可通过 I2C 总线调节或 MTP电子保险丝预设。

该器件保护功能全面,包括欠压锁定 (UVLO)、过电流保护 (OCP) 和热关断。MPM54304 所需的外部元器件数量极少,并采用节省空间的 LGA(7 mm x 7 mm x 2 mm) 封装(图 6)。LGA 的扁平外形使其适合板后布置或置于散热器下。

设计和布局注意事项

MPM54304 的边沿引脚布局简单,使布局和 PC 板设计更容易。只需 5 个外部器件,整体解决方案小巧紧凑。LGA封装使得坚实的接地平面覆盖了模块下方的大部分区域,这有助于封闭涡流回路,进一步降低 EMI。

这种降压转换器的输入电流是不连续的,在保持直流输入电压的同时,需要一个电容器向转换器提供交流电流。设计人员应使用低等效串联电阻 (ESR)电容器,以获得最佳性能。推荐使用 X5R 或 X7R 电介质陶瓷电容器,因为其 ESR 低、温度系数小。对于大多数应用来说,22 微法拉 (µF)电容器就足够了。

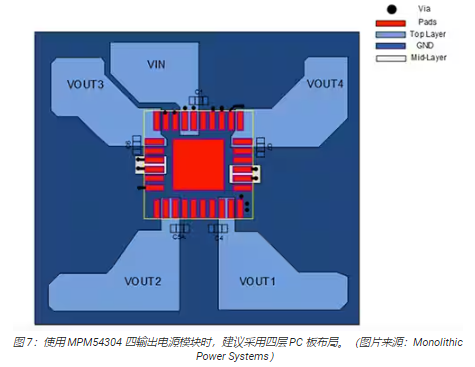

高效的 PC 板布局是 MPM54304 稳定运行的关键。为了达到更好的散热性能,建议使用四层 PC 板(图

7)。为了达到最佳效果,设计师应该遵循这些准则。

尽量减少电源回路

用一个大型接地平面直接连接 PGND。如果底层是接地平面,则在 PGND 附近增加过孔。

确保 GND 和 VIN 处的大电流路径具有短而直接的宽印制线。

将陶瓷输入电容尽可能地靠近该器件。

尽量保持输入电容和 IN 尽可能短,尽可能宽。

将 VCC 电容尽可能靠近 VCC 和 GND 引脚。

将 VIN、VOUT 和 GND 连接到一个大面积的铜片上,以提高散热性能和长期可靠性。

将输入 GND 区域与顶层的其他 GND 区域分开,并在内部层和底层通过多个过孔连接在一起。

确保在内部层或底层有一个集成的 GND 区域

使用多个过孔将电源平面连接到内部层。

结语

随着处理架构的不断发展,以应对苛刻的数据应用,设计人员面临着开发多轨电源解决方案的挑战:要求这些解决方案能够支持更强的处理能力和更多体积不变或更小的电子器件。在设计这些系统的电源解决方案时,降压式DC/DC 转换器是关键,但实施起来可能很复杂。

如图所示,设计人员可以转向具有多电源轨和可编程排序功能的自足式降压 DC/DC转换器模块,从而简化设计流程,加快产品上市。同时,新的构建技术使这些自足式模块具有了许多性能优势:电磁干扰得到了更好的控制,改善了散热,减小了占地面积。

-

高密度400W DC/DC电源模块,集成平面变压器和半桥GaN IC2025-01-22 601

-

AN77-适用于大电流应用的高效率、高密度多相转换器2025-01-08 508

-

提高效率的DC电源模块设计技巧2024-02-26 2294

-

用于高密度和高效率电源设计的意法半导体WBG解决方案2023-08-01 596

-

DC/DC转换器的高密度印刷电路板(PCB)布局2022-11-18 856

-

具有PMBus接口的高密度160A 4相DC DC降压转换器设计2022-09-08 711

-

使用集成降压式DCDC模块实现具有较低EMI高密度高效率电源转换2021-03-17 1047

-

具有双端口CLA应用的高效率降压DC/DC转换器2020-07-25 1990

-

双输出高效率高密度模块稳压器DC2066A2020-03-17 4116

-

60V降压型DC/DC转换器保持高效率2019-06-25 2778

-

高效率高密度电源无需散热器即可提供200A电流2019-05-31 2119

-

高密度DC/DC转换器的PCB布局第二部分2018-09-05 2254

-

PI31xx系列高密度隔离式DC-DC转换器2016-01-06 1307

-

Vicor 发布高密度AC-DC前端模块2012-11-16 1984

全部0条评论

快来发表一下你的评论吧 !