dcdc电源纹波大怎么解决

电源/新能源

描述

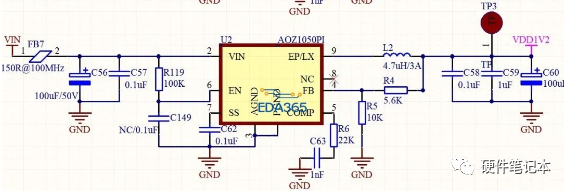

网友eefishing问题: 一个DC-DC电源转换,纹波有点大,上传原理图和PCB图 用AOZ1050PI设计的一款DC-DC电源转换,输入9~18V,输出1.2V,AOZ1050开关频率500KHz,现在用示波器测得输出大概有100mV,Vp-p在485KHz左右的纹波。

请问各位专家:

1 这个指标的纹波是否在设计许可的范围之内?在一般情况下,DC-DC电源转换的纹波在一个什么范围内可以认为是正常的? 2 从原理图和PCB图上,这个设计是否还能够进一步优化降低纹波?还请指出。 敬请各位斧正。

网友mituone的回复: 100mV 的纹波(Ripple)对数字线路应该没什么问题,对模拟线路就看情况了,有的线路很敏感需要更低。但芯片资料展示在满载(Full Load)状况下,纹波(Ripple)可以压到 20mV 左右。

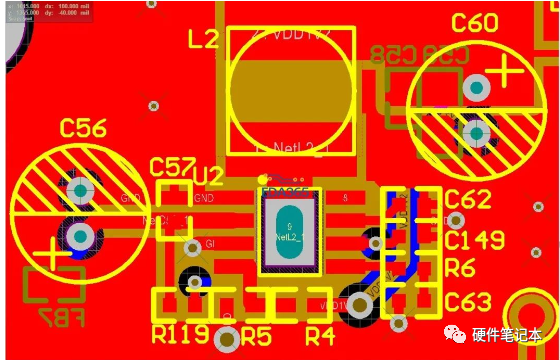

布线建议︰ L2 在上方,但 FB 在 AOZ1050 Pin 4,造成反馈路径绕了一大圈才回到芯片。将 L2 移到下方,可以缩短反馈路径。 AOZ1050 Pin 3 Power Return Ground 只有单点落地显得太单薄,要注意一盎司(oz)铜厚下,10 mil 的落孔只有 0.8A 的承受力,如果是使用十字线接地,就 4 条十字线加起来可承受的电流。宜将地铺大,并多打导通孔与背面的地连通。 注意芯片资料上的 AOZ1050 Pin 4 PGND 与 R5 落地的画法,它们是用不同的地符号。意思是说他们建议你用隔离的地(Isolation Ground),做法上就是 R5 和 Pin 4 拉在一起,然后单点落地。 输出应该先过滤波电容 C58、C59 和 C60,再给其它线路,注意到你的输入电容 C56 和 C57 就做得不错,可以参考它的做法。 注意线宽与承载电流的关系,输入与输出线宽需要计算。不晓得 C60 "+" 号旁边那条细线是做什麽用的?看起来很细。

布线大原则︰ 让输入或输出滤波电容和地造成的回路越短越好。

仍需检视的部份︰ L2 电感宜选用有屏蔽(Shielding)的封装,避免漏磁(Magnetic Leakage)干扰。 L2 电感的额定电流(IDC1 和 IDC2)宜被检视,避免峰值电流(Peak Current)超过或温度升高,造成电感量不足产生纹波和噪声。 L2 直流电阻(DCR)宜被检视,太高效率不好、容易发热。 AOZ1050 Pin 5 COMP 上的补偿电路,芯片资料上有计算公式,宜试算一下是否搭配得宜。 电解电容 C56 和 C60 的 ESR 越小越好,如果您真的很在意纹波及噪声的大小,电解电容尽量选用可靠一点的厂牌。

编辑:黄飞

-

抑制电源纹波的方式详解2024-02-19 2652

-

测DCDC纹波的标准2023-07-14 3283

-

DCDC电源纹波的正确测试方法2023-05-18 8961

-

DC-DC电源模块如何应对纹波噪声2022-12-09 6813

-

DC-DC开关电源电路纹波分析2022-09-19 11496

-

隔离升压DCDC电源模块 外围加滤波电路 纹波100mV左右深圳市俞霖科技开发有限公司 2022-06-06

-

DCDC常见问题之输出纹波大2021-11-07 2549

-

如何去改善DCDC输出电压纹波过大的问题2021-11-01 6992

-

高效率低纹波峰值电流模Boost型DCDC稳压器设计2021-08-31 1231

-

请问DCDC电源纹波输出有点大该怎么办?2019-09-30 10551

-

DCDC电源纹波如何测量?2018-11-13 5163

-

dcdc电源模块输入端的反射纹波会影响前级系统工作么?2018-06-28 5783

-

基于Buck电路的开关电源纹波的计算和抑制2015-11-20 1010

-

DCDC输出电压纹波的测量2012-08-14 6832

全部0条评论

快来发表一下你的评论吧 !