利用FPGA设计基于LVDS的图像数据采集传输系统

描述

点击上方蓝字关注我们

引言

图像信息的获取和传输是图像处理系统的重要组成部分,直接影响图像处理系统的性能。图像信息的采集包括对图像数据、各种附带参数信息以及状态控制信号的采集,一般图像信号和状态参数信号以及控制信号是独立产生的,因此需要设计一种系统能够将外部设备产生的图像数据和状态控制信号同步采集,并能长距离高速传输,综合考虑到图像采集系统所要求的实时性,可靠性,以及FPGA在数字电路的设计中的优势,为此本文讨论了一种利用FPGA实现基于LVDS的图像数据采集传输技术。

系统设计

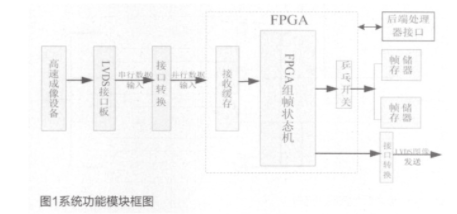

高速图像数据的采集传输系统如图1 所示,主要包括图像数据源的形成、数据信息的处理和缓存以及帧数据的转发三部分。其中,图像数据源的形成过程中,成像设备作为图像数据的来源,它为系统提供高分辨率的可见光和红外图像,考虑系统的实时性和高可靠性因素,采用LVDS传输接口实现数据长距离高速传输,解决了传输瓶颈问题,图像数据在进入FPGA之前需通过数据格式转换接口(采用MAX9218实现)将串行的数据转换为并行数据并缓存。

数据信息的处理由协处理器FPGA完成,主要包括图像数据及相关参数信息的采集、缓存、组帧和图像数据的转发。其中图像数据的组帧过程最为复杂, FPGA根据图像源中帧同步、行同步、图像选择信号接收解串图像,存储至缓存区,并将图像附带的参数信息写入缓存后部,经组帧状态机形成所需的图像数据帧。

图像数据帧形成后,转发存储至乒乓结构的帧存储器,其容量为:512×512×8bit=2Mb。同时硬件逻辑自动将图像和配套参数信息数据通过LVDS图像发送接口发送至数据链,图像数据再次以串行的LVDS方式传输到后续设备进行处理。

系统实现

FPGA及外围硬件电路

在接口转换电路模块中,图像数据接收端和发送端均需采用LVDS串行方式进行传输,所以在接收端将串行输入的数据并行接收进FPGA进行处理和在发送端将并行的数据串行输出时,需要进行并串和串并转换。

本设计选用MAXIM公司点对点LVDS串行/解串器芯片MAX9247/MAX9218实现数据收发。

在MAX9218接收端,需要进行数据格式转换,将串行数据源变成并行格式供FPGA处理,同样在图像数据链路终端发送方MAX9247对输入的图像数据也有特定的时序要求,涉及到数据位和控制位的交替传输,需要由FPGA完成数据格式的转换, 并产生相应的控制信号DE_IN。

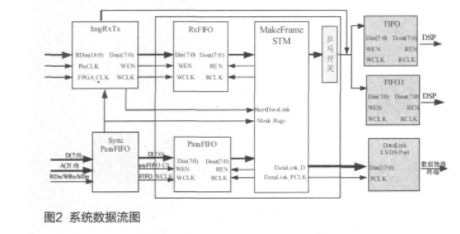

可编程器件FPGA选用Xilinx公司Virtex-4系列XC4VLX25。实现的功能主要是:根据输入的行帧同步,采图像同步和图像选择信号来实现图像数据的接收,并缓存到FPGA内部的接收RxFIFO中,进行帧头帧尾识别、时序转换,控制信号的生成,并且根据自定义的通讯协议,从数据流中分解出数据帧,同时将原始图像数据和状态数据打包到同一帧数据包中,输出至数据链路终端。

图像数据链路层

由图3数据的流向来分析,从LVDS接口板输出的串行图像数据由14个数据位(数字图像数据为D0--D13,低位在前高位在后)、帧同步、行同步、时钟同步、图像选择信号、采图同步信号组成。图像数据同步时钟采用7.375MHz,DE_IN由图像的帧同步信号产生,帧、行同步均为高电平有效,图像选择信号用来区分红外和可见光图像,红外图像为256×320b,可见光图像为512×512b,19位图像数据信号经过MAX9218解串后的数据和控制位接入FPGA。

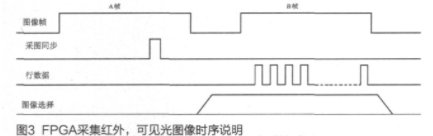

FPGA设计时,针对红外和可见光两种不同类型的图像数据进行采集传输,设置一个模式寄存器ModeReg来实现图像选择,可以填0或1,用来区分红外和可见光,当采集可见光时,每输出一帧有效图像数据,需输出两个帧信号,第一帧内(A帧)只输出采图同步信号,不输出图像数据、行信号等,第二帧(B帧)中不输出采图同步信号,只输出图像数据、行信号等;当采集红外图像时,只需输出一帧,图像选择信号在第一个帧信号的下降沿跳变,至第二个帧信号下降沿有效,高电平表示红外图像,低电平表示可见光图像。具体时序参考图3。

经过FPGA组帧完成的帧数据同时要转发到终端数据链路和外部帧存储器中,供后续设备调用。为了实现后续设备提取图像信息时的实时性,外部存储模块采用由乒乓开关控制的两个片外帧存储器,应用FPGA实现双帧存交替切换,将图像数据存储在两个独立的FIFO中,FIFO采用IDT公司的IDT72V2103,此器件快速的存取允许图像实时存储转发。在FPGA的控制下,FIFO空间的一帧数据送出后,然后开始将FIFO1 空间的数据送出,同时又向FIFO中写入下一帧数据,这样可以保证后续图像处理设备不间断的提取图像数据,以实现快速处理,提高工作效率。

组帧状态机

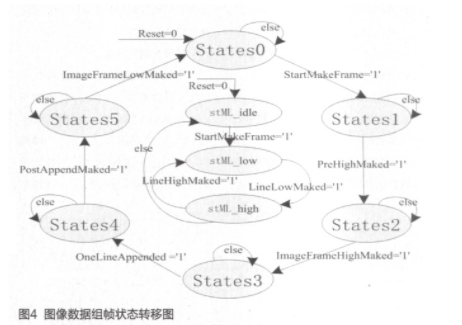

状态机在FPGA内部设计成两部分,为组帧状态机(外圈)和组行状态机(内圈)。其中组帧状态机各状态转移顺序及条件见图4,各状态占用时间可以通过组行状态机中的行计数来控制,近而可以完成不同大小规格的图像的接收。组帧状态机共有6个状态。

state0:空闲状态(系统复位)。state1:帧有效期开始到行有效期开始之间的延时。state2:图像帧有效期,state3:图像参数帧有效期。state4:行有效期结束到帧有效期结束之间的延时。state5:帧无效期。Reset为输入的状态机复位信号,在系统复位状态,如果用来启动状态机的信号StartMakeFrame = 1,状态机开始工作,进入系统下一状态,组帧状态机在各状态转移条件满足时,依次进入下一状态,否则,保持在原状态。

组行状态机共有3个状态。

stML_Idle:空闲状态。stML_High:行有效期。stML_Low:行无效期。在外圈组帧状态机的每个状态中,包含n个组行状态,所包含的组行状态机中的行数即组帧状态机各状态所占用时间,组行状态机和组帧状态机启动条件一致,同时启动。

以采集可见光图像数据为例,上电复位期间系统处于states0状态,状态机用外部输入的7.375MHz时钟同步整个运行过程,图像的帧、行、图像数据等信号在同步时钟的下降沿跳变,上升沿锁存。一帧图像数据的大小为512×512bit,并将图像附带的参数信息写入图像数据后一行(即513行),在帧有效期间(states1、 states2、 states3状态),CLK 信号作为行计数器的时钟,每帧图像在行有效之前有1行无效图像信号(states1), 在states2状态下,控制采集一帧中的前512行,在states3状态下,采集图象的参数信息,将图像数据和状态参数组合为统一的数据帧,采集完一帧图像数据后等待下一个帧同步信号的到来。在行有效期(stML_High)控制采集一行中的512个像素点数据,在CLK信号的上升沿进行计数, 在数据有效期间采集完512个像素点,等待下一个行同步信号的到来,按同样方式对下一行512像素点数据进行采集,直至采集完一帧中的512行。

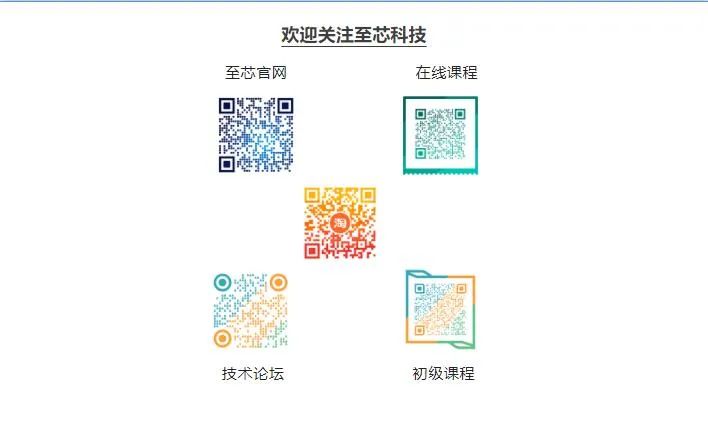

系统仿真

在该系统中,状态机设计是难点,图5是运用Active-HDL7.1仿真工具的状态机仿真结果,仿真时,采用7.375MHz时钟同步,状态机启动后,计数寄存器里的数据递减,进而产生各状态转移满足的条件,以此实现状态机的翻转。

在Active-HDL7.1中编写TestBench文件时,通过向组帧状态机计数寄存器写数,来控制各状态所占用的时间,利用 StartMakeFrame信号高电平启动状态机,各状态发生翻转时,状态完成标志就产生产生高电平跳变。

根据图5的仿真结果,可以看出组帧状态机工作正常,所有的逻辑关系也都验证无误。

结语

本文采用FPGA设计实现高速图像采集系统,并采用LVDS接口实现接收与发送,各种模块之间通过缓存实现通信,避免图像的丢失;采集的图像类型和图像尺寸可以通过软件重新配置FPGA进行调整。总之,基于FPGA 的高速专用图像采集系统电路集成度高、信噪比高、功耗低、成本低、速度快以及接口方便,所设计系统采用两帧切换存储方式,使得后续的其它图像处理模块能够与图像采集模块并行工作,为图像处理器的高度集成化实现提供了可能性。

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:利用FPGA设计基于LVDS的图像数据采集传输系统

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- FPGA

-

FPGA的多通道数据采集传输系统2024-12-09 1723

-

基于ARM和FPGA设计高速图像数据采集传输系统2023-09-27 3013

-

如何利用ARM和FPGA设计一种高速图像数据采集传输系统?2021-06-02 2653

-

基于FPGA的X射线脉冲信号数据采集系统2021-06-01 1338

-

如何采用FPGA和CMOS数字传感器实现图像数据传输的图像监测系统?2021-05-26 1582

-

如何利用FPGA实现高速连续数据采集系统设计?2021-04-08 2412

-

如何使用FPGA实现图像数据采集卡及其驱动设计2021-02-03 1669

-

如何使用FPGA实现新型高速CCD图像数据采集系统2021-02-02 1376

-

如何使用FPGA实现多通道高速CMOS图像采集系统的设计2021-01-29 1716

-

基于FPGA和EPP的图像传感器高速数据采集2020-04-30 2143

-

基于FPGA的新型高速CCD图像数据采集系统2016-09-22 723

-

基于FPGA的图像数据采集卡及其驱动设计2016-08-29 835

-

基于FPGA的数据采集系统2012-08-11 5647

-

基于FPGA的主从式高速数据采集与传输系统2011-09-29 3502

全部0条评论

快来发表一下你的评论吧 !