高速信号阻抗匹配的重要性

电子说

描述

1.概述

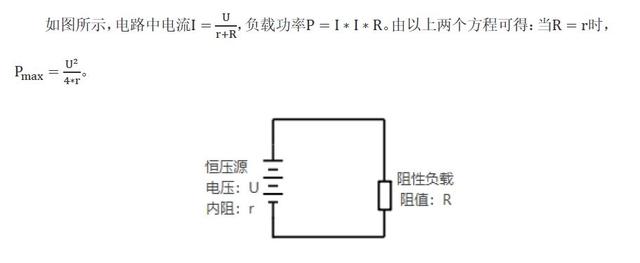

阻抗匹配(Impedance Matching)主要用于传输线上,以此来达到所有高速、高频信号均能传递至负载点的目的,而且几乎不会有信号反射回来源点,从而提升传输效益。对于不同特性的电路,匹配条件是不一样的。在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。

当激励源内阻抗和负载阻抗含有电抗成份时,为使负载得到最大功率,负载阻抗与内阻必须满足共扼关系,即电阻成份相等,电抗成份只数值相等而符号相反,这种匹配条件称为共扼匹配。

2.阻抗匹配的重要性

阻抗匹配主要有两点作用,调整负载功率和抑制信号反射。

● 调整负载功率

假定激励源已定,那么负载的功率由两者的阻抗匹配度决定。对于一个理想化的纯电阻电路或者低频电路,由电感、电容引起的电抗值基本可以忽略,此时电路的阻抗来源主要为电阻。

● 抑制信号反射

当一束光从空气射向水中时会发生反射,这是因为光和水的光导特性不同。同样,当信号传输中如果传输线上发生特性阻抗突变也会发生反射。波长与频率成反比,低频信号的波长远远大于传输线的长度,因此一般不用考虑反射问题。高频领域,当信号的波长与传输线长处于相同量级时反射的信号易与原信号混叠,影响信号质量。通过阻抗匹配可有效减少、消除高频信号反射。

信号源与传输线之间的匹配,分为两种情况,一种是信号源无反射,方法是接入信号源与传输线之间接入匹配装置;另一种是信号共轭匹配,方法是信号源与被匹配电路之间接入匹配装置,这种情况下多属于有源电路设计。

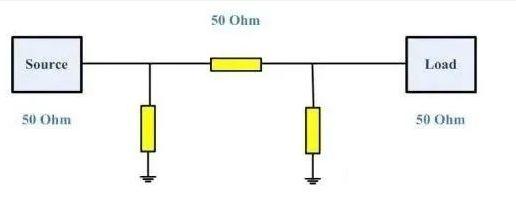

如下图所示,其最理想的模型是希望信号源Source端的输出电阻为50欧姆,传输线的阻抗为50欧姆,负载Load端的输入阻抗也是50欧姆。然而实际情况是源端阻抗不会是50欧姆,负载端阻抗也不会是50欧姆,这时候就需要若干个阻抗匹配电路。

3.阻抗匹配方式

● 串联终端匹配

串行连接终端匹配技术是在源端的一种终端匹配技术,和其他类型的终端匹配技术不同。它是由连接在驱动器输出端和信号线之间的一个电阻组成,驱动器输出阻抗Rᴅ以及电阻R的和必须与信号线的特征阻抗匹配。

优点:

1.器件单一,只需要一个电阻元件;

2.抑制振铃,减少过冲;

3.增强信号完整性,产生更小的EMI;

4.适用于集总线型负载和单一负载。

缺点:

1.接收端的反向反射依然存在;

2.影响信号上升时间并增加信号延时;

3.分布式负载不适用,因为在走线路径的中间,电压仅为源电压的一半;

4.当TTL、CMOS器件出现在相同网络时,串联匹配不是最佳选择。

● 并联终端匹配

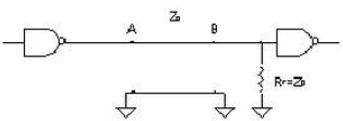

并联终端匹配是最简单的阻抗匹配技术, 通过一个电阻R将传输线的末端(可能是开路,也可能是负载)接到地或者接到VCC上,电阻的值必须同传输线的特征Z₀阻抗匹配,以消除信号的反射。

优点:

1.器件单一,只需要一个电阻元件;

2.适用于分布式负载;

3.反射几乎可以完全消除;

4.电阻阻值易于选择。

缺点:

1.该电阻会增加系统电路的功耗;

2.降低了噪声容限(比如将TTL输出终端匹配到地会降低Vᴏʜ的电平值,从而降低接收器输入端的抗噪声能力)。

● 戴维南终端匹配

戴维南终端匹配技术也叫做双终端匹配技术也就是双电阻形式的并联匹配,它采用两个电阻R₁和R₂来实现终端匹配,要求的电流驱动能力比单电阻形式小,这是由于R₁和R₂的并联值与传输线的特性阻抗相匹配,每个电阻都比传输线的特性阻抗大。

根据戴维南终端匹配设计规则,R₁通过从VCC向负载注入电流来帮助驱动器更容易到达逻辑高状态;R₂帮助通过向地吸收电流来将驱动器下拉到逻辑低状态。当R₁和R₂的并联同信号线的特征阻抗Z₀匹配时可以加强驱动器的扇出能力,并且减小由于信号占空比的变化导致的功耗的改变。

匹配设计规则:1.两个电阻的并联值必须与传输线的特性阻抗相等;2.与电源VCC连接的电阻不能太小。需保证驱动器的Iᴏʟ电流在驱动器的性能指标范围内,以免信号为低电平时灌电流过大,损坏器件;3.与地连接的电阻不能太小,需保证驱动器的Iᴏʜ电流在驱动器的性能指标范围以内,以免信号为高电平时拉电流过大,损坏器件。

优点:

1.终端匹配电阻采用上下拉的方式,有效抑制信号过冲;

2.信号摆幅降低,加强了系统的噪声容限;

3.增强驱动器的驱动能力,在5V和3.3V的CMOS和BiCMOS的系统中显得尤为有益。

缺点:

1.存在静态直流功耗;

2.戴维南电压接近于器件的开关阈值电压,对于CMOS逻辑器件来说会导致更高的功耗。

RC终端匹配

RC终端匹配技术也称之为AC终端匹配技术,它是由一个电阻R和一个电容C组成的,电阻R和电容C连接在传输线的负载一端。

RC终端匹配技术的优势在于终端匹配电容阻断了直流通路,因此节省了可观的功率消耗,同时恰当地选取匹配电容的值,可以确保负载端的信号波形接近理想的方波,同时信号的过冲与下冲又都很小。

RC终端匹配技术的一个缺点是信号线上的数据可能出现时间上的抖动,这取决于在此之前的数据模式。

● 肖特基二极管终端匹配

肖特基二极管终端匹配技术也称之为二极管终端匹配技术,由两个肖特基二极管组成,此法不属于阻抗匹配的思路,而是通过二极管的钳位来减小过冲和下冲;传输线末端的信号反射,导致负载输入端上的电压升高超过VCC和二极管D1的正向偏值电压,使得该二极管正向导通连接到VCC上,从而将信号的过冲嵌位在VCC和二极管的阈值电压的和上,同样,连接到地的二极管D2也可以将信号的下冲限制在二极管的正向偏置电压上;因为二极管不会吸收任何的能量,仅仅只是将能量导向电源或者地,传输线上就会出现多次的信号反射。由于能量会通过二极管到电源和二极管到地的消耗,信号的反射会逐渐衰减,能量的损耗限制了信号反射的幅度,以维持信号的完整性。

4.阻抗匹配在PCB走线中的应用

高频领域中,信号频率对PCB走线的阻抗值影响非常大。一般来说当数字信号边沿时间小于1ns或者模拟信号频率超过100M时就要考虑阻抗问题。

PCB走线阻抗主要来自寄生的电容、电阻、电感系数,主要因素有材料介电常数、线宽、线厚乃至焊盘的厚度等。PCB 阻抗的范围是25至120欧姆,USB、LVDS、HDMI、SATA、MIPI等一般要做85至100欧姆阻抗控制。

-

阻抗匹配技术:信号完整性与功率传输的基石2025-09-24 1444

-

技术资讯 I 信号完整性与阻抗匹配的关系2025-09-05 5339

-

PCB阻抗匹配过孔的多个因素你知道哪些?2024-07-04 3600

-

高速差分信号阻抗匹配详解2024-05-16 6992

-

什么是阻抗匹配?高速PCB设计为什么要控制阻抗匹配?2023-10-30 4197

-

为什么高频小信号谐振放大器中要考虑阻抗匹配?如何实现阻抗匹配?2023-10-11 3854

-

阻抗匹配的重要性及理想模型2023-07-04 2979

-

PCB设计中阻抗匹配的重要性2022-07-06 6232

-

PCB阻抗匹配的方法2020-11-02 4603

-

请问高速信号线为什么要阻抗匹配?2019-07-10 4583

-

阻抗匹配是什么意思_阻抗匹配原理详解2018-05-03 53891

-

高速PCB中的阻抗匹配2017-08-28 1788

-

什么是阻抗匹配以及为什么要阻抗匹配2015-10-28 1387

-

关于高速设计中的阻抗匹配的问题2010-03-15 1694

全部0条评论

快来发表一下你的评论吧 !