systemverilog:logic比reg更有优势?

电子说

1.4w人已加入

描述

在systemverilog协议中,logic定义四态值,即向量(vector)的每个位(bit)可以是逻辑0, 1, Z或X,与verilog协议中的reg很接近。但是logic有个很明显的优势,不允许多驱动。

多驱动对关键字logic而言是语法错误,在VCS编译阶段就能够发现,能够更早得发现错误。

而在Verilog协议中,并没有强调reg是不允许多驱的,因此VCS等编译工具不会主动报错。

需要在spyglass lint才能检查出来,或者通过VCS 仿真发现。

在芯片设计中,更早的暴露问题一直是设计和验证人员追求的目标,因此在RTL编码时,如果正常设计是不允许多驱动的场景中,建议使用logic替代reg。

如下案例中:cfg_mode 被多驱动,在实际项目设计中,多驱动的问题往往更加隐蔽,更不容易发现。

module try_top (

input clk , //

input rst_n , //

input [1:0] cfg_mode_in //

);

logic [1:0] cfg_mode ;

always_ff@(posedge clk, negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

always_ff@(posedge clk, negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

endmodule

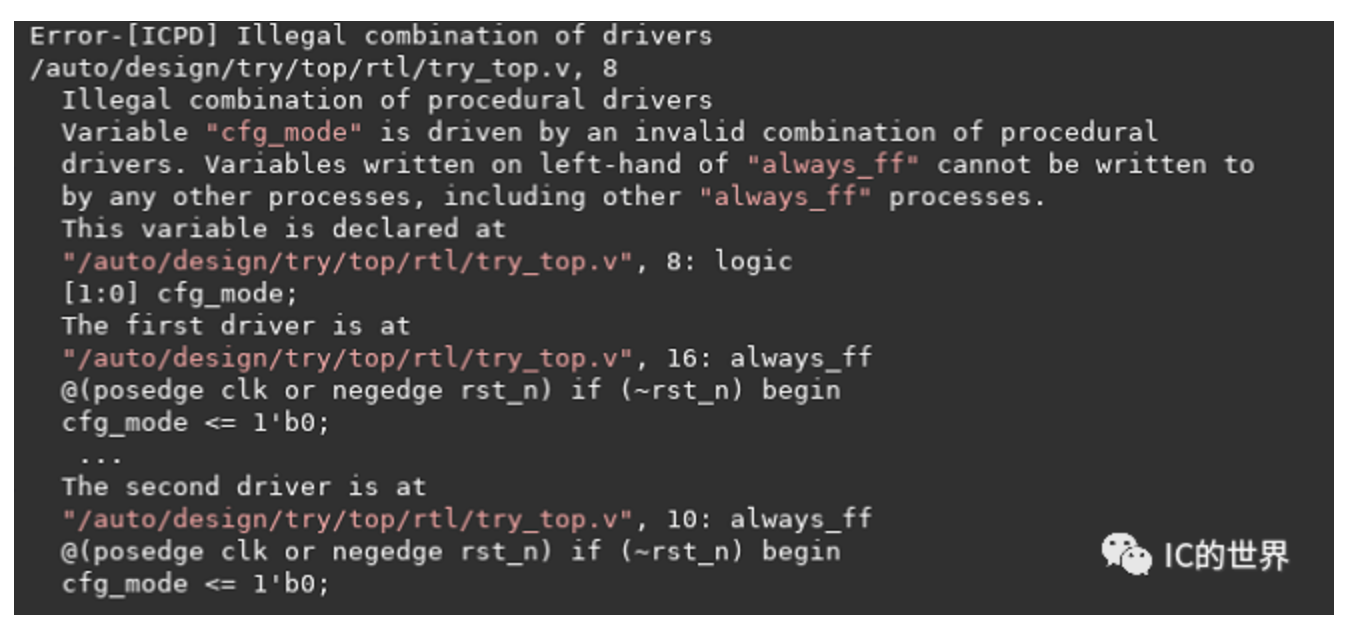

VCS报错:

如下案例中:cfg_mode 被多驱动,但是申明成reg类型,因此VCS不会报ERROR。

module try_top (

input clk , //

input rst_n , //

input [1:0] cfg_mode_in //

);

reg [1:0] cfg_mode ;

always@(posedge clk or negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

always@(posedge clk or negedge rst_n)

if(~rst_n)

cfg_mode <= 1'b0;

else

cfg_mode <= cfg_mode_in;

endmodule

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

systemverilog:logic比reg更有优势2023-10-26 2512

-

SystemVerilog在硬件设计部分有哪些优势2023-10-19 2511

-

数字硬件建模SystemVerilog之Interface方法概述2023-04-28 4570

-

SystemVerilog的正式验证和混合验证2021-03-29 932

-

噪声频谱密度(NSD)比信噪比(SNR)更有用?2021-03-05 3946

-

使用SystemVerilog来简化FPGA中接口的连接方式2021-01-08 1906

-

是否有更好的方法来存储比reg [100,000:0] val更有效的大值2019-02-15 1330

-

systemverilog学习教程2015-04-01 8657

-

[启芯公开课] SystemVerilog for Verification2013-06-10 8957

-

SystemVerilog学习一 —— 计数器2012-02-21 4488

-

SystemVerilog Assertion Handbo2009-07-22 1064

全部0条评论

快来发表一下你的评论吧 !