看一下SystemVerilog中package的使用方法与注意事项

描述

谈到package,用过VHDL的工程师并不陌生。实际上,SystemVerilog中的package正是从VHDL引入的,以进一步增强其在系统级的描述能力。我们来看一下SystemVerilog中package的使用方法与注意事项。 SystemVerilog中的package需要在关键字package和endpackage之间进行定义,其包含的内容可以是parameter,localparam,const,typedef,task,function,import,export和time unit。当然,package中也可以包含一些不可综合的用于验证的内容如class。

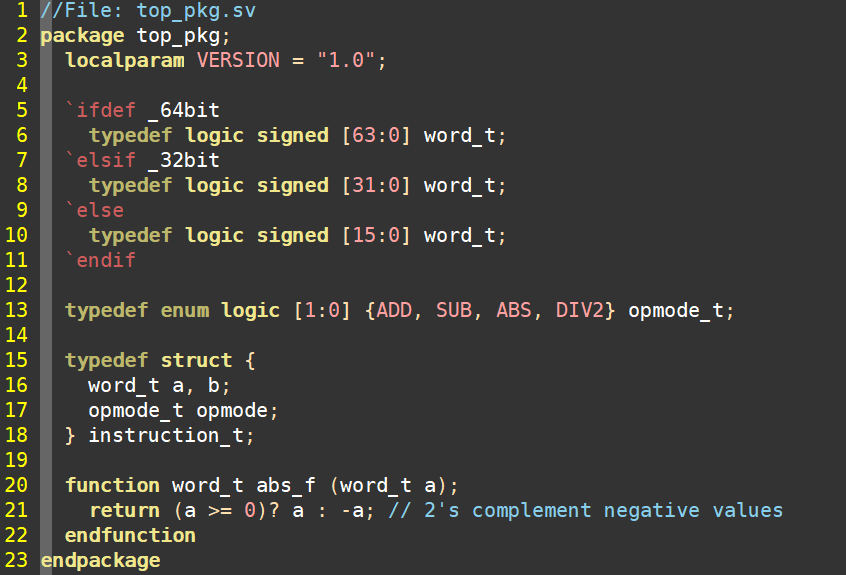

我们来看一个具体的例子,如下图所示代码片段。代码第2行通过关键字package表明其描述类别,package之后的top_pkg是package的名字。代码第5行至第11行以条件编译的方式结合typedef定义了数据类型。代码第13行通过typedef enum定义了枚举类型。代码第15行到第18行通过typedefstruct定义了结构体。代码第20行至第22行定义了function。代码第23行以endpackage确定package结束。

从可综合的SystemVerilog代码风格角度而言,需要注意:对于需要定义在package中的常数,应采用localparam或const定义,而不要使用parameter定义。此外,结构体应定义在package中,而不是以独立的.sv文件存在。

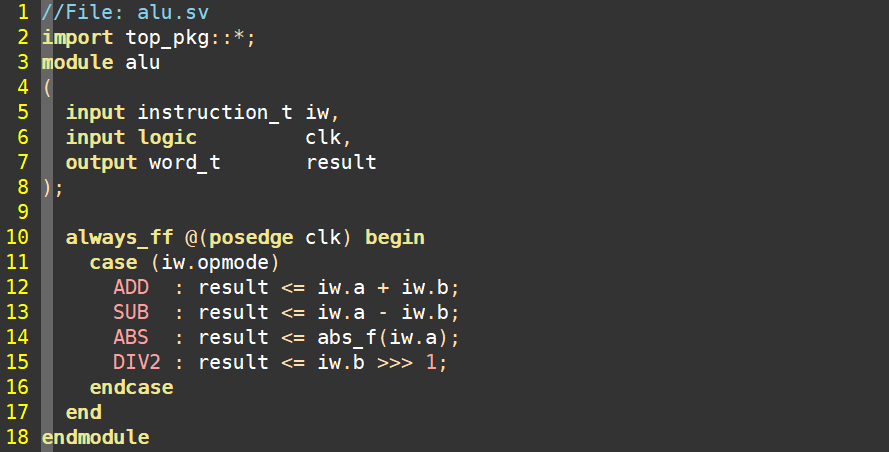

当需要使用package中的对象时,就需要导入package,如下图所示代码片段。代码第2行通过import导入package。“*”表示导入top_pkg中的所有内容。也可以只导入需要使用的package中的某个具体内容,例如

import top_pkg::word_t;

如果使用此方法导入用户定义的枚举类型时,需要明确导入使用到的枚举标签,如下所示:

import top_pkg::ADD;

import top_pkg::SUB;

import top_pkg::ABS;

import top_pkg::DIV2;

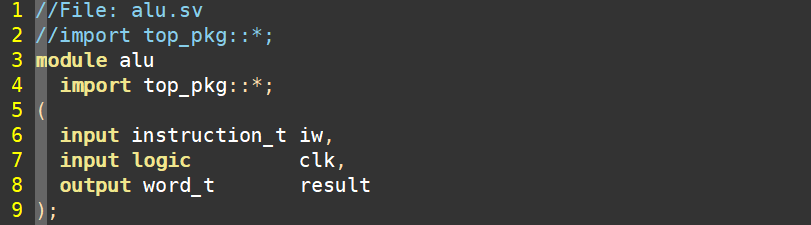

import package可以放在module声明之前,如上图所示代码第2行的位置,也可以放在端口声明之前,如下图所示代码片段的第4行。两者的效果是一样的,即:端口声明部分和module内的语句均可使用导入的package内容。

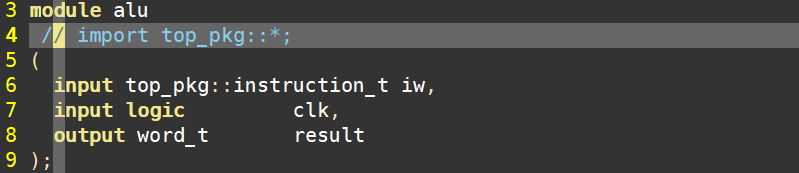

尽管可以使用如下图所示代码片段第6行所示方式,但实际工程中并不建议这么使用,这会导致代码变得冗长。工程实践表明,采用类似于“importtop_pkg::*;”的方式更为方便,也更为明了。

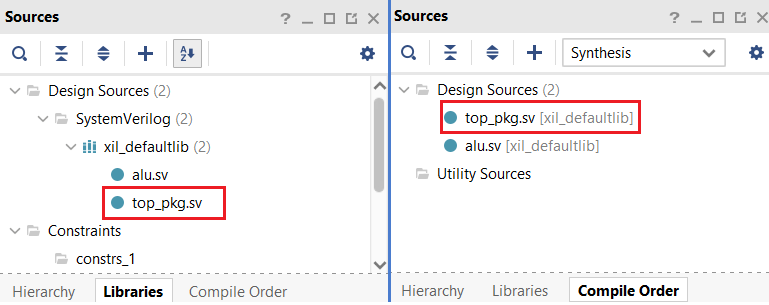

Vivado是支持package的。只需将package单独定义在一个后缀为.sv的文件中即可。Vivado会自动将package放在首位进行编译,如下图所示。

审核编辑:刘清

-

防雷元器件的使用方法及使用注意事项2009-12-09 2186

-

信号发生器的使用方法及注意事项2016-02-19 4589

-

大电流发生器使用方法和注意事项2019-05-05 3746

-

视频展台的典型使用方法/注意事项2010-02-08 1701

-

摇表的接线和使用方法及注意事项2011-01-28 21319

-

额温计的使用方法图解及使用注意事项2020-02-27 56681

-

浅谈压力传感器的使用方法及注意事项2021-03-10 1800

-

PCB承载大电流的操作方法和注意事项2023-07-26 3261

-

java中equals()方法的注意事项2023-11-17 1862

-

射频电缆组件的使用方法和注意事项2024-01-05 1866

-

锡膏的使用方法及注意事项2024-03-26 5642

-

数字万用表的使用方法和注意事项2024-05-07 2557

-

钳形电流表的使用方法和注意事项2024-05-14 8358

-

现场总线的使用方法与注意事项2024-06-06 2317

-

光纤收发器的使用方法和注意事项2024-08-26 4031

全部0条评论

快来发表一下你的评论吧 !