MMCU/PLL时钟约束导致的问题调试笔记

描述

Vivado2019.1/win10

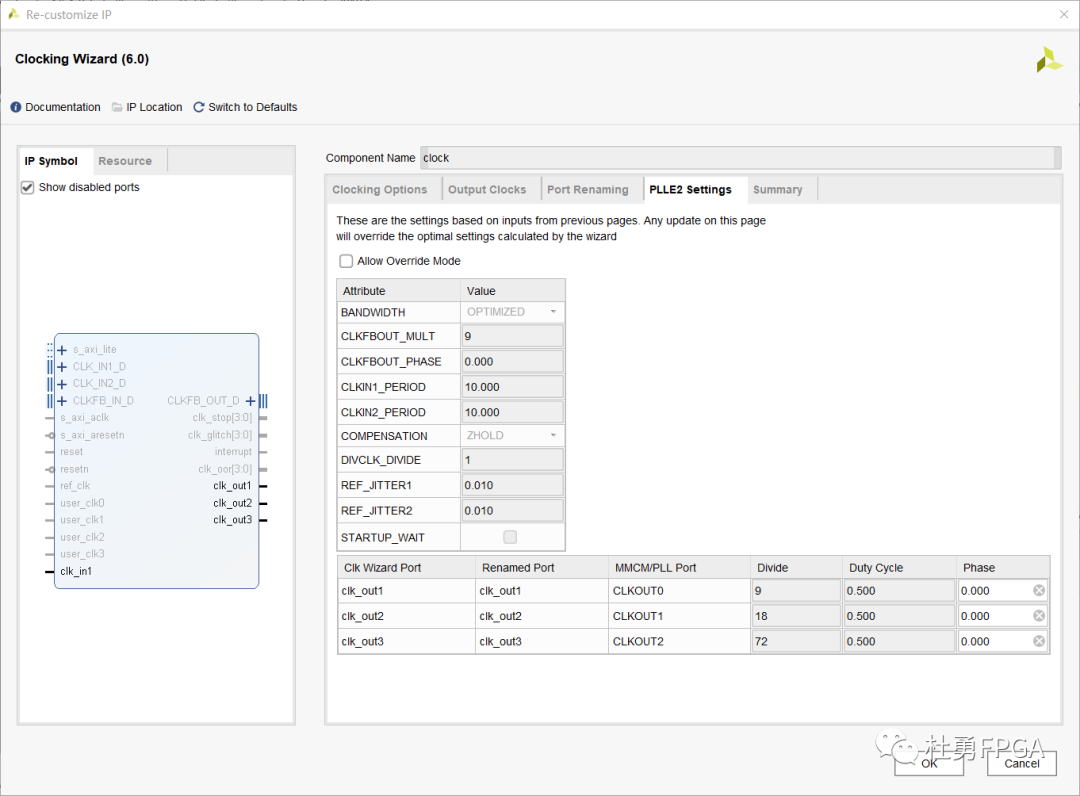

调用MMCU产生时钟,输入时钟频率为100M,产生100M、50M、12.5M时钟输出,MMCU核自动生成的时钟倍频数为9,即主时钟为900M,分别分频9得100M,18得50M,72得12.5M。

在约束文件中,设置了输入时钟的频率为50M。

create_clock -period 20 [get_ports gclk]。

实现程序时报错:

[DRC PDRC-43] PLL_adv_ClkFrequency_div_no_dclk: The computed value 450.000 MHz (CLKIN1_PERIOD, net gclk_IBUF) for the VCO operating frequency of the PLLE2_ADV site PLLE2_ADV_X0Y0 (cell u0/inst/plle2_adv_inst) falls outside the operating range of the PLL VCO frequency for this device (800.000 - 1866.000 MHz). The computed value is (CLKFBOUT_MULT_F * 1000 / (CLKINx_PERIOD * DIVCLK_DIVIDE)). Please adjust either the input period CLKINx_PERIOD (20.000000), multiplication factor CLKFBOUT_MULT_F (9) or the division factor DIVCLK_DIVIDE (1), in order to achieve a VCO frequency within the rated operating range for this device.

错误信息提示,主时钟根据计算为450M,不在VCO的工作范围内(800-1866M),需要调整倍频因子。

原因:

IP核设置的参数中输入时钟为100M,主时钟为900M(倍频因子为9),但约束文件中设置的输入时钟为50M。程序实现时,IP核的输入时钟频率竟然会按约束文件中的参数运算。

解决方案:

修改约束文件

create_clock -period 10 [get_ports gclk]。

IP核设置多少,时序约束就设置多少,可避免此类问题。

审核编辑:刘清

-

KUN-TC35调试笔记1.02023-11-17 432

-

RK3588-MIPI屏幕调试笔记:RK3588-MIPI-DSI2023-06-10 8305

-

电源调试笔记2021-12-31 791

-

调试笔记--keil 测量周期小技巧2021-12-01 929

-

S32K14x系列MCU时钟调试笔记相关资料推荐2021-11-26 1236

-

小白求助,求ADS1118的调试笔记2021-11-18 1692

-

调试笔记--keil 测量周期小技巧 相关资料分享2021-07-01 887

-

PSFB调试笔记分享!2019-07-25 2172

-

基于KUN-TC35调试笔记2017-10-16 788

-

ARM入门调试笔记2017-10-13 809

-

阿南《AT91SAM7S64调试笔记》2017-01-08 1548

-

IIC总线调试笔记2015-12-16 6079

-

ARM调试 AT91SAM7S64调试笔记2011-08-18 1642

-

AT91SAM7S64调试笔记2009-10-31 3025

全部0条评论

快来发表一下你的评论吧 !