FPGA设计中的模块化设计

可编程逻辑

描述

模块化设计是FPGA设计中一个很重要的技巧,它能够使一个大型设计的分工协作、仿真测试更加容易,代码维护或升级也更加便利。

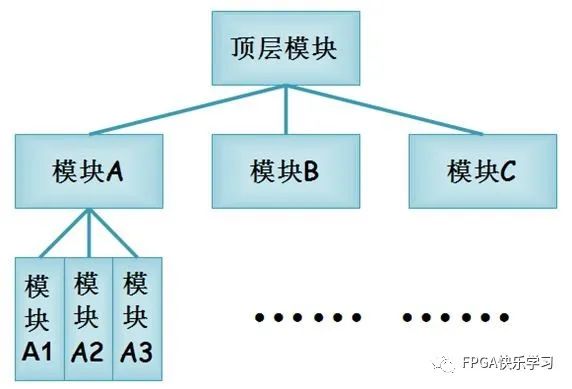

如图3.28所示,一般整个设计工程的顶层文件里只做例化,不做逻辑处理。顶层模块下会包含多个子模块,比如图中的模块A、模块B、模块C等等,而模块A、B、C下又可以再为分多个子模块实现,如A模块可以包含子模块A1、A2和A3等。

图3.28 模块设计示意图

采用模块化的设计,就可以将大规模复杂系统按照一定规则划分成若干模块,然后对每个模块分别进行设计输入、综合与实现,并将实现结果约束在预先设置好的区域内,最后将所有模块的实现结果进行整合集成,就能完成整个系统的设计。

模块化设计的实现一般包含以下步骤。

●初始预算,本阶段是实现步骤的第一步,对整个模块化设计起着指导性的作用。在初始预算阶段,项目管理者需要为设计的整体进行位置布局,只有布局合理,才能够在最大程度上体现模块化设计的优势;反之,如果因布局不合理而在较后的阶段需要再次进行初始预算,则需要对整个实现步骤全面返工。

●子模块的设计实现,在该阶段,每个项目成员并行完成各自子模块的实现。

●模块的最终集成,在该阶段项目管理者将顶层的实现结果和所有子模块的实现结果进行整合集成,完成整个设计的实现。

模块划分的基本原则是:各个子模块的功能相对独立,模块内部联系尽量紧密,模块间的连接尽量简单。对于那些难以满足模块划分准则的具有强内部关联的复杂设计,并不适合采用模块化设计方法。

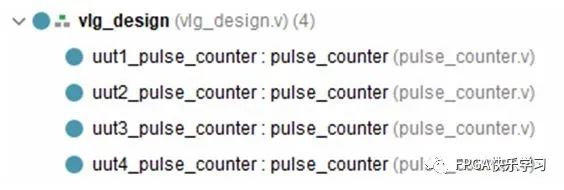

以工程note10_prj004为例,我们用模块复用的方式,在顶层模块vlg_design.v下定义了4个子模块uut1_pulse_counter.v、uut2_pulse_counter.v、uut3_pulse_counter.v和uut4_pulse_counter.v,这4个子模块虽然代码一样,都是pulse_counter.v这个模块的代码,但是由于引到顶层模块的接口信号不同,所以它们最终实现了4个完全独立的模块,即4个完全相同的硬件电路。

图3.29 代码的模块化层次视图

顶层模块vlg_design.v中没有逻辑处理的代码,只有子模块的例化和接口的连接。代码如下。

module vlg_design(

input i_clk,

input i_rst_n,

input[3:0]i_pulse,

input i_en,

output[15:0]o_pulse_cnt1,o_pulse_cnt2,

output[15:0]o_pulse_cnt3,o_pulse_cnt4

);

pulse_counter uut1_pulse_counter(

.i_clk (i_clk),

.i_rst_n (i_rst_n),

.i_pulse (i_pulse[0]),

.i_en (i_en),

.o_pulse_cnt (o_pulse_cnt1)

);

pulse_counter uut2_pulse_counter(

.i_clk (i_clk),

.i_rst_n (i_rst_n),

.i_pulse (i_pulse[1]),

.i_en (i_en),

.o_pulse_cnt (o_pulse_cnt2)

);

pulse_counter uut3_pulse_counter(

.i_clk (i_clk),

.i_rst_n (i_rst_n),

.i_pulse (i_pulse[2]),

.i_en (i_en),

.o_pulse_cnt (o_pulse_cnt3)

);

pulse_counter uut4_pulse_counter(

.i_clk (i_clk),

.i_rst_n (i_rst_n),

.i_pulse (i_pulse[3]),

.i_en (i_en),

.o_pulse_cnt (o_pulse_cnt4)

);

endmodule

下面是对pulse_counter.v模块的例化代码。

pulse_counter uut1_pulse_counter(

.i_clk (i_clk),

.i_rst_n (i_rst_n),

.i_pulse (i_pulse[0]),

.i_en (i_en),

.o_pulse_cnt (o_pulse_cnt1)

);

以上面这段代码为例,模块例化大体有下面几个要点:

● pulse_counter是原始工程源码本身的模块名称,同一个工程源码,可以多次被例化。

●uut1_pulse_counter的名称是可以随意起的,只要不和已有的名称重名即可,它表示我们对当前例化模块pulse_counter.v的唯一识别名。在这个工程中,我们看到pulse_counter.v模块被例化了多次,但它和uut1_pulse_counter对应位置的命名是不一样的,而且必须是不一样的,表示工程中有多个完全一样的功能模块。这和软件程序里面的调用不一样,软件程序由于运行起来总是串行的,所以多次调用同一个函数时,这个函数可以只占一个函数所需的物理存储空间即可;但是FPGA是并行处理的,它的模块例化,哪怕是完全一样的模块,往往也是需要多个完全一样的物理资源与其对应的。

●“. i_clk (i_clk),”是接口的映射,“.(),”是固定格式。点号后面的i_clk是pulse_counter.v模块内部的接口,括号内的i_clk是vlg_design.v模块的接口。

pulse_counter.v模块是具体的逻辑处理源码,其代码如下。

module pulse_counter(

input i_clk,

input i_rst_n,

input i_pulse,

input i_en,

output reg[15:0]o_pulse_cnt

);

reg[1:0] r_pulse;

wire w_rise_edge;

//////////////////////////////////////////

//脉冲边沿检测逻辑

always @(posedge i_clk)

if(!i_rst_n)r_pulse <= 2'b00;

else r_pulse<= {r_pulse[0],i_pulse};

assign w_rise_edge = r_pulse[0] & ~r_pulse[1];

//////////////////////////////////////////

//脉冲计数逻辑

always @(posedge i_clk)

if(i_en) begin

if(w_rise_edge)o_pulse_cnt <= o_pulse_cnt+1;

else/*o_pulse_cnt <= o_pulse_cnt*/;

end

elseo_pulse_cnt <= 'b0;

endmodule

审核编辑:刘清

-

模块化示波器的技术原理和应用2024-12-11 767

-

学fpga的verilog语言怎么模块化2013-11-21 1995

-

Xilinx FPGA入门连载25:PLL实例之模块化设计2015-11-18 4303

-

勇敢的芯伴你玩转Altera FPGA连载64:模块化设计概述2018-04-24 2331

-

玩转Zynq连载20——基于FPGA的模块化设计2019-08-31 3636

-

什么是模块化编程2021-12-06 1725

-

模块化Java:动态模块化2010-12-01 787

-

模块化FPGA设计在某雷达接收机中的应用2009-11-24 1204

-

基于模块化设计方法实现FPGA动态部分重构2010-08-23 1223

-

模块化程序设计2016-03-22 643

-

基于DSP和FPGA的模块化实时图像处理系统设计2017-10-23 1078

-

FPGA学习之模块化设计概述2018-05-02 7563

-

采用模块化设计实现基于FPGA的动态可重构功能2020-07-29 2799

-

FPGA模块化设计与AlteraHardCopy结构化ASIC2021-01-20 984

-

什么是模块化自动化?2023-03-10 3955

全部0条评论

快来发表一下你的评论吧 !