PLIC平台级中断控制器介绍

描述

平台级中断控制器(PLIC)

PLIC:Platform-Level Interrupt Controller.

实际上,除了CLINT管理的软件中断和定时器中断,其他的中断都是由PLIC管理的。

U54内核的平台级中断控制器 (PLIC) 最多可支持 132 个具有 7 个优先级的外部中断源。

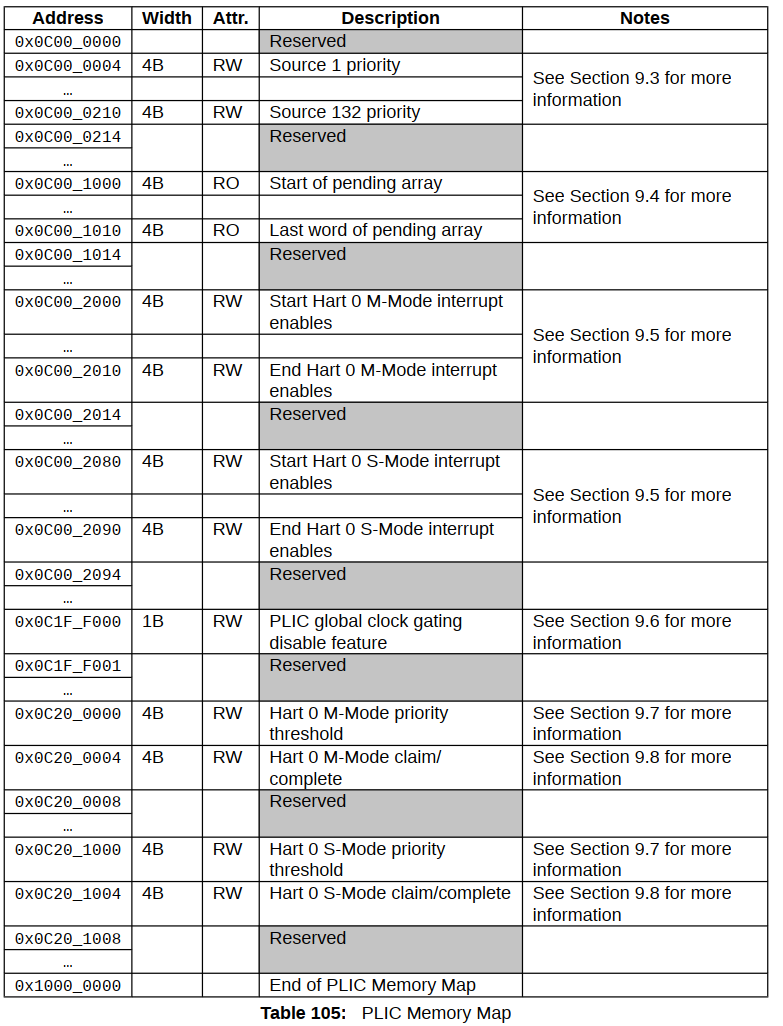

Memory Map

U54 内核 PLIC 控制寄存器的内存映射如表 105 所示。PLIC 内存映射仅支持对齐的 32 位内存访问。

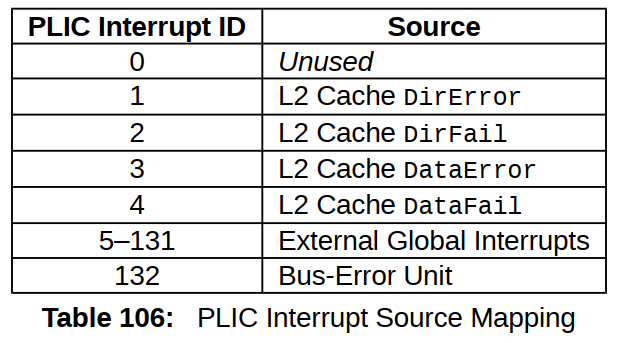

中断源

U54内核共有 132 个全局中断源,此外还有CLINT管理的 中描述的本地中断。

其中 127 个是外部全局中断,其余由表 106 中列出的各种片上设备驱动。表 106 描述了 U54 核心复合体上的全局中断源。

Note:在 RISC‑V 平台级中断控制器规范中,中断源 0 (ID 0) 未使用,因此第一个可用的 PLIC 中断 ID 的值为 1

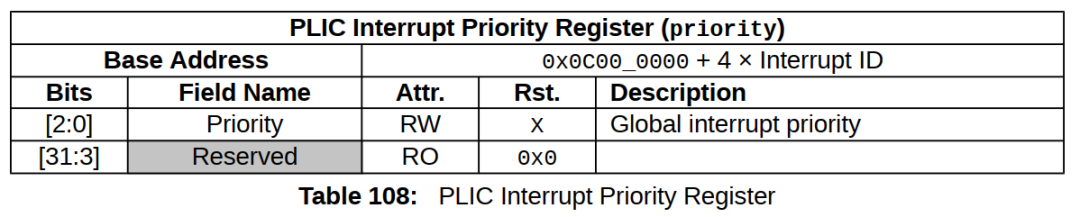

中断优先级

每个 PLIC 中断源都可以通过写入其 32 位内存映射优先级寄存器来分配优先级。

U54 内核支持 7 个优先级。保留优先级值 0 表示“永不中断”并有效地禁用中断。

优先级 1 是最低的活动优先级,优先级 7 是最高的。

相同优先级的全局中断之间的关系由中断 ID 打破;ID 最低的中断具有最高的有效优先级。相关寄存器信息如下:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

RISC-V怎么实现核间中断?核心本地中断控制器(CLINT)深度解析2025-12-13 2806

-

易灵思Sapphire SoC中RISC-V平台级中断控制器深度解析2025-11-08 8185

-

AS32X601驱动系列教程 PLIC_中断应用详解2025-05-23 861

-

中断控制器级联的类型有哪几种2023-09-28 1638

-

STM32外部中断控制器EXTI详解2023-04-20 4317

-

简要介绍配置嵌套向量中断控制器2022-02-22 935

-

细说STM32的中断控制器(NVIC)那些事2022-01-14 1235

-

NVIC嵌套向量中断控制器介绍2021-12-07 1324

-

中断控制器的驱动解析(上)2021-12-04 619

-

STM32的NVIC嵌套向量中断控制器与EXIT外部中断控制器介绍2021-11-16 2760

-

华芯微特MCU的嵌套向量中断控制器与外部中断/事件控制器的使用方法2021-06-04 4753

-

ARM的中断控制器2020-08-29 3900

-

一种多核处理器中断控制器的设计2017-01-07 1097

-

psoc1中断控制器2012-11-22 3506

全部0条评论

快来发表一下你的评论吧 !