车规模块系列(五):聊一聊DBB/铜绑定技术

描述

相比于之前的标准化模块封装,近年来各具特色的模块封装类型都慢慢映入眼帘,就好比之前我们聊到的DCM、HPD和TPAK等等。并且其中细节部分也有着不一样的改进,如DBB技术、Cu-Clip技术、激光焊接、SKiN、单/双面水冷、银烧结、铜烧结等等,无疑给模块封装技术增添了更多组合的可能,以应对不同的性价比和应用。

今天我们就来聊聊铜绑定,以一篇丹佛斯硅动力的一篇论文来看看这个工艺的特点。

DBB技术

AUTUMN IS COMING

相对于传统的铝绑定线工艺,铜绑定线需要对芯片表面进行要求更高的金属化,而丹佛斯键合缓冲Danfoss Bond Buffer (DBB)技术就是为了铜绑定线进行的表面处理。

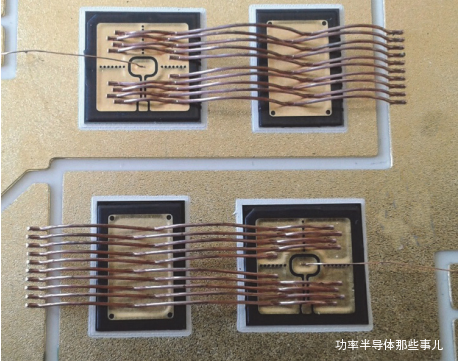

在模块生产制造过程中,在芯片顶部额外地烧结一层铜层,防止芯片在超声波焊接过程中开裂,提供了所需的机械粘接缓冲作用。芯片的顶部的铜层适合键合直径可达500um的铜线,同时,芯片的底部被烧结到DBC上,铜绑定和烧结技术的结合显著地提高可靠性以及功率密度。

DBB技术是为了减少CTE不匹配带来的热机械应力,除了在键合过程中吸收能量以及保护芯片,其还具有一定的热学优势。

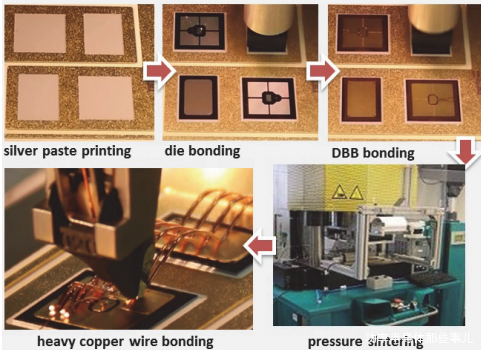

DBB的主要工艺步骤如下,

芯片烧结到DBC和芯片表面的DBB可以使用同一台烧结设备和工艺。下面是一个DBB技术模块的局部示意图,

上图中,DBC衬底和DBB铜层都有一层NiAu表面,以达到更好的延展性。

DBB中的铜层形成了一个热容量,对于模块的Zth有着一定的影响,但不会增加其热阻Rth。其大面积的铜层,以及铜层的厚度比普通的Al顶层要厚得多,导致了更好的电流扩散,提供了更为均匀的电流密度分布。

热特性

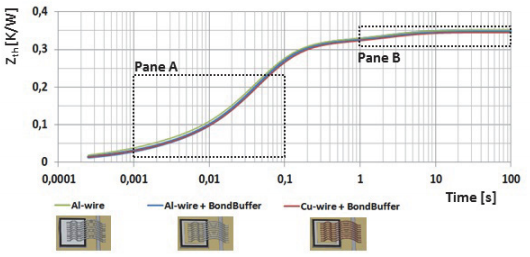

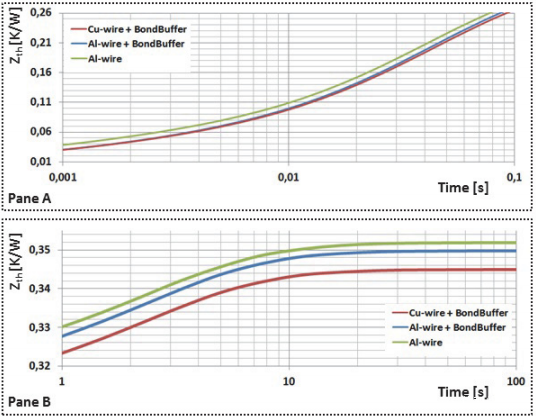

利用有限元仿真工具,在相同条件下对比了三种情况下的热参数,

缓冲层(70um)+铜绑定线(300um)

缓冲层(70um)+铝绑定线(300um)

无缓冲层+铝绑定线(300um)

热阻抗曲线如下,

PaneA中,在1ms处单纯Al线和缓冲层加Cu线热阻抗相差0.01K/W主要是由于铜线具有较高的热导率;PaneB中,纯Al线和缓冲层加Al线热阻差了约0.003K/W是由于缓冲层厚度较高引起的。

热机械应力

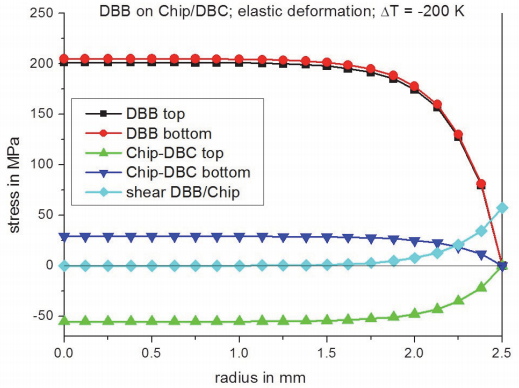

为了评估Si芯片和DBB铜层之间的银烧结层内的应力,采Suhir的轴对称模型,计算出了层状材料(顶层和底层)的弹性弯曲应力分布和连接层中的应力,即剪切应力。轴向对称近似矩形,其半径由边长的一半或者对角线来定义,或者通过使用等面积的方法。Suhir表明,大面积的剪切应力只存在于一定的外围区域,如下图中的曲线“剪切DBB/Chip”所示,在一定横向尺寸内保持不变。

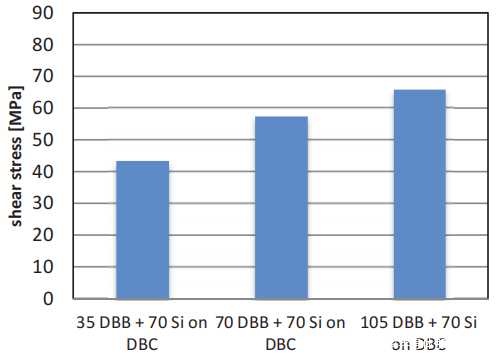

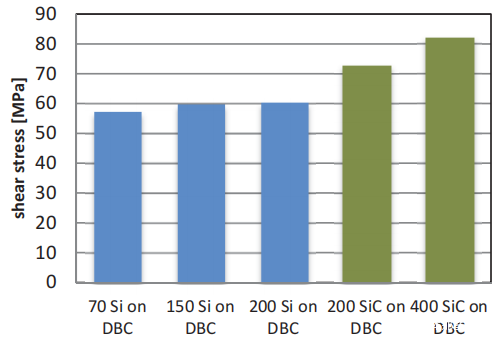

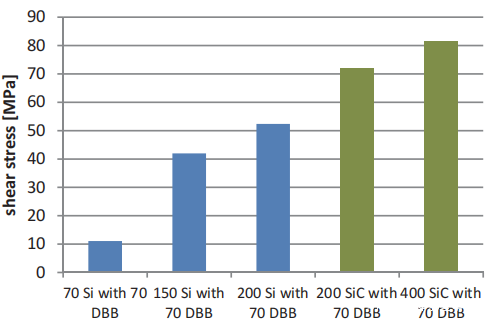

同时也给出了一些相关参数对剪切力的关系。

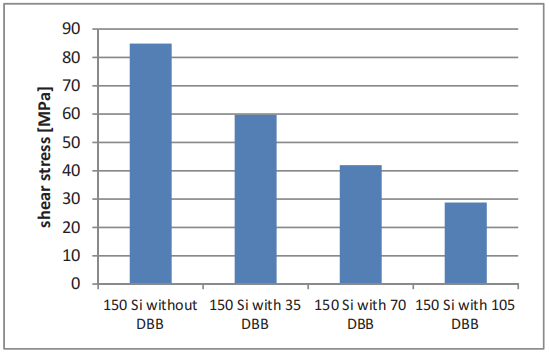

不同DBB厚度下,DBB烧结层的剪切应力与厚度成正相关性。

不同芯片厚度下,DBB烧结层的剪切应力与厚度成正相关,相同面积下,SiC大于Si。

不同芯片厚度下,芯片到DBC的烧结层剪切应力。可以看出芯片越薄,烧结层中的应力越低。

不同DBB铜层厚度下,芯片到DBC的烧结层的剪切应力。可以看出,DBB越厚,芯片到DBC的烧结层剪切应力越小,但需要结合第一个柱状图,DBB越厚,DBB烧结层的剪切应力越大。这两种需要进行相应的权衡。

TC和PC循环

TC测试在-40/+150℃,15/15min下进行,给到了开始前和750次循环后的SAM图像,

可以看出,烧结层都没有变化迹象,而DBC的铜层明显有损伤,此时DBC的可靠性成了木桶效应的短板。

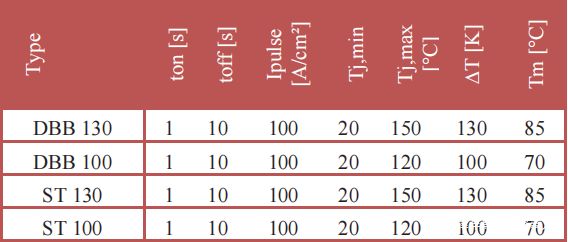

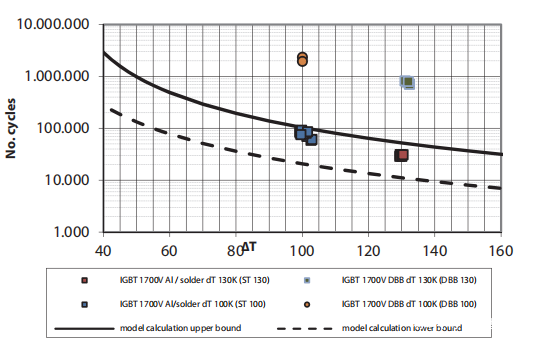

PC测试基于100A/1700V的IGBT进行,分别有DBB技术和传统的铝绑定线加焊接(ST)的样品,测试条件如下,

可见采用DBB技术的功率循环能力得到了飞跃的提升。

小结

今天以DBB技术为基础,大致聊了一下铜绑定线带来的一些优势,当然归根结底还是为了更高的功率密度和可靠性。但功率半导体没有一个过程是固定不变的,都是在反反复复的折中过程中寻找着属于自己的最优解,DBB技术是一种,那相信其他家的铜绑定或者Cu-Clip都有属于自己模块的最优解。

审核编辑:刘清

-

聊一聊消息队列技术选型的7种消息场景2023-12-09 2315

-

聊一聊7系列FPGA的供电部分2021-11-11 1872

-

聊一聊英飞凌DSC(双面水冷)的车规模块2023-10-30 2685

-

简单聊一聊DPT技术-double pattern technology2023-12-05 4477

全部0条评论

快来发表一下你的评论吧 !