半导体行业产生深远影响的定律:摩尔定律!

描述

这节我们将为大家介绍一个对半导体行业产生深远影响的定律:也就是大名鼎鼎的摩尔定律!

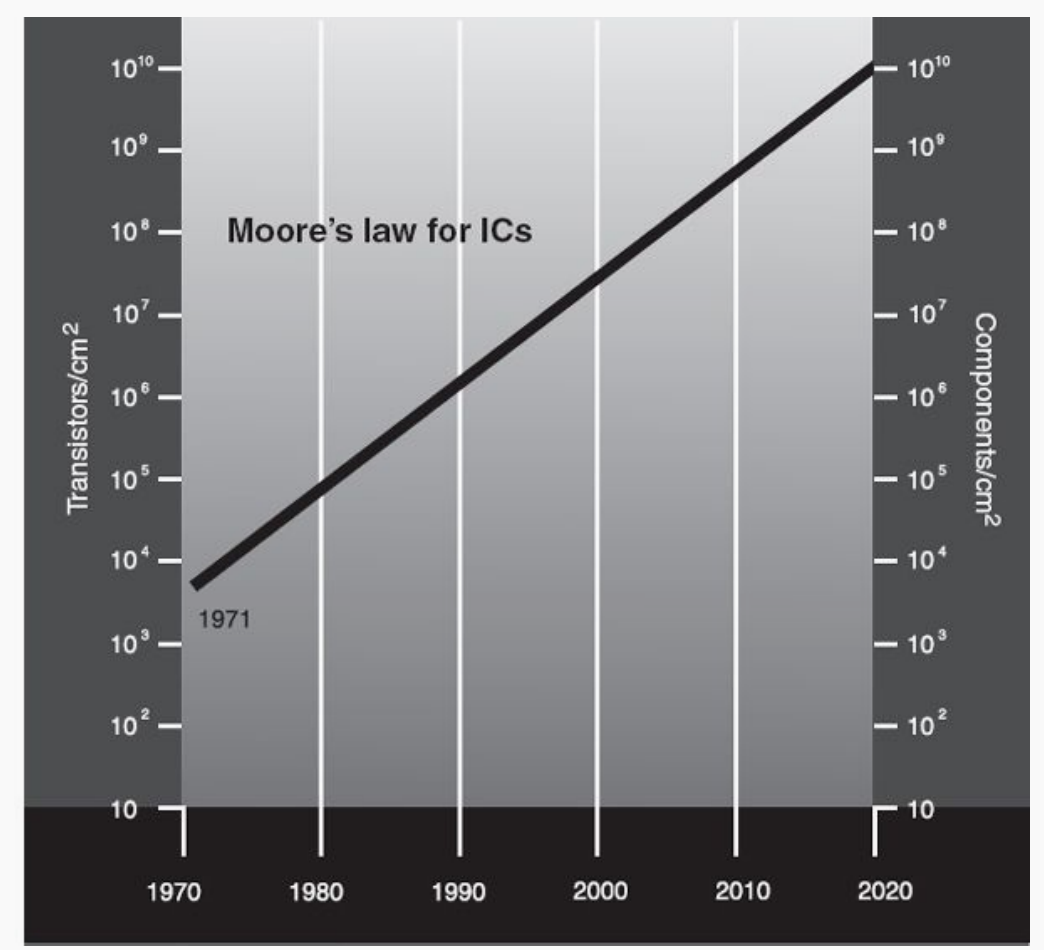

1965年,英特尔创始人戈登·摩尔(Gordon Moore)注意到,芯片上的晶体管数量每年都在翻倍。他发表了这一观察结果,并立即被称为摩尔定律。他将规律更新为每两年翻一番。行业观察人士利用这一定律来预测未来芯片的密度。多年来,它已被证明是非常准确的,现在正在推动技术进步。如果这是真的,芯片上的晶体管数量将达到数十亿(如下图所示)。它是由半导体工业协会(SIA)制定的国际半导体技术路线图(ITRS)的基础。

有人猜测芯片密度可能会超过摩尔定律的预测。佐治亚理工学院的微系统封装研究指出,2004年每平方厘米约有50个组件,到2020年,组件密度将攀升至每平方厘米约100万个组件。

芯片中元件密度的持续增加确实遵循了摩尔定律。还有一种讨论认为,该行业现在已经将摩尔定律作为芯片密度和提高性能的未来驱动力(目标)。这些目标嵌入在最新版的国际半导体技术路线图,如2011年版。

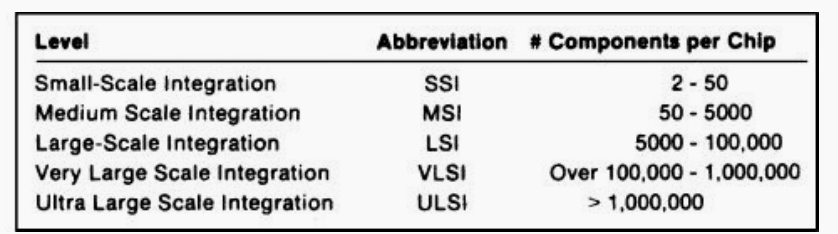

电路密度由集成度水平这个指标来进行跟踪,集成水平指的是一个电路中所包含元件的数量。集成级别(如下图所示)范围从小规模集成(SSI)到超大规模集成(ULSI)。ULSI芯片有时被称为超级大规模集成(VVLSI)。大众媒体称这些最新产品为巨型芯片。

除了集成规模之外,存储电路还通过电路中包含的存储位的数量来识别(一个4兆的存储芯片可以存储400万位的内存)。逻辑电路通常按其所具有的门的数目来定级。门是逻辑电路的基本操作元件。

逐渐减小的特征图形尺寸

2023 National Day

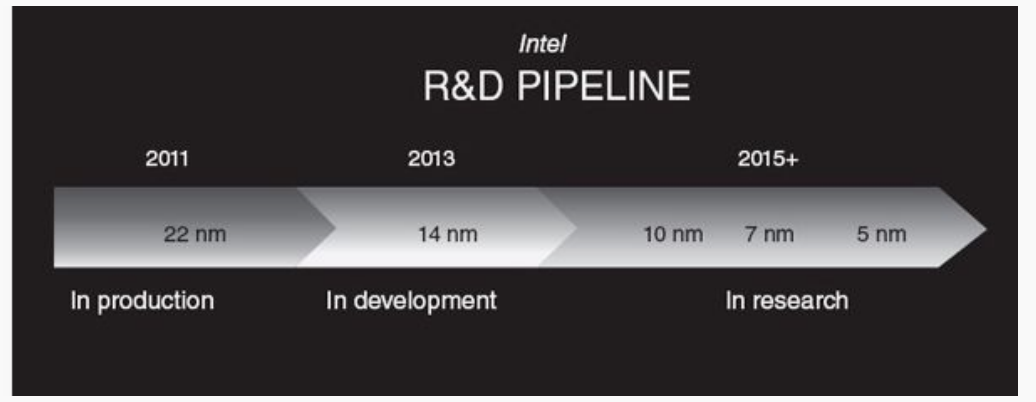

从小规模集成电路逐渐发展到今天的超大规模集成电路芯片的历程主要是由单个组件的特征尺寸减小所驱动的。这种特征尺寸的减少是由于成像工艺的急剧进步所推动的,这一点可以深刻阐释:科技是发展的第一生产力这句真理。这些技术包含光刻技术,以及多层导体集成技术。半导体工业协会曾经预测,到2016年,特征尺寸将减少到22纳米(0.0022 μm)。随着芯片上的组件更小的能力带来的好处是使它们更紧密地聚集在一起,进一步增加密度(如下图中所示)。

用来解释这些趋势的一个类比是单户住宅社区的布局。社区的密度是房屋大小地块大小和街道宽度的函数。容纳更多的人口可以通过增加社区的规模(增加芯片面积)来实现。另一种可能性是缩小单个房屋的大小,将它们放在较小的地块上。我们也可以减少街道的面积来增加密度。然而,在某种程度上,街道不能再缩小,否则它们将不够宽的汽车。此外,在某种程度上,房屋不能进一步缩小,仍然作为住宅单位使用。在这一点上,一个选择是通过建造多层高速公路和/或用公寓楼取代个人住宅来进行建设。所有这些概念都用于半导体技术。

-

摩尔定律时代落幕,半导体行业何去何从?2016-02-22 1308

-

摩尔定律死去,半导体怎么办?2016-05-23 1774

-

所谓的后摩尔定律时代,IC业者面临什么挑战?2017-02-06 7041

-

什么是摩尔定律?2023-08-05 7304

-

晶圆和摩尔定律有什么关系?2011-12-01 5900

-

介绍28 nm创新技术,超越摩尔定律2012-08-13 2591

-

半导体行业的里程碑“摩尔定律”竟是这样来的2016-07-14 4194

-

摩尔定律推动了整个半导体行业的变革2019-07-01 4377

-

摩尔定律在测试领域有哪些应用?2021-04-13 2215

-

请问摩尔定律死不死?2021-06-17 1891

-

摩尔定律,摩尔定律是什么意思2010-02-26 1813

-

摩尔定律_摩尔定律是什么2012-05-21 2845

-

摩尔定律是什么_摩尔定律提出者及含义2018-03-09 32483

-

摩尔定律已过时?谁还能撑起芯片的天下?2023-05-18 1500

-

摩尔定律是什么 影响了我们哪些方面2025-01-07 3279

全部0条评论

快来发表一下你的评论吧 !