如何使用Power Design Manager(PDM)进行功耗评估?

描述

一、前言

在基于FPGA和 SoC器件的产品设计过程中,从器件选择到系统级电源设计、散热设计,电源功率估算对于设计方案确定至关重要;早期进行极端情况下的功耗分析,可以帮助用户产品避免进入系统电源、散热设计过度或设计不足的陷阱。从Xilinx Power Estimator (XPE)工具问世以来,一直都是领先的FPGA 电源估算工具;但是随着 FPGA、MPSoC 以及Versal ACAP 器件的逻辑容量、复杂性不断增加,XPE工具面临如下一些挑战:

A. 只支持Windows操作系统;

B. XPE工具使用Microsoft Excel和宏来计算功率,Microsoft安全更新可能导致宏或ActiveX控件在Excel中停止工作;

C. FPGA器件的逻辑容量、复杂性增加,功耗估算需要复杂的决策和计算,Excel中宏的运行速度慢;

为应对上述挑战,需要对电源估算工具功能进行升级,支持大型复杂器件架构,提高功耗估算的运行速度,支持更多操作系统。

二、PDM工具介绍

Power Design Manager (PDM) 是 AMD 的全新一代电源估算平台,旨在为 Versal™ 和 Kria™ SOM 产品带来精确、一致的电源估算性能。PDM有如下特性:

A. 为 Versal 器件带来了更高的速度和稳定性;

B. 支持 Versal AI Core 系列、Prime 系列、Premium 系列、AI Edge 系列和 HBM 系列;

C. 支持 Kria K26 SOM 和Kria KV260 入门套件;

D. 面向硬件特定电气和热约束的全新 Export XDC 向导,用于 Vivado® ML 版本电源设计和热预算管理;

E. 支持 Windows 及 Linux 操作系统;

F. 支持XPE迁移到PDM;

PDM的首次公开发布是在2022.2年,在2023.1版本中,PDM可以使用统一安装程序进行单独安装,不需要安装完整的Vivado工具,PDM是一个独立的工具,不依赖Vivado。

PDM最新版本是2023.1.2,有单独的安装软件包,可以独立下载安装,不需要license。

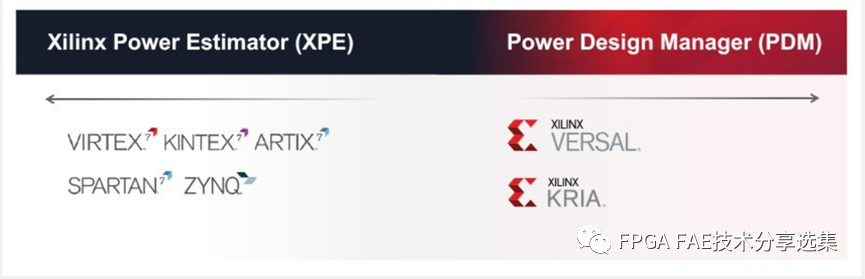

XPE将继续支持 Versal 产品系列之前的所有产品系列,新的器件将仅在PDM中得到支持,例如,Versal HBM、Versal Edge。

三、PDM设计步骤

PDM支持两种设计流程:手工流程和导入流程。手工流程要求工程师手动输入各种参数,如时钟频率、翻转率、各类资源使用量以及使用模式等。导入模式可直接导入.xpe文件用于功耗评估,与XPE工具导入.xpe文件操作类似;.xpe文件可以是XPE工具导出文件,也可以是Vivado IDE生成的.xpe文件。

手工流程设计方法如下:

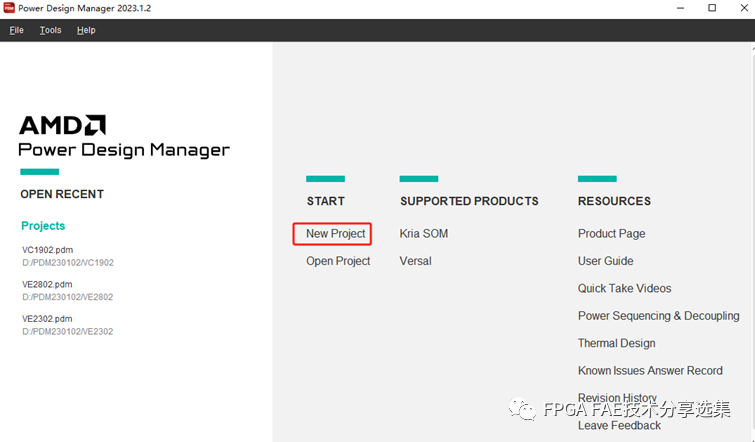

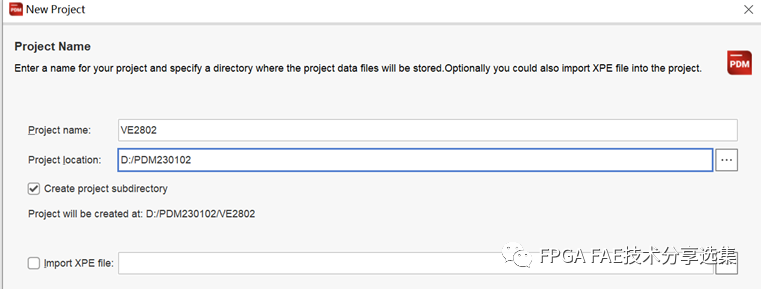

1. 建立工程

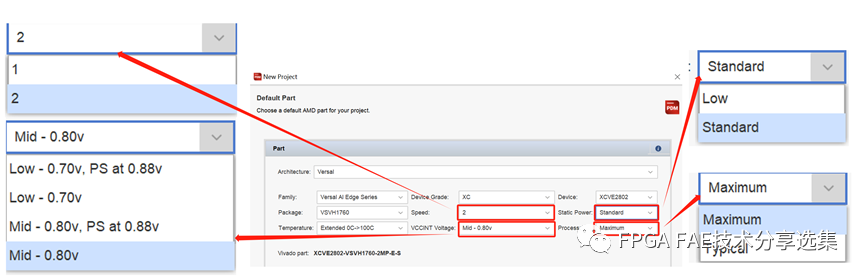

2. 器件选择

选择器件型号与实际使用器件一致;VCCINT电压越高,功耗越高;Static Power为 Low的器件,静态功耗低;如果按照最严苛情况功率估算,Process设置为Maximum。

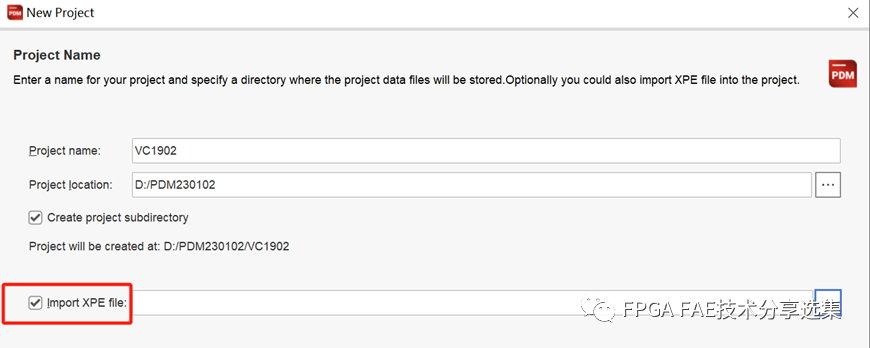

导入流程设计方法如下:

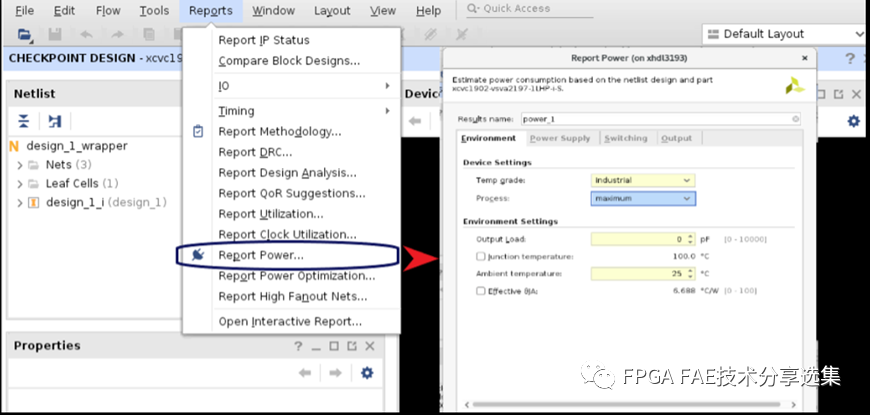

使用现有的.xpe文件,或者从Vivado中导出.xpe文件,下图是Vivado中导出.xpe文件的操作示意图。

点击下图位置中的import.xpe按钮,选择.xpe文件目录进行导入。

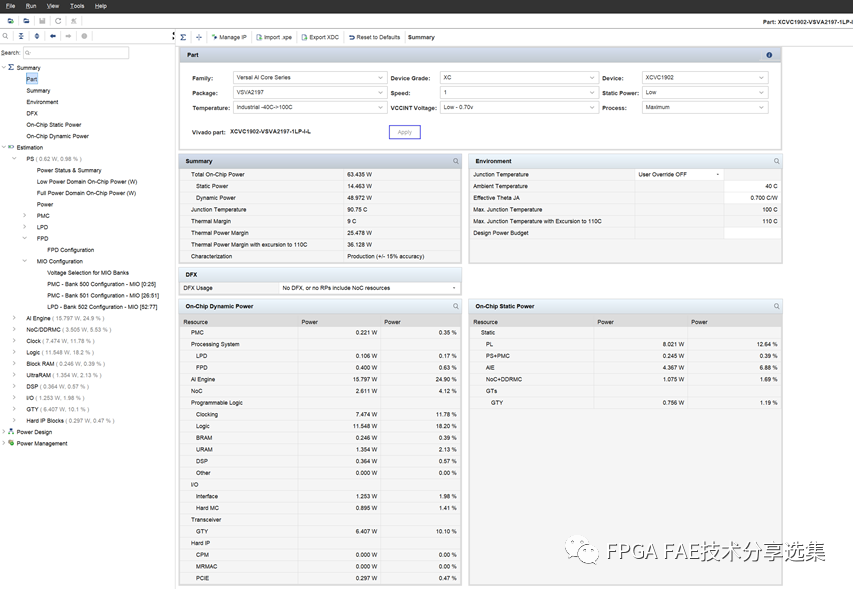

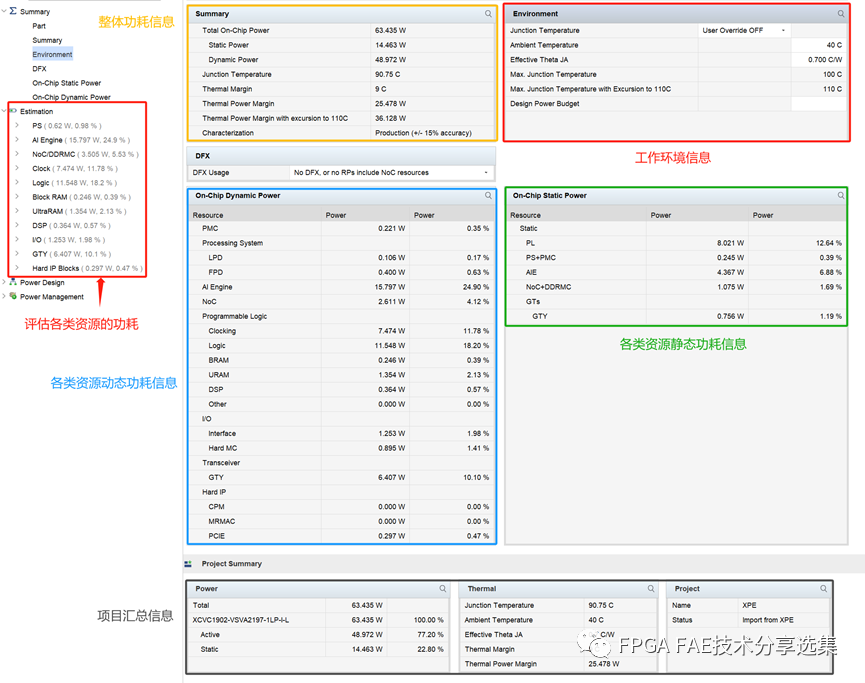

导入成功后,进入下面界面。

四、功耗评估实例

工作环境参数设置

工作环境参数设置非常重要,动态功率随结温呈指数增长。在工作环境信息框中,设置产品的工作环境温度、目标结温或者effective Theta JA参数,通过热模拟或实际系统测量可以获取有效的effective Theta JA参数。PDM会根据设置的参数计算出结温和功耗,计算的结温超过器件温度等级限制或者计算的功耗超过设置的功耗值,PDM会发出警报。

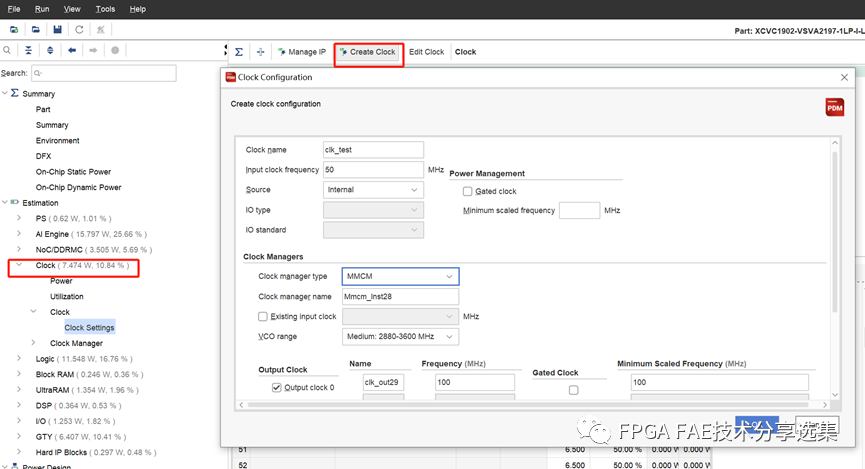

时钟设置

选中界面中左侧clock选项,再选中界面中右侧上方 creat clock 按钮,使用clock config wizard进行添加clk 设置操作,设置完成后,点击ok,生成clk_test、clk_out29两个时钟网络。

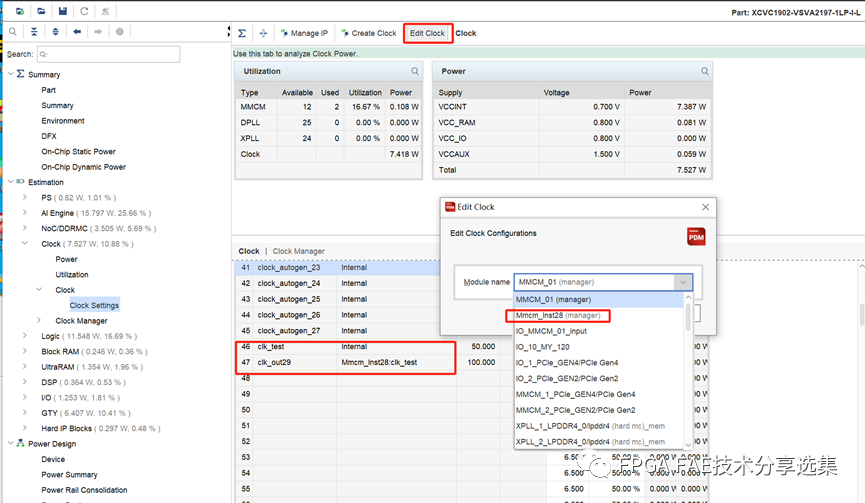

选中界面中右侧上方Edit clock 按钮,使用edit clock wizard,可以对已经生成的时钟网络进行编辑,可以从这里删除不需要的时钟网络。完成时钟配置后,可以观察到相关的电源的功耗。

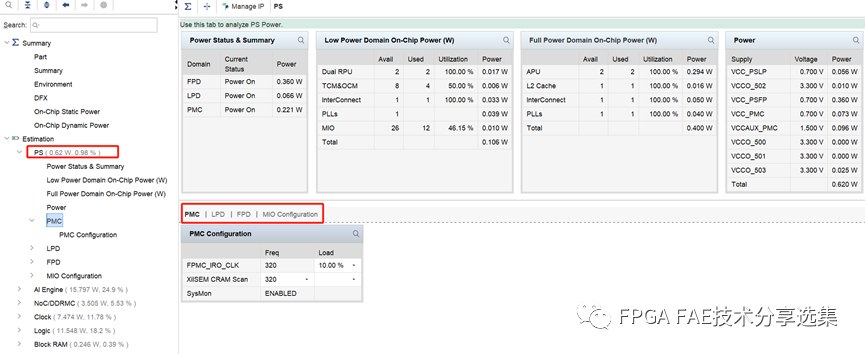

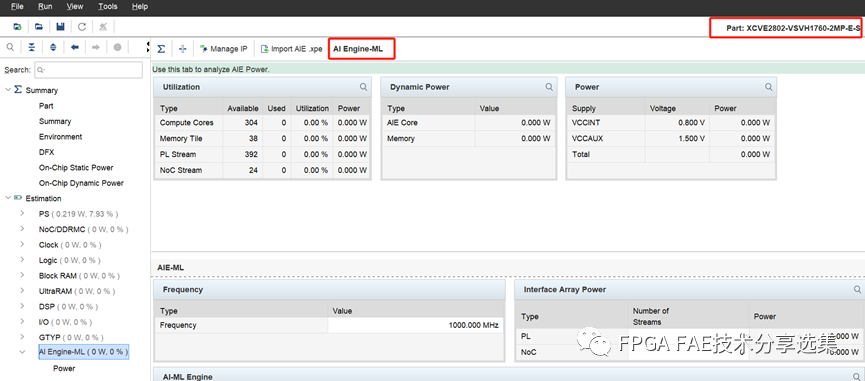

PS系统功耗计算

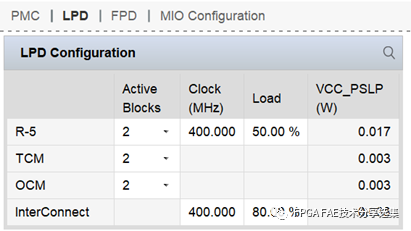

PS系统的功率估算分为LPD、FPD、PMC 3个区域,分别点击PMC、LPD、FPD、MIO Config按钮,设置参数,MIO 部分的功耗计入LPD区域。完成PS系统配置后,可以观察到相关的电源的功耗。

PMC区域:

LPD 区域:

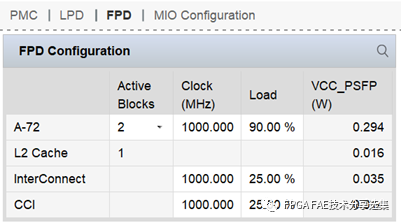

FPD区域:

MIO Config:

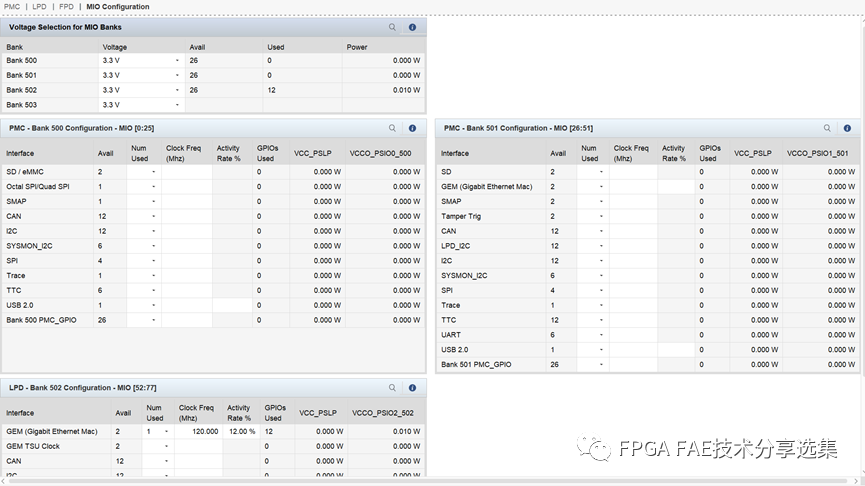

AI Engine功耗计算

AI Engine(AIE)在Versal ai Core系列和一些Versal ai Edge、Versal Premium 器件中使用。计算功耗时,需要提供Al Engine阵列的时钟频率、 AIE数量、数据类型、Vector Load信息。可以使用import流程,导入Vitis软件平台生成的.xpe文件,为Al Engine功耗估计提供准确的信息。

.xpe文件导入后,将生成所有配置,与手动输入模式相比,可以更准确地估计功率。AIE的时钟在-3速度等级的器件中,最高可以支持1300MHZ,设置值超出所选器件AIE支持的时钟速率,PDM会报警提示, AIE功耗计算界面还提供PL和NoC接口的数量及其对应的功耗信息。完成AIE配置后,可以观察到相关的电源的功耗。

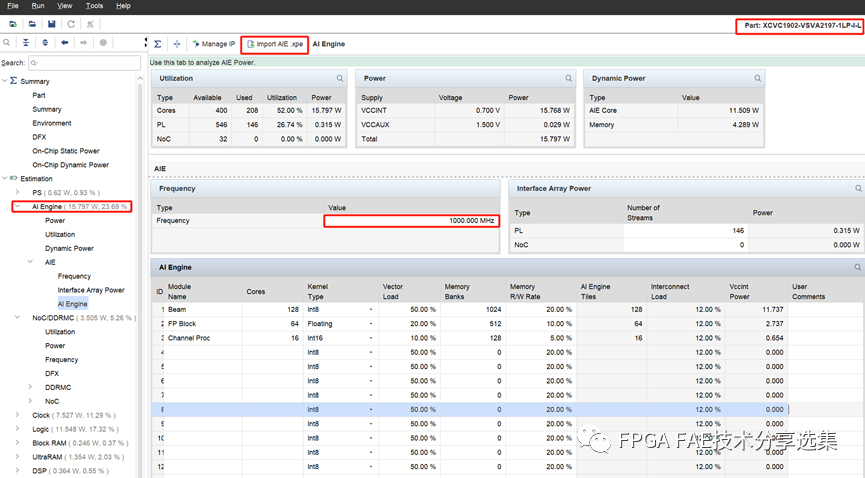

AI Engine-ML 功耗计算

AI Engine-ML (AIE-ML) 在Versal ai Edge系列和一些Versal ai Core器件中使用,AIE-ML基于AlE进行优化,支持BFloat 数据类型,功耗估算设置与AIE类似。

NOC/DDRMC /HBMMC功耗计算

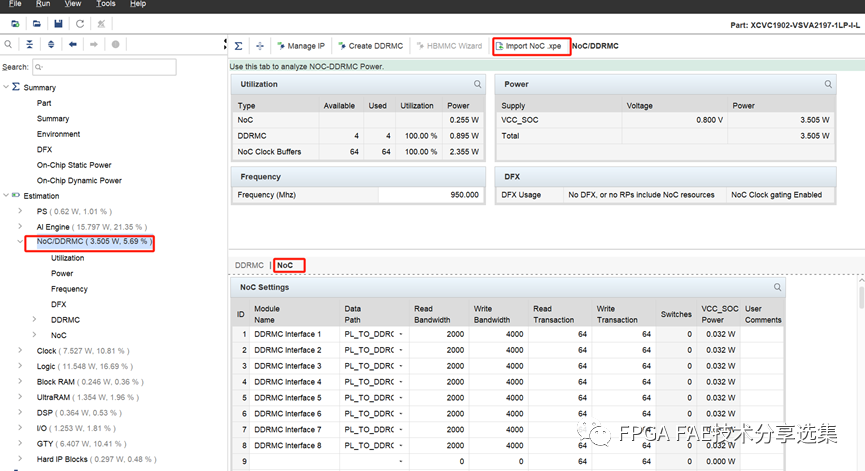

Network-On-Chip(NOC)是versal器件中的连接硬块,它用更窄的高速网络提供PMC、DDRMC、HBM、CPM、PL、Al Engine和PS之间的连接,并为其接口的模块提供配置功能。支持直接手动输入和.xpe文件导入两种方式配置,手动输入点击界面下方的Noc按钮,在界面信息中直接输入配置信息,.xpe文件导入时,选择界面上方的import Noc.xpe按钮,.xpe文件由Vivado软件生成。

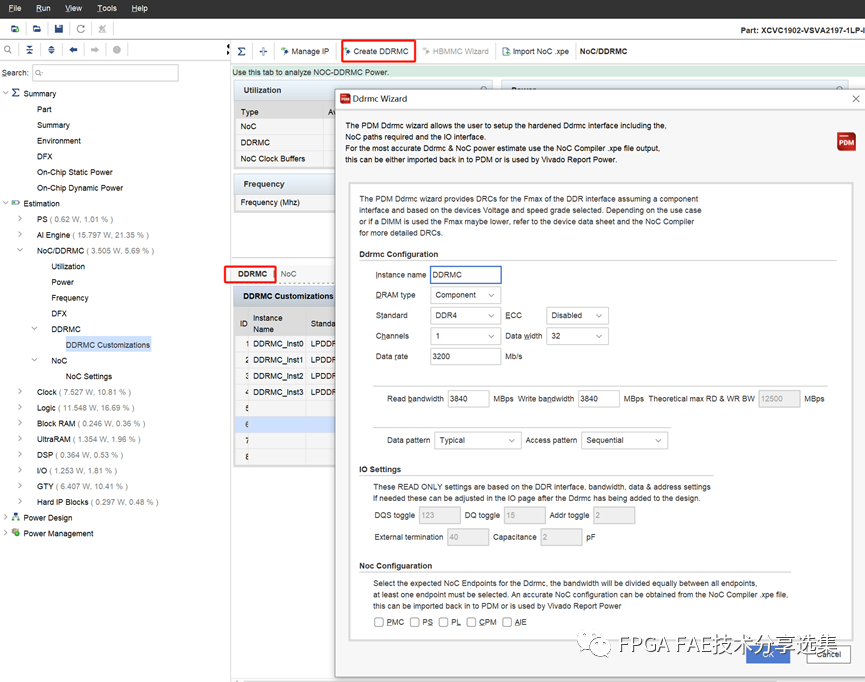

通过DDRMC wizard进行DDRMC设置,点击界面上方的Create DDRMC 按钮进入配置界面,在DDRMC wizard中完成参数设置后,参数会保存到DDRMC的信息栏中。

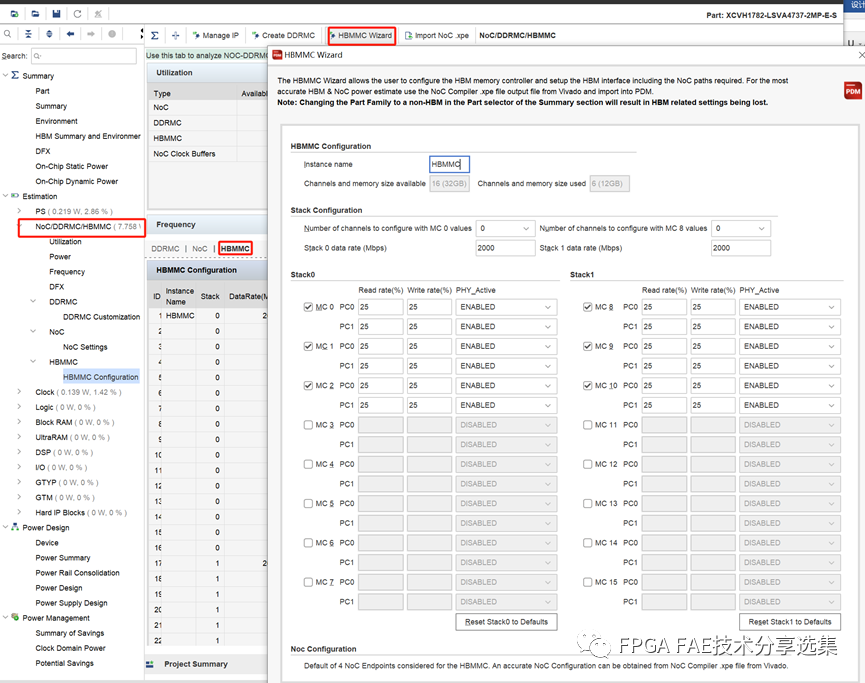

High Bandwidth Memory (HBM)在Versal HBM系列器件中使用,点击界面上方的HBMMC Wizard 按钮进入配置界面,在HBMMC Wizard中完成参数设置后,参数会保存到HBMMC的信息栏中。

完成NOC/DDRMC /HBMMC配置后,可以观察到各自相关的电源的功耗。

参照上述方法,进入Logic、Block RAM 、UltraRAM 、DSP 、I/O、GTY、GTYP、GTM、Hard IP Blocks各个界面进行参数设置,设置完成后,PDM会计算出对应的功耗。

五、结语

PDM是下一代功率估算工具,比上一代XPE功率估算工具更快,更准确,PDM有一个更稳定、更易于使用的界面。本文简单介绍使用PDM进行Versal 器件功耗评估的流程和方法,PDM工具详细的使用方法,参照UG1556。

审核编辑:刘清

-

关于低功耗蓝牙连接功耗的评估2025-04-26 559

-

SWITCH POWER SUPPLY DESIGN2012-08-16 2046

-

Low_Power_Design2013-05-13 1878

-

[UPF]低功耗(Low Power Design)and UPF介紹 精选资料分享2021-07-27 2348

-

gnome-power-manager的工作原理是什么2022-01-03 870

-

power design 下载2008-06-27 566

-

The Design of Power Line in Hi2009-03-24 1081

-

Switching USB Power Manager wi2009-09-30 891

-

THERMAL DESIGN OF POWER MOSFET2009-11-29 629

-

PADS Design Archive Manager的功能实现2019-05-21 4200

-

Power System Manager和Super Sequencer选择指南2021-04-20 912

-

Xilinx推出了新一代功耗评估工具:PDM2022-10-27 5424

-

Power Design Manager (PDM) 2023.1的新增功能2023-09-06 1916

-

AMD Power Design Manager 2025.1现已推出2025-07-09 1397

-

AMD Power Design Manager 2025.2版本现已发布2025-12-24 801

全部0条评论

快来发表一下你的评论吧 !