高级数字IC设计之灰度转二值化设计

EDA/IC设计

1078人已加入

描述

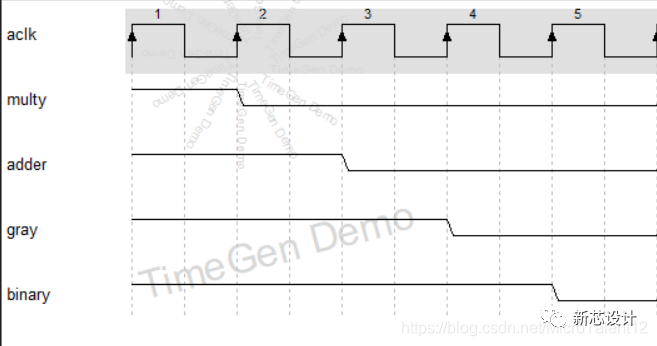

这是一个能够成功上板实现的灰度转二值的 Verilog 程序设计,详细的数据延时与信号延时如下所示:

首先是输入 RGB 数据信号在第一个时钟上升沿到来的时候,开始从前级的模块输入到后级的模块。 此时,乘法打一拍、加法打一拍、灰度打一拍、二值打一拍。

这样,经过一系列操作,直到最终的二值输出,中间经历了 **4 **个时钟的延时。因此,行场同步控制信号也需要 4 个时钟的延时来和 RGB 数据同步。

RTL 代码

module Gray_Binary(

input wire aclk,

input wire aresetn,

input wire [23:0] rgb,

input wire i_h_sync,

input wire i_v_sync,

output reg binary,

output reg o_h_sync,

output reg o_v_sync

);

reg [15:0] multy1,multy2,multy3;

reg [15:0] adder;

reg [7:0] gray;

wire [7:0] i_r_8b;

wire [7:0] i_g_8b;

wire [7:0] i_b_8b;

assign i_r_8b = rgb[23:16];

assign i_g_8b = rgb[15:8];

assign i_b_8b = rgb[7:0];

reg i_h_sync_delay_1;

reg i_h_sync_delay_2;

reg i_h_sync_delay_3;

reg i_v_sync_delay_1;

reg i_v_sync_delay_2;

reg i_v_sync_delay_3;

always @(posedge aclk)begin

multy1 <= i_r_8b * 8'd76;

multy2 <= i_g_8b * 8'd150;

multy3 <= i_b_8b * 8'd30;

end

always @(posedge aclk)begin

adder <= multy1 + multy2 + multy3;

end

always @(posedge aclk)begin

gray <= adder[15:8];

end

always @(posedge aclk)begin

binary <= (gray< 8'd58)?1'b1:1'b0;

end

always @(posedge aclk or negedge aresetn) begin

if(!aresetn)begin

i_h_sync_delay_1<=0;

i_h_sync_delay_2<=0;

i_h_sync_delay_3<=0;

i_v_sync_delay_1<=0;

i_v_sync_delay_2<=0;

i_v_sync_delay_3<=0;

end

else begin

i_h_sync_delay_1 <= i_h_sync;

i_h_sync_delay_2 <= i_h_sync_delay_1;

i_h_sync_delay_3 <= i_h_sync_delay_2;

o_h_sync <= i_h_sync_delay_3;

i_v_sync_delay_1 <= i_v_sync;

i_v_sync_delay_2 <= i_v_sync_delay_1;

i_v_sync_delay_3 <= i_v_sync_delay_2;

o_v_sync <= i_v_sync_delay_3;

end

end

endmodule

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

视觉分析中,二值化与灰度图片的数据传导问题2024-04-08 5568

-

DSP教学实验箱_数字图像处理操作_案例分享:5-13 灰度图像二值化2024-07-25 14315

-

使用Otsu阈值算法将灰度图像二值化2025-10-28 188

-

labview中怎么把USB采集的图像输入到灰度处理 二值化等模块...2014-09-05 2696

-

经典教材Verilog HDL高级数字设计(第二版)习题答案2016-04-27 24304

-

高级数字IC设计工程师-成都 上海 广州 武汉 深圳2017-07-13 1778

-

Verilog HDL 高级数字设计源码2018-02-02 6428

-

基于灰度直方图和谱聚类的文本图像二值化方法2009-10-29 691

-

图像处理之图像的灰度变换2018-09-15 11035

-

如何使用STM32F103进行二值化及灰度化处理程序免费下载2018-09-25 2313

-

SRM32单片机图像处理(灰度化、二值化)及直线识别2021-11-19 1471

全部0条评论

快来发表一下你的评论吧 !