基于32位RISC-V CPU架构的Trikarenos微控制器

控制/MCU

描述

地球上使用的电子设备很少能够在离开地球舒适的大气层后幸存下来。特别是处理器的设计必须能够承受外太空的恶劣条件,包括辐射和接近绝对零的温度。RISC-V 似乎可以帮助解决这一挑战。

瑞士公立大学苏黎世联邦理工学院的研究人员开发了 Trikarenos,这是一种基于 RISC-V 的微控制器,旨在在太空等恶劣环境中可靠运行。Trikarenos 可以承受辐射引起的单粒子扰乱 (SEU),这是由单个电离粒子引起的微电子设备状态的变化。此外,它可以提供与传统“太空芯片”相当的性能水平,而消耗的能量仅为相同能源预算的一小部分。

传统上,这个问题是通过使用在旧工艺节点上开发的辐射硬化芯片来解决的。老化的基于 PowerPC 的 BAE RAD750 就是一个典型的例子。该芯片于 2001 年推出,采用 250 纳米工艺节点制造,二十年后该芯片仍在使用,并执行了无数次飞行任务,并为好奇号和毅力号火星车以及詹姆斯网络太空望远镜提供动力。

研究人员解释说,针对太空条件的常见对策通常依赖于专有的抗辐射技术、低密度制造节点和广泛的复制。这些因素导致成本高、性能和效率低。Trikarenos 旨在通过台积电提供的 32 位 RISC-V CPU 架构和“先进”28nm 制造技术来应对这些挑战。

研究人员表示,28 纳米节点已展现出对辐射引起的 SEU 事件“破坏性影响”的恢复能力,并且与之前的设计相比,它提供了前所未有的效率水平。Trikarenos 采用超低功耗PULPissimo微控制器架构,该架构是开源的,就像 RISC-V CPU 架构一样。

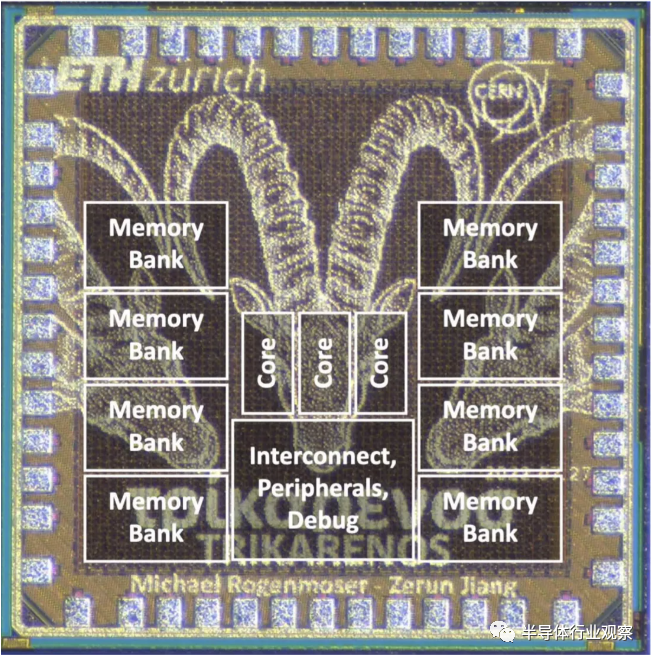

该芯片包含三个基于 RISC-V 的 Ibex 计算核心,每个核心的时钟速度高达 270 MHz,并由 8 个 SRAM 组提供数据,每个 SRAM 组有 256 KB 的内存。这三个核心以“三核锁步”配置运行,其中每个核心同时执行相同的操作。如果 SEU 事件损坏其中一个核心,则类似于少数派报告中描述的投票将确定正确的操作输出。

旨在增强辐射耐受性的其他架构元素包括集成冗余、纠错存储体以及连续读取每个内存地址以纠正任何可纠正错误的“内存清理器”。此外,三个 Ibex 核心在物理上由每个核心周围 20 微米的间隙隔开。这很重要,因为设计人员需要确保单个粒子撞击不会影响两个独立核心上的类似元素。

三核设计提供了更高的容错能力,但可能会影响控制器的潜在性能。尽管如此,该设计似乎能够提供与基于 PowerPC 的 RAD750 芯片相当的性能水平,该芯片已经使用了二十年,并且仍然被主要航天机构用于执行最复杂的任务,例如詹姆斯·韦伯太空望远镜。未来几年,NASA 打算用SiFive 设计的高性能 RISC-V CPU 取代 RAD750 。

与功耗为 5 瓦的 RAD750 相比,Trikarenos 只需 15.7 毫瓦即可实现相同的计算结果,这使其有利于 CubeSat 卫星发射等能源受限的任务。如果不需要极高的可靠性,三个内核可以并行运行,提供三核锁步设计 300% 的性能。

如上所述,苏黎世联邦理工学院并不是第一个提出基于 RISC-V 的航天部件的机构。去年,我们了解到SiFive 的 RISC-V 兼容 CPU 内核将为 NASA 的高性能航天计算机 (HPSC) 提供动力。

该计算机系统是与 SiFive 和 Microchip 合作开发的,合同为期三年,价值 5000 万美元。完成后,该部件预计将成为航天局未来载人和无人任务的支柱。

不过,与 Trikarenos 相比,HPSC 的威力要强不少。据 SiFive 称,与它所取代的 RAD750 相比,该部件的性能将提高 100 倍。据说该芯片具有 12 个核心,其中 8 个基于 SiFive 的 X280 矢量处理器设计,以及 4 个通用核心。

编辑:黄飞

-

risc-v与esp32架构对比分析2024-09-26 1525

-

RISC-V内核的32位通用微控制器 GD32VF103芯片简介2024-10-23 687

-

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究2020-07-27 4364

-

科普RISC-V生态架构(认识RISC-V)2020-08-02 6964

-

基于 RISC-V 的微控制器入门指南2020-08-21 2391

-

RISC-V指令集架构微控制器相关知识2021-12-16 1448

-

【RISC-V专题】国产首创RISC-V安全微控制器CF3310开发板免费试用2022-04-14 3735

-

CH573集成BLE的32位RISC-V内核微控制器2022-12-26 856

-

RISC-V架构2023-04-03 2012

-

两大架构RISC-V 和 ARM 的各种关系2023-06-21 1287

-

RISC-V是什么?如何基于此设计微控制器2020-10-30 1184

-

Raven基于PicoRV32内核的RISC-V微控制器2022-12-13 960

-

一文解析x86、ARM、RISC-V、CPU处理器微架构2023-04-08 4950

-

瑞萨电子推出采用自研CPU内核的通用32位RISC-V微控制器2024-03-29 1429

-

瑞萨电子推出业界首款自研通用型32位RISC-V MCU内核2024-05-17 2192

全部0条评论

快来发表一下你的评论吧 !