YTM32的模数转换器ADC外设模块详解

电子说

描述

简介

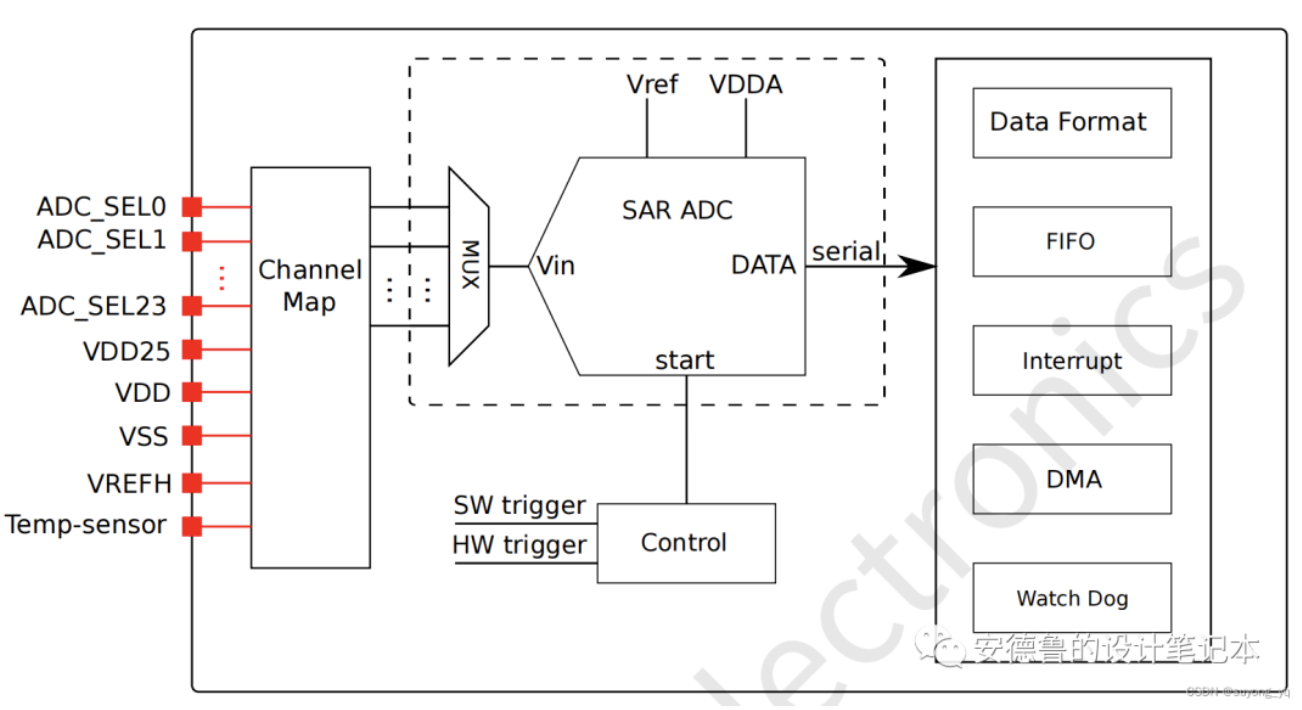

YTM32的ADC转换器外设最多可以集成32个输入通道,最高12b转换精度,最快可以支持2M Sps的12b采样。ADC转换器外设内部的主要结构,如图x所示,包括ADC输入通道复用器、ADC转换器、FIFO等。

图x ADC外设模块框图

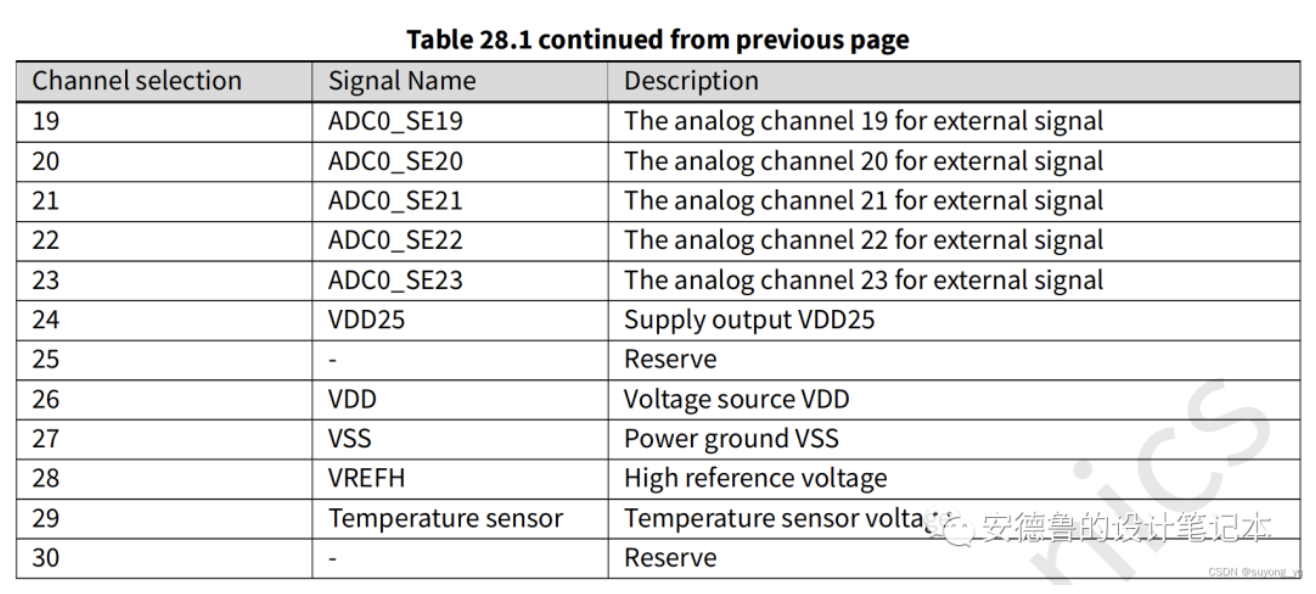

YTM32B1ME上集成了两个ADC转换器,每个转换器实际仅对外开放了24个输入通道,并且ADC0还在芯片内部绑定了若干采样点(所谓的external channel)。如图x所示。

图x ADC在芯片内部绑定的采样信号

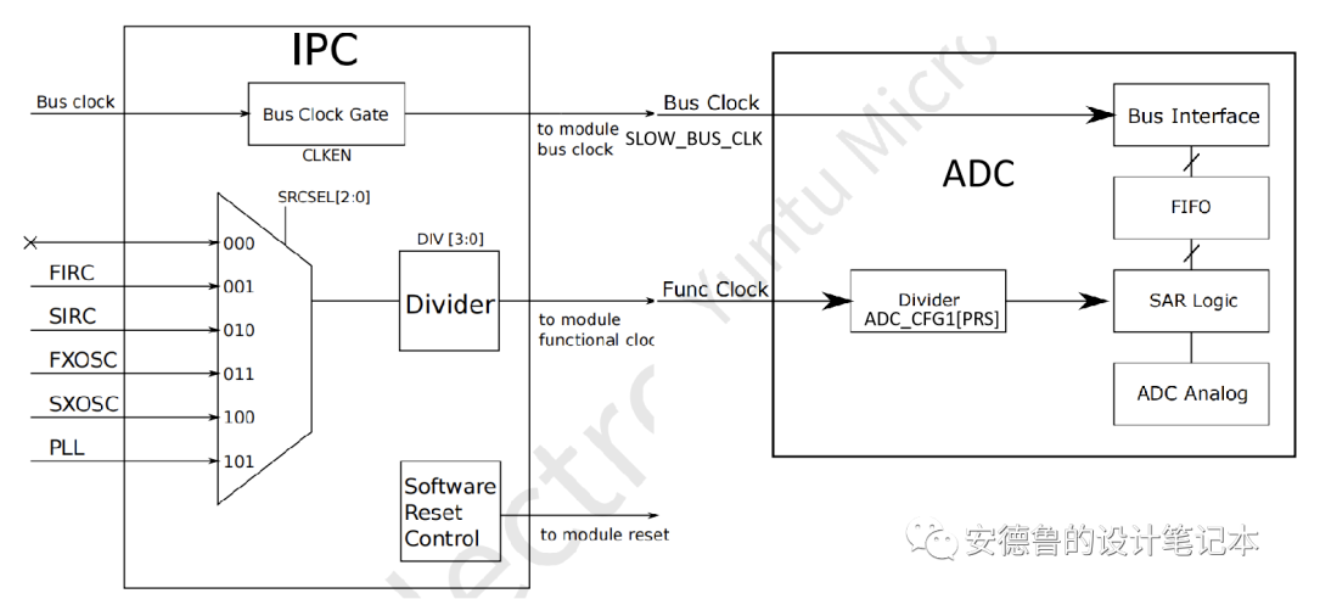

ADC作为一个模拟外设,通常会使用两个时钟源:使用总线时钟驱动数字部分的电路,例如通过总线访问寄存器等;通过功能时钟驱动模拟部分的ADC转换器工作。如图x所示。

图x ADC外设的总线时钟和功能时钟

这里有两个要点:

- 通过IPC可以选择ADC转换器的输入时钟源。实际上,ADC的模拟电路部分也不一定能消化掉来自于IPC的时钟源,内部还专门设计的分频器。模拟电路对频率敏感,因此特定的电路也会要求能够处理的频率信号在一定范围内。YTM32的ADC转换器最高可以使用16MHz的时钟信号作为ADC转换器的时钟源。

- 模拟和数字部分在交换数据时,需要处理同步(同支持高频率的定时器)。

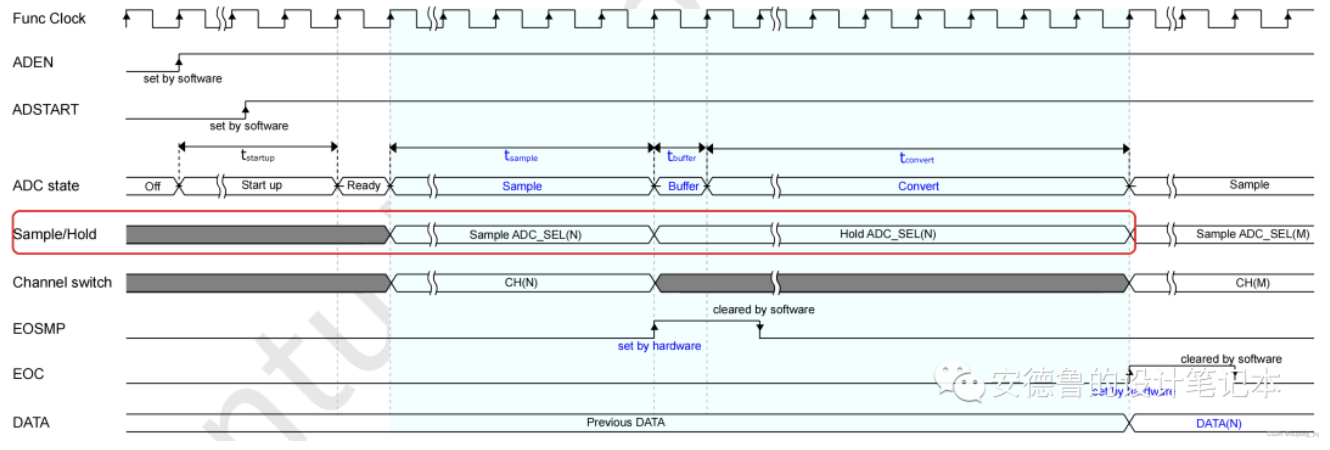

ADC采样的时序,通常包含采样(Sampling)和保持(Holding)两个阶段,如图x所示。采样和保持在ADC的时钟驱动下工作,时间越长,采样的结果越接近真实值,但速度也会变慢。若用户需要使用更快的采样速度,只要提高ADC转换时钟和缩短采样保持阶段的时间即可,但产生的转换结果就可能损失一些准确度了。

图x ADC转换中的采样保持时间

YTM32的ADC外设,为了有效地使用电能,将ADC转换器上电和掉电的控制接口也开放给用户了。要知道,ADC作为一个模拟外设,是个耗电大户(另一个耗电大户是PLL),如果在不需要执行ADC转换任务的阶段停电,可能有效减少功耗,也能控制芯片的发热。但是,ADC上电和下电过程,也都是需要一定时间的,上电过程需要等待供电稳定后才能启动ADC转换任务,ADC需要把正在执行的任务执行完毕,清理好工作现场之后才能顺利下电。这些时间,都将会在使用ADC转换器的过程中由用户配置。

原理与机制

ADC转换器的上下电和省电模式

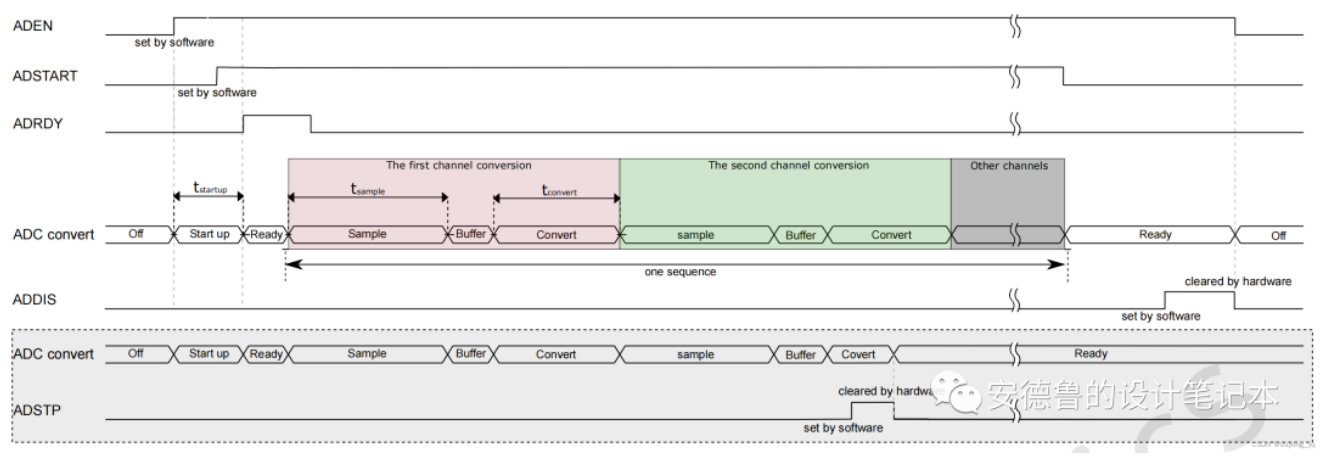

MCU上电后,软件通过IPC模块,为ADC外设模块开放了总线时钟供应,但此时,ADC转换器的供电还没有加上,ADC外设模块处于掉电模式(Off State,power-down mode)。若要启用ADC转换器,需由用户先设定ADC_CTRL[ADEN]=1,开始为ADC转换器供电,待t_startup(约2us)后,ADC转换器供电稳定,硬件置寄存器位ADC_CTRL[ADRDY]=1,告知用户可以启动转换。此时请求ADC开始转换,软件触发设定寄存器ADC_CTRL[ADSTART]=1,才正式启动ADC转换。如图x所示。

图x ADC转换器的信号时序

注意,图x中的ADSTART信号在ADRDY之前置位,同前文讲述等待ADRDY置位后才拉起ADSTART不同。这展示了一种典型的情况:ADSTART只是请求不是命令,只有当ADRDY置位之后,ADC转换器才能启动。

ADC_CTRL[ADDIS]=1可以直接给ADC转换器断电。但为了确保ADC内部的状态机不会被打乱,建议先通过ADC_CTRL[ADSTOP]=1请求停止转换任务,在确保ADC转换器已经不再执行任何转换任务后,再给ADC转换器断电。

关于给ADC转换器断电的操作,YTM32的ADC外设还设计了一些“自动化”的供电管理机制,自动断电Auto-Off模式,对应寄存器开关ADC_CFG0[AUTOOFF]。

- 默认未启动自动断电模式时,用户一为ADC转换器建立稳定的供电后,若无人为停用,则对ADC转换器持续供电。下次启动转换也不需要等上电稳定。

- 若启用自动断电模式,则一旦ADC转换器闲下来就自动断电,在下次转换任务的触发信号到来时可自动唤醒恢复供电。此时,每次启动转换任务,ADC转换器都要等上电稳定(t_startup)后再启动转换。这个模式下,原本硬件反馈供电稳定的

ADC_CTRL[ADRDY]标志位将不再起作用(置位)。

启用自动断电模式后,执行每次转换任务之前,都需要重新等待供电稳定的时间t_startup,这无疑影响了ADC的连续转换速率。但大多数情况下,应用对连续转换速率没有特别高的要求,使用启动断电模式可以在简化用户操作的前提下(不需要人工上电断电),有效降低ADC转换器的动态功耗。

ADC转换结果和FIFO

ADC外设内部设计了一个32-bit x 16 的FIFO,按照转换完成的顺序,依次存入转换完成的结果。用户从寄存器ADC_FIFO作为读FIFO的入口,可以依次读出转换结果。

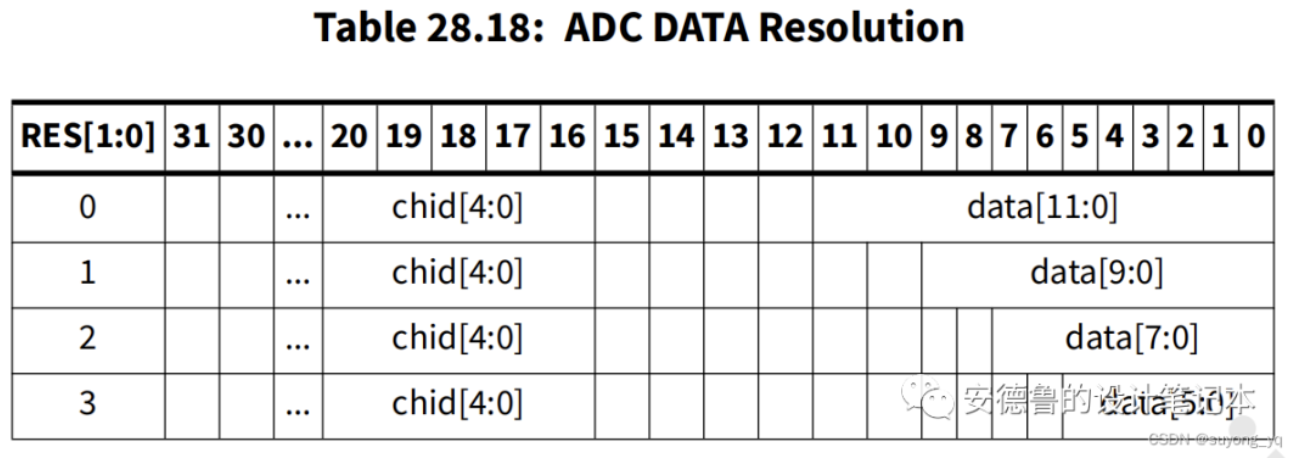

FIFO中的数据单元包含转换结果对应的通道ADC_FIFO[CHID]和转换数值ADC_FIFO[DATA],无论设定的转换分辨率(ADC_CFG[RES])是多少,数值固定右对齐的。如图x所示。

ADC FIFO中的转换结果

当FIFO填满了未能及时读走的转换数据,ADC外设设计了两种机制处理后来的数据,一种是Overrun Mode,另一个是Wait Mode:

Overrun Mode描述的是,当新的转换结果到来时,是覆盖FIFO中最近一次转换结果,还是直接抛弃掉新的转换结果。由寄存器ADC_CFG0[OVRMD]控制启用。Wait Mode描述的是,当FIFO满的时候,直接给ADC转换器断电(类似于Auto-Off模式)。只有当FIFO有空位的时候,才能给ADC转换器供电。由寄存器ADC_CFG0[WAIT]控制启用。

ADC转换队列的工作模式

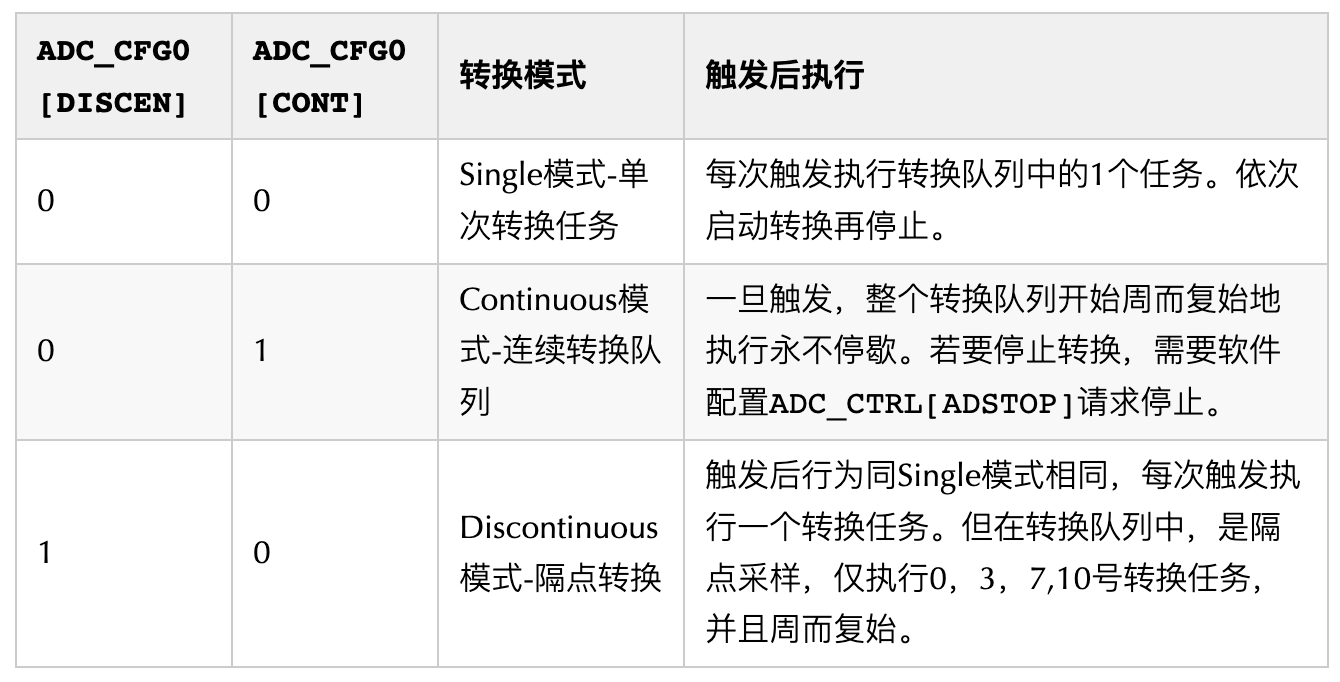

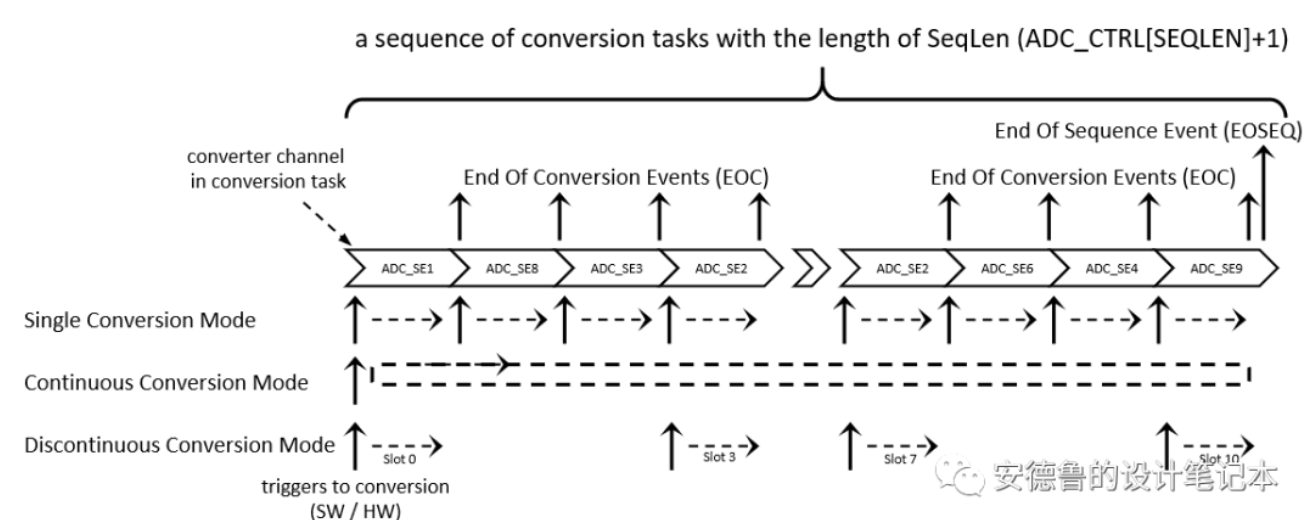

ADC的转换过程,是由多个单通道的转换任务串起来的转换队列,由寄存器字段ADC_CFG0[SEQLEN]由触发信号驱动执行转换过程。YTM32的ADC外设模块中,设计了多种触发机制,以不同的节奏执行转换队列中的转换任务。通过配置寄存器位ADC_CFG0[DISCEN]和ADC_CFG0[CONT],对应有Single模式、Continuou模式和Discontinuous模式。

表x ADC转换队列的工作模式

图x ADC转换队列的工作模式

ADC转换器的触发信号

ADC外设模块可以捕获软件触发和硬件触发信号(一个上升沿脉冲信号),以启动转换任务。触发信号无论是来自于软件触发还是硬件触发,对于启动转换的作用是完全相同的,但ADC仅允许使用其中一种触发模式,由寄存器ADC_CFG0[TRIGMD]选定。

- 当

ADC_CFG0[TRIGMD]=0,软件触发可由用户写寄存器ADC_CTRL[ADCSTART]=1产生。 - 当

ADC_CFG0[TRIGMD]=1,还需要设定寄存器ADC_CTRL[ADCSTART]=1解锁硬件触发信号(同步),硬件触发的信号可以来自于芯片上的其它外设模块。

硬件触发信号大多来自于TMU(Trigger Multiplexer Module)或者PTU模块(Programmable Trigger Unit),可以通过CIM(Chip Integration Module)模块的寄存器CIM_CTRL[ADCn_TRIG_SEL]选择ADC外设外部的触发信号源:

- Raw signal which from the PTU module (CIM->CTRL[ADCn_TRIG_SEL]=0)

- Signal from the TMU module and synchronized by bus clock (CIM->CTRL[ADCn_TRIG_SEL]=1)

- Signal from the TMU module and synchronized by function clock (CIM->CTRL[ADCn_TRIG_SEL]=2)

ADC转换器的看门狗

YTM32微控制器的ADC外设设计了看门狗的功能,这个功能在同类的设计中,还有一个更直观的名字,“硬件自动比较”。意思是通过为采样转换结果设置一个高限ADC_WDTH[HIGH]和低限ADC_WDTH[LOW]框起来的正常数值区间,每次ADC执行转换完成后,硬件都自动将转换结果同预设的正常数值区间进行比较,当采样结果过高(高于高限)或者过低(低于底限),都会触发一个超出预设范围的事件(可以触发中断)。这个功能通常用于实现对传感器的监控。某些MCU上设计ADC可以使用异步时钟在低功耗模式下继续存活,就会用到这个硬件自动判定超限的机制,只有当出现异常采样时,才唤醒CPU对环境做进一步的判断。

然而,当下的这款ADC最多可以保存16个转换结果(在FIFO中)和24个采样通道,但没有为16个转换结果或者24个采样通道分别安排上限值寄存器和下限值寄存器。 这里有个机制,通过寄存器ADC_WDCTRL[WDSGL]选择:

- 当

ADC_WDCTRL[WDSGL]=0时,硬件比较的机制会作用于FIFO的入口,任何通道的转换结果进入FIFO时,都会被比较,有可能触发超事件。 - 当

ADC_WDCTRL[WDSGL]=1时,硬件自动比较会现定于某个指定的通道,通道号设置于寄存器字段ADC_WDCTRL[WDCHSEL]中。

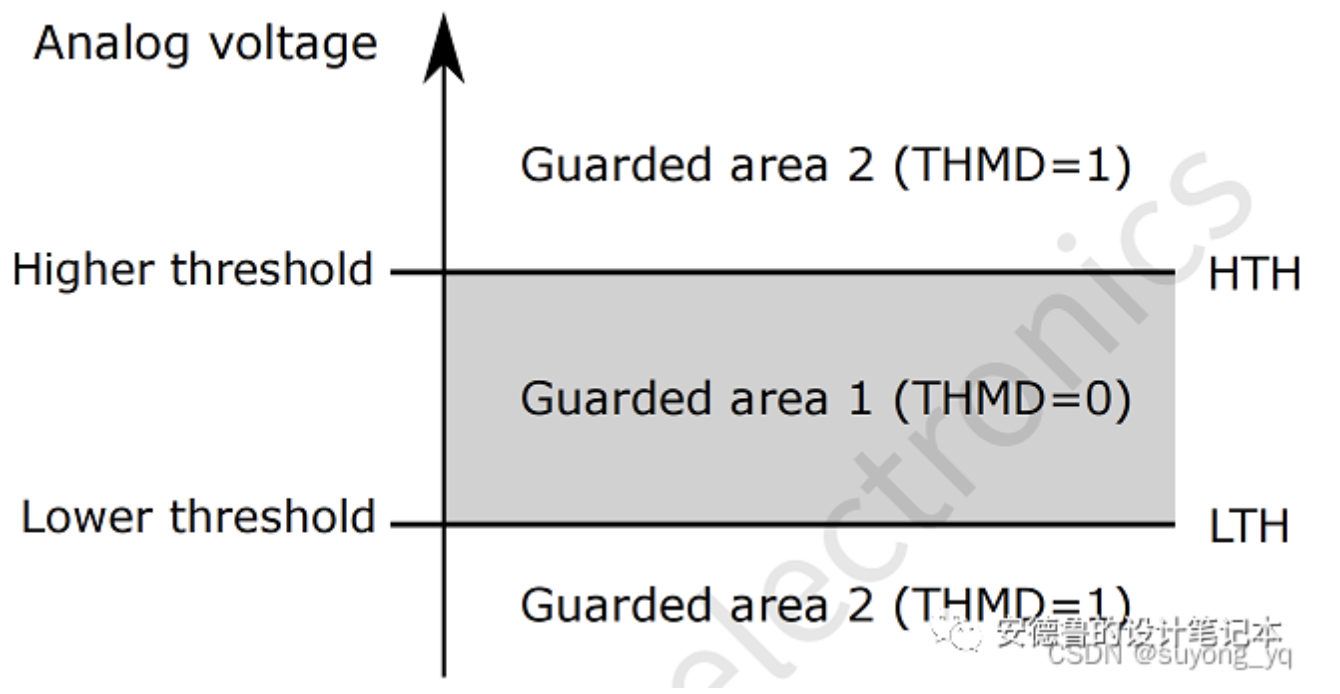

另外,还有控制位ADC_WDTH[THMD],可以设定在ADC转换的结果是限定区域之内触发超限事件还是在限定区域之外。如图x所示。

图x 硬件自动比较的有效范围

中断事件和DMA

ADC转换器能够触发中断的事件,主要是面向转换任务和转换队列的执行转换任务完成的情况,ADC外设甚至对ADC转换器上电成功和采样阶段结束也设计中断事件。

ADC的DMA是基于FIFO设计的。用户可以在寄存器ADC_CFG0[WM]中设定产生DMA触发信号的FIFO有效数据数量的阈值,当FIFO中已经填入的转换结果数量达到预设的阈值时,ADC外设会向DMAMUX发出DMA触发信号,预设的DMA搬运任务将一次性从ADC的FIFO中搬运走预设数量(可以小于等于预设的数量阈值)的转换结果、

FIFO的阈值事件是可以产生DMA的触发信号的同时,也可以产生中断的触发信号。根据设计惯例,当同一个事件的DMA和中断触发开关同时打开时,DMA的优先级更高,中断信号不会发出。否则,如果在中断服务程序中将FIFO中的数据读走了,给DMA搬运的数据不够多,FIFO就会产生下溢错。

应用要点(软件)

YTMicro SDK中包含了YTM32的ADC外设模块的驱动程序adc_driver,并提供了关于ADC外设的样例工程,包括:adc、adc_dma、adc_all_channels等。

总结

YTM32的手册对ADC外设模块进行了基本的介绍,列写了ADC外设模块开放给用户的资源,本文对YTM32的ADC外设模块的功能进行演绎,更为细致地讲解了ADC外设模块及各功能的运行机制,方便用户充分理解ADC外设模块并结合应用利用好在ADC中设计的硬件资源。同时,本文也是对一种ADC外设模块的系统架构设计进行了较为细致的分析,推演了ADC外设模块的设计方法,可以为从事芯片设计的系统架构设计师们在设计IP时提供参考。

-

YTM32的增强型定时器eTMR外设模块简介2023-10-31 2888

-

YTM32的LIN通信协议引擎LinFlexD外设模块详解2023-10-08 3645

-

为什么我们需要模数转换器?哪个ADC转换器更好?2023-02-15 1808

-

模数转换器ADC简介2022-02-17 1789

-

【单片机基础】ADC0809模数转换器详解2021-11-23 1902

-

STM32之ADC模数转换器介绍2021-11-08 3278

-

模数转换器(ADC)的基本原理是什么?2021-09-28 2968

-

ADC模数转换器2021-08-06 2068

-

模数转换器(ADC)的配置有哪些流程?2021-07-14 3137

-

5962-9581501HXA高端AD模数转换器2020-07-15 2191

-

ADC0809模数转换器的使用详解与程序2015-11-02 1528

-

电流积分模数转换器(ADC),什么是电流积分模数转换器(AD2010-03-24 3648

-

数模和模数转换器2009-09-16 7931

全部0条评论

快来发表一下你的评论吧 !