基于Verilog的经典数字电路设计(5)译码器

电子说

1.4w人已加入

描述

引言

前面讲完了编码器,其实不知不觉地,也顺便把译码器也讲了,毕竟,二者是一个相反操作的过程,类似于加减,前进与后退,调制与解调,FFT 和 IFFT 等等。

译码器的逻辑功能就是将每一个输入的二进制代码转为对应的多输出高、低电平信号或另外一个代码,是编码器的逆运算,译码器又可以分为变量译码和显示译码。变量译码器一般是一种较少输入变为较多输出的器件,常见的有 N 线 - 2^N 线译码和 8421BCD 码译码两类;显示译码器用来将二进制数转换成对应的七段码,一般其可分为驱动 LED 和驱动 LCD 两类。

一、变量译码器的 Verilog 代码实现和 RTL 电路实现

module Decoders(

input wire [2:0] b, // 输入信号_未译码

output reg [7:0] d // 输出信号_已译码

);

reg d = 8'b0000_0000;

always @ ( b ) begin

case ( b )

3'b000 : d <= 8'b0000_0001;

3'b001 : d <= 8'b0000_0010;

3'b010 : d <= 8'b0000_0100;

3'b100 : d <= 8'b0001_0000;

3'b101 : d <= 8'b0010_0000;

3'b110 : d <= 8'b0100_0000;

3'b111 : d <= 8'b1000_0000;

default: d <= 8'b0000_0000;

endcase

end

endmodule

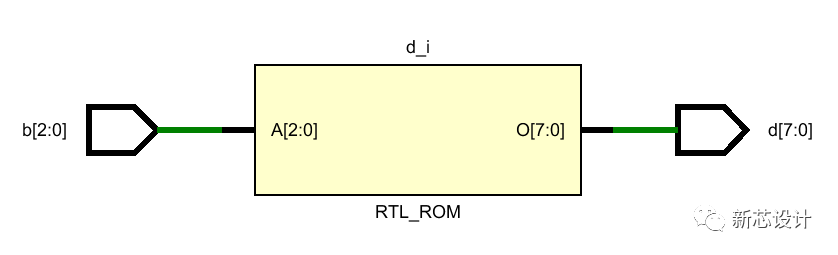

这是一个 3 线 − 8 线变量译码器,基于查找表 LUT(Look Up Table)的方式实现的一个电路,其 RTL 电路图如下所示:

变量译码器的 RTL 电路图

这里的译码器,其实就只是基于 LUT 的译码器,是最简单的,并没有经过复杂的运算操作,其思想只是简单地输入地址,然后输入地址所在的数据即可。

译码是编码的逆过程,在编码时,每一种二进制代码,都赋予了特定的含义,即都表示了一个确定的信号或者对象;把代码状态的特定含义 “翻译” 出来的过程叫做译码,实现译码操作的电路称为译码器;或者说,译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

数字电路—12、译码器2025-03-26 669

-

40. 译码器 (5)#译码器 #数字电路电路设计快学 2022-07-27

-

数字电路设计与Verilog HDL2015-07-16 13842

-

数字电子电路技术--译码器及其应用2017-05-01 4353

-

数字电路设计的基本方法有哪些2019-02-27 6335

-

译码器定义2021-12-07 2553

-

译码器2008-09-27 14347

-

集成电路译码器2009-04-07 9922

-

译码器,译码器是什么意思2010-03-08 5879

-

74HCl38译码器在数字电路设计中的应用2010-06-28 29081

-

数字电路中显示译码器设计的分析2011-07-12 12151

-

译码器的分类和应用2018-04-04 46656

-

Multisim14.0数字电路译码器实现函数的工程文件免费下载2020-05-28 1445

-

单片机 什么是编码器?什么是译码器?2021-11-24 1746

-

如何使用 Verilog 进行数字电路设计2024-12-17 2203

全部0条评论

快来发表一下你的评论吧 !