D触发器与Latch锁存器电路设计

电子说

1.4w人已加入

描述

引言

D 触发器,是时序逻辑电路中必备的一个基本单元,学好 D 触发器,是学好时序逻辑电路的前提条件,其重要性不亚于加法器,二者共同构成数字电路组合、时序逻辑的基础。

一、D 触发器的 Verilog 代码实现和 RTL 电路实现

module D_FF(

input Clk,

input D,

output reg Q

);

always @(posedge Clk) begin

Q <= D;

end

endmodule

触发器(Flip - Flop):能够存储 1 位二值信号的基本单元统称为 D 触发器,简称 DFF,多个 D 触发器的级联便构成了能够存储多位二值信号的基本电路。时钟信号(Clock),简称 Clk,当系统中有多个 D 触发器需要同时动作时,就可以用同一个 Clk 信号作为同步控制信号。

电路中的输入端处没有小圆圈表示 Signal 以高电平为有效信号。(如果在 Signal 输入端画有小圆圈,则表示 Signal 以低电平作为有效信号)。

D 触发器的 RTL 电路图如下所示:

D 触发器的 RTL 电路图

二、D 触发器的 Verilog 代码实现和 RTL 电路实现

module Latch(

input din,

input en,

output reg dout

);

always @(din or en)

if(en)

dout <= din;

endmodule

锁存器(Latch):一种对脉冲电平敏感的存储单元电路,可以在特定输入脉冲电平作用下才改变状态;而锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用是缓存,利用电平控制数据的输入与输出,它包括不带使能控制的锁存器和带使能控制的锁存器。锁存器的缺点是容易产生毛刺,不稳定,不利于静态时序分析。

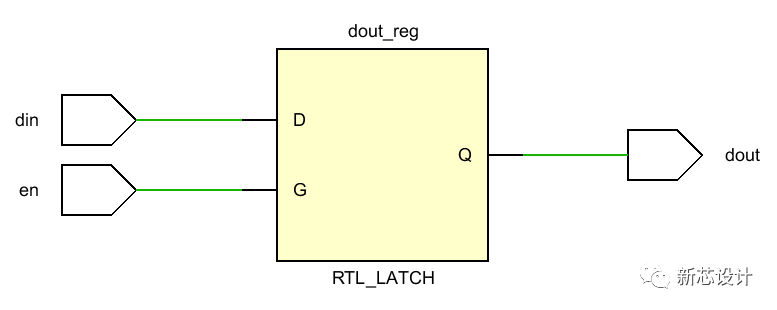

锁存器的 RTL 电路图如下所示:

锁存器的 RTL 电路图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

d触发器和d锁存器的区别是什么2024-08-28 4229

-

sr锁存器和触发器的逻辑功能区别2024-07-23 2189

-

触发器与锁存器的区别在哪?2023-12-04 3623

-

什么是D触发器,D触发器如何工作的?2023-06-29 52360

-

锁存器、触发器、寄存器的关联与区别及其相应的verilog描述2022-12-19 15185

-

锁存器和触发器2022-03-10 9577

-

图文并茂:D型触发器电路设计教程2021-02-03 14168

-

锁存器与触发器的区别2020-11-29 26689

-

【转】数字电路三剑客:锁存器、触发器和寄存器2018-10-27 2840

-

寄存器、锁存器和触发器的区别2018-07-03 4111

-

锁存器Latch和触发器Flip-flop有何区别2018-04-18 133986

-

凔海笔记之FPGA(六):触发器和锁存器2016-05-21 4455

-

锁存器、触发器、寄存器和缓冲器的区别2011-10-09 9569

-

锁存器和触发器原理2010-08-18 2078

全部0条评论

快来发表一下你的评论吧 !