JK触发器与T触发器的Verilog代码实现和RTL电路实现

电子说

1.4w人已加入

描述

一、JK 触发器的 Verilog 代码实现和 RTL 电路实现

module JK_FF(

input wire Clk,

input wire J,

input wire K,

output reg Q

);

// 公式

always @(posedge Clk) begin

Q <= (J&(~Q))|((~K)&Q);

end

// 查找表

// always @(posedge Clk)

// case({J,K})

// 2'b00: Q <= Q;

// 2'b01: Q <= 0;

// 2'b10: Q <= 1;

// 2'b11: Q <= ~Q;

// endcase

endmodule

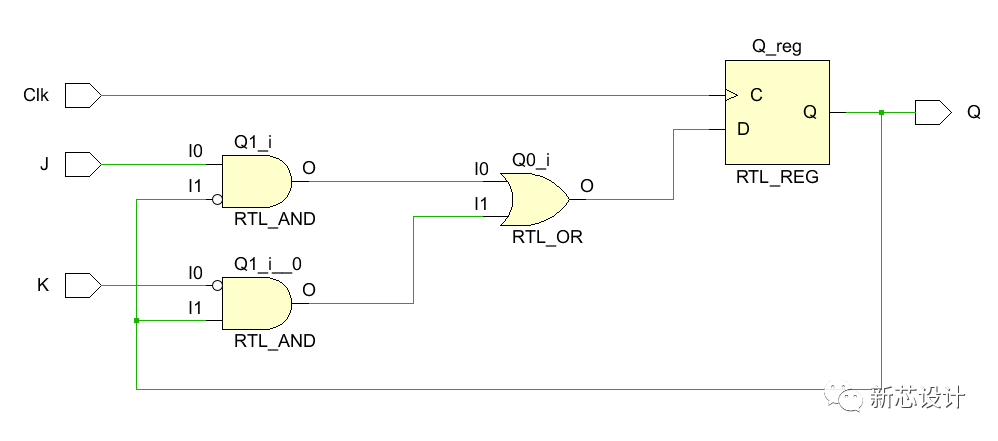

JK 触发器的 RTL 电路图如下所示:

JK 触发器的 RTL 电路图

二、T 触发器的 Verilog 代码实现和 RTL 电路实现

module T_FF(

input wire Clk,

input wire T,

output reg Q

);

// 公式

always @(posedge Clk) begin

Q <= (T&(~Q))|((~T)&Q);

end

// 查找表

// always @(posedge Clk)

// if(t)

// Q <= ~Q;

// else

// Q <= Q;

endmodule

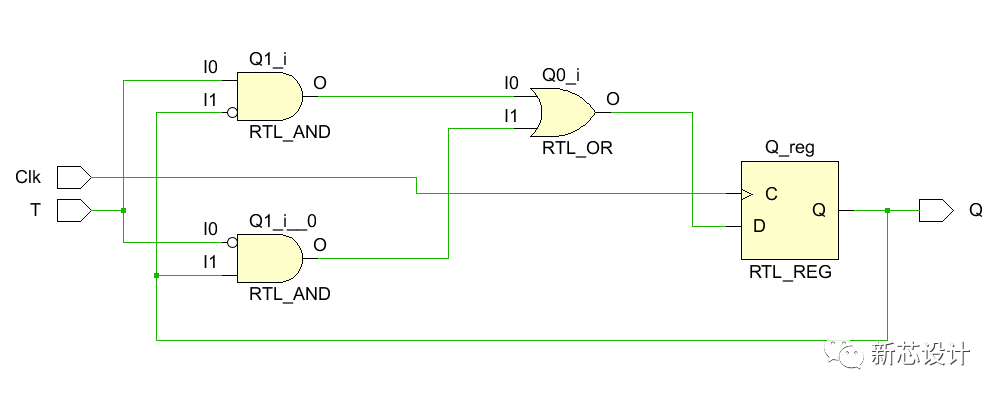

T 触发器的 RTL 电路图如下所示:

T 触发器的 RTL 电路图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

把jk触发器转换为t的方法2024-08-28 4521

-

主从jk触发器和边沿jk触发器的区别2024-08-22 8387

-

t触发器和jk触发器的区别和联系2024-02-06 8162

-

JK触发器逻辑符号_jk触发器的特性方程2019-11-08 97492

-

jk触发器逻辑表达式是什么?2018-02-08 54095

-

jk边沿触发器工作原理2018-01-30 38735

-

jk触发器是什么原理_jk触发器特性表和状态转换图2017-12-25 192879

-

jk触发器实现74ls194功能2017-12-22 25858

-

JK触发器,JK触发器是什么意思2010-03-08 7617

全部0条评论

快来发表一下你的评论吧 !