CREE功放管漏级偏置电路对称设计分析

电子说

1.4w人已加入

描述

CGH40045F-TB漏级偏置电路采用对称设计,主要分析原因在于降低偏置网络阻抗,提高视频带宽VBW,从而减小功放管的电记忆效应。

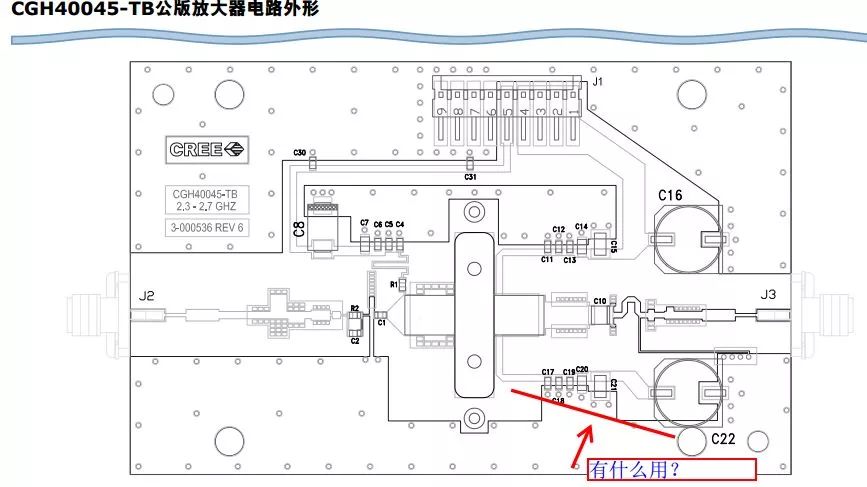

图1 CGH40045-TB PCB图

以下简单介绍下VBW与电记忆效应:

- 低阻抗通路的带宽被称为视频带宽(VBW),范围为100KHz~200MHz,个人理解为调制信号的带宽,即信道带宽,跟输入的调制信号有关。

- 功率管的记忆效应分为热记忆效应和电记忆效应,热记忆效应主要跟晶体管沟道温度周期有关,电记忆效应主要来源于功率放大电路的直流偏置。记忆效应的本质在于当前的时刻不仅跟输入信号有关,还跟过去的某一时刻有关,体现在增益和相位上。

当功放管在数字预失真方案中,减小记忆效应对功放的影响显的尤为重要,偏置电路是记忆效应的一个重要来源,现实中,功率管的漏极到电源之间的电路阻抗(video impedance)在低频(VBW 10MHz)时并非为0,该阻抗的存在使得加载到功率管漏极的电压并非是个恒定值,而是随着功放输入信号变化。

如果是纯阻性的,仅仅引起增益压缩,如果存在电抗部分,则引起记忆效应,因此在设计时,需要该阻抗越小越好。同时工程实验证明在同样的输入信号,同样的DPD系统中,较大的视频带宽(VBW)的ACPR要比较小的视频带宽(VBW)的ACPR要好。

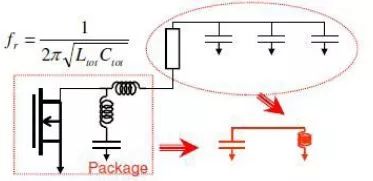

图2 晶体管VBW计算公式

图2所示,fr表征的是晶体管输出段低频谐振频率,频率越高,VBW越宽,Ltot指得是供电线跟旁路电容组成的等效电感,Ctot指的是晶体管漏级之间的电容,因此在可操作性上提高VBW的措施是降低Ltot。具体措施如下:

1.如图1所示,漏级双供电方式,并联降低阻抗,减小低频信号的影响。

2.将uF级的电容靠近漏级放置,电容的工作频率实际大于其SFR,这样电容呈感性,从而减小Ltot,提高VBW

3.缩短漏级供电线长度,小于1/4波长,但是这样会牺牲一部分功率。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

选择功放管要注意的三个参数2024-03-01 6312

-

数字万用表测功放管好坏的方法2023-09-02 15648

-

安森美功放管解读 安森美功放管怎么样 安森美功放管优缺点2023-03-29 35051

-

二极管怎么进行偏置互补对称电路?2019-10-12 2078

-

Infineon的LDMOS功放管简介2019-07-08 5462

-

自制功放管恒温电路2017-06-25 5538

-

急急急,本人想用功放管做一个H桥驱动电机。2017-03-16 6970

-

功放管发热严重怎么办?2016-05-24 47992

-

如何在Datasheet上查找功放管的电流2016-04-19 2988

-

功放的功放管越少,音质越好2015-12-15 15763

-

功放音量小,功放管发烫2011-03-19 12163

-

立体声功放管及电路 (Stereo Tube Amplifi2009-12-25 5502

-

功放管的三种工作状态2006-04-17 4052

-

[组图]功放管的三种工作状态2006-04-15 1660

全部0条评论

快来发表一下你的评论吧 !