仿真测试3:分频、奇数、偶数

电子说

1.4w人已加入

描述

偶分频

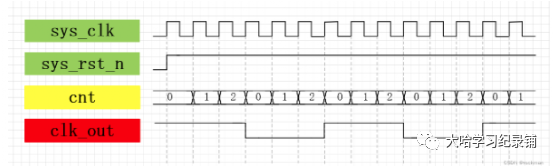

5.1计数实现偶12分频(占空比50%)

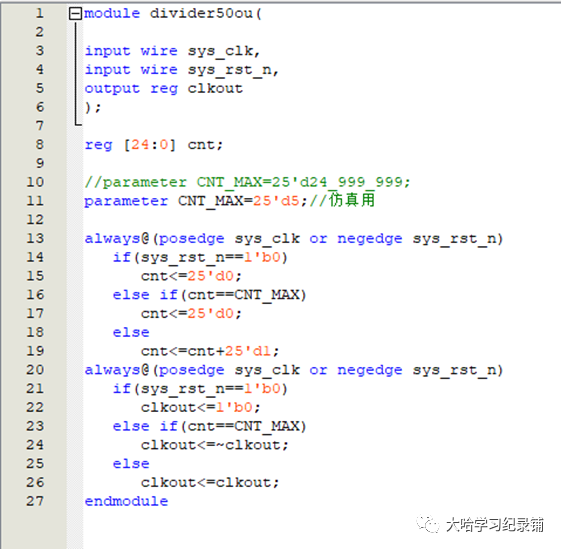

5.1.1源码

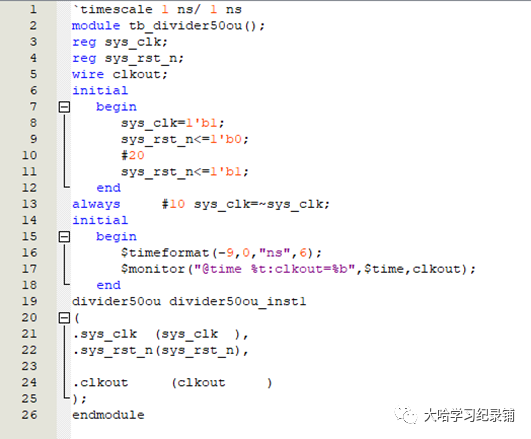

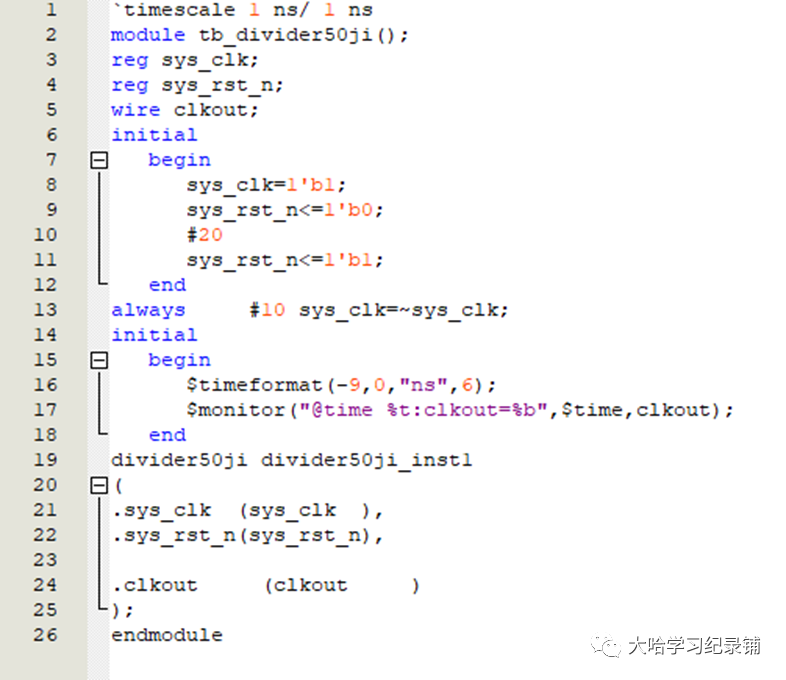

5.1.2测试源码

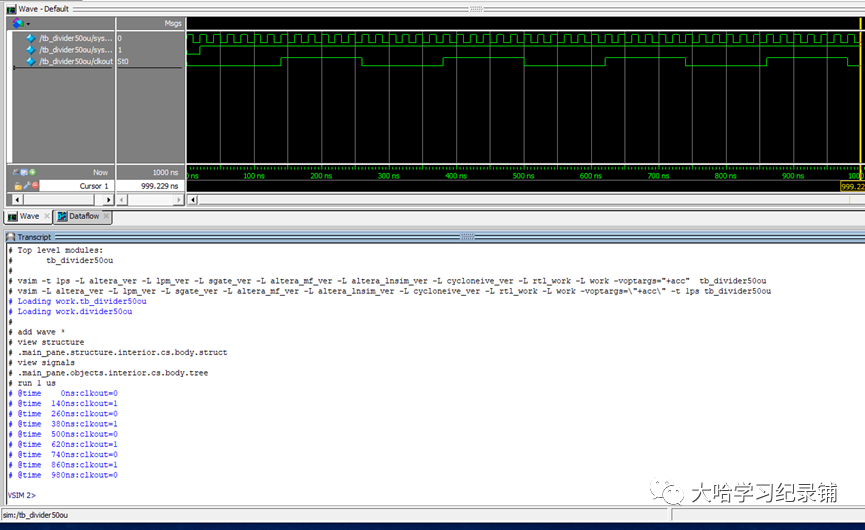

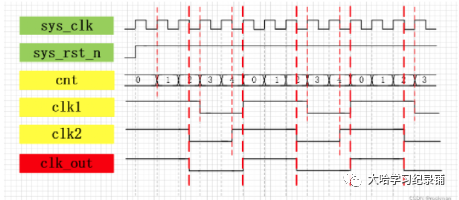

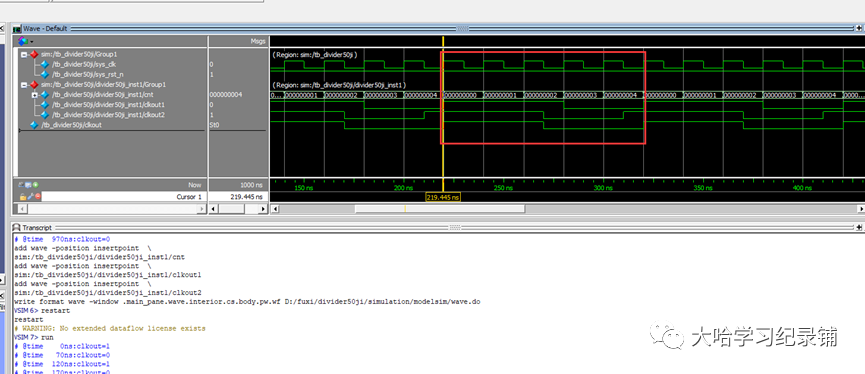

5.1.3仿真图

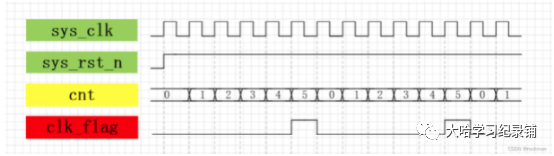

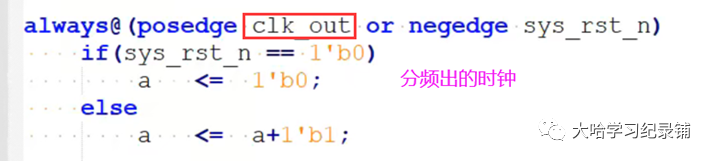

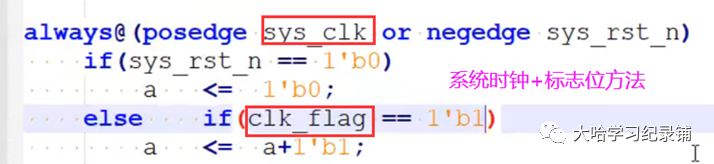

5.2通过一个标志信号作为偶6分频的工作时钟(可靠,常用)

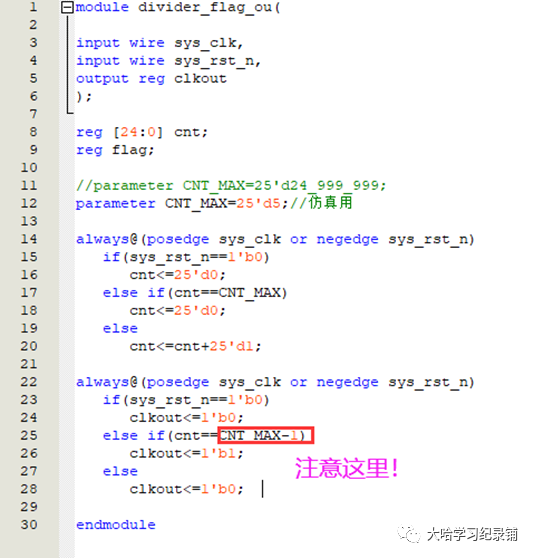

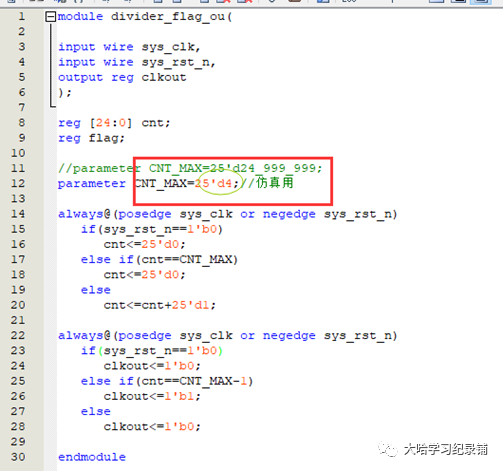

5.2.1源码

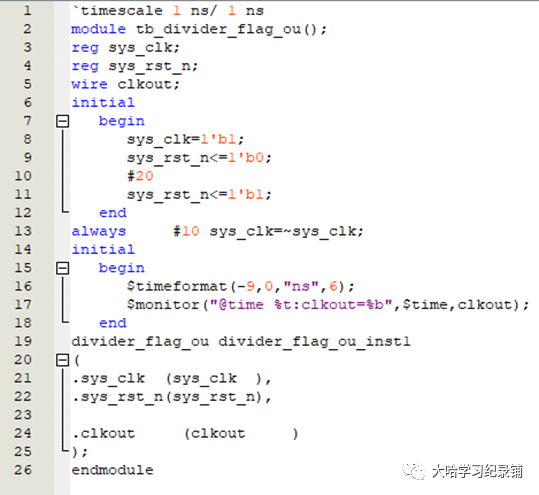

5.2.2测试源码

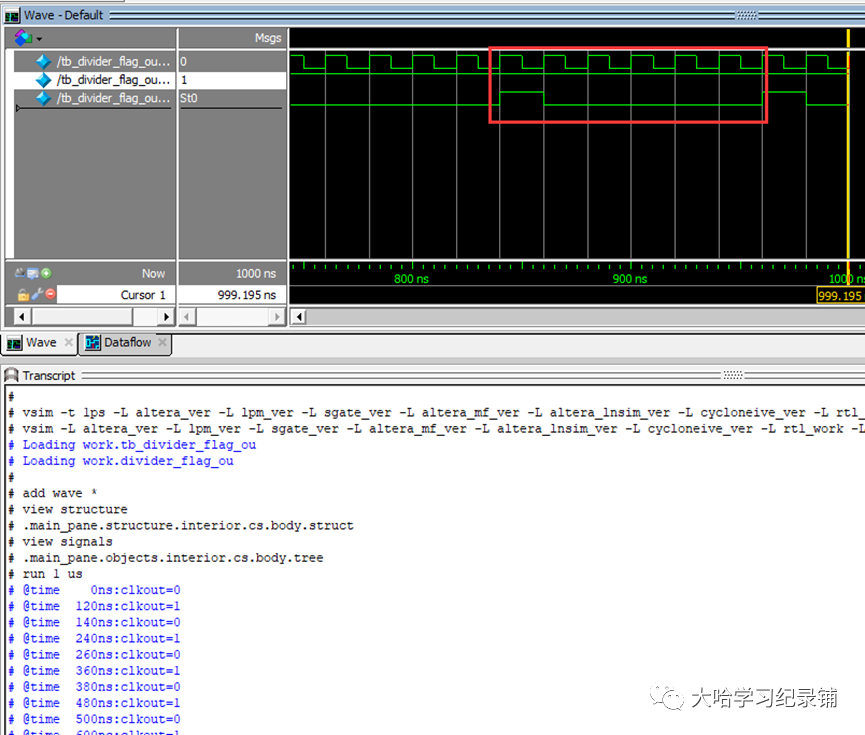

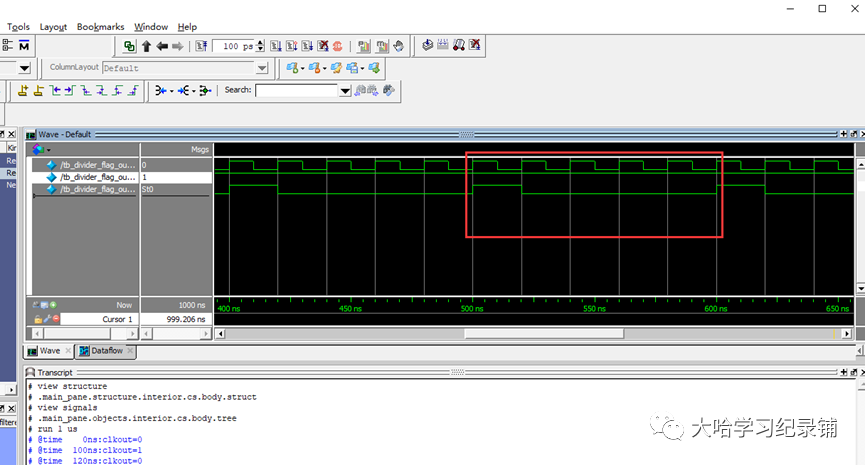

5.2.3仿真图

这里为什么要说明这两种方式呢?

这里就要说到FPGA中的全局时钟网络,因为在 FPGA 中凡是时钟信号都要连接到全局时钟网络上,全局时钟网络也称为全局时钟树,是 FPGA 厂商专为时钟路径而特殊设计的,它能够使时钟信号到达每个寄存器的时间都尽可能相同,以保证更低的时钟偏斜(Skew)和抖动(Jitter)。

然而我们采用第一种方式产生的时钟clk_out信号并没有连接到全局时钟网络上,这种做法所衍生的潜在问题在低速系统中不易察觉,而在高速系统中就很容易出现问题,但 sys_clk 则是由外部晶振直接通过管脚连接到了 FPGA 的专用时钟管脚上,自然就会连接到全局时钟网络上,所以在 sys_clk 时钟工作下的信号要比在 clk_out 时钟工作下的信号更容易在高速系统中保持稳定。所以第二种方式相对来说更加安全。

应用时候:

第一种:

奇分频

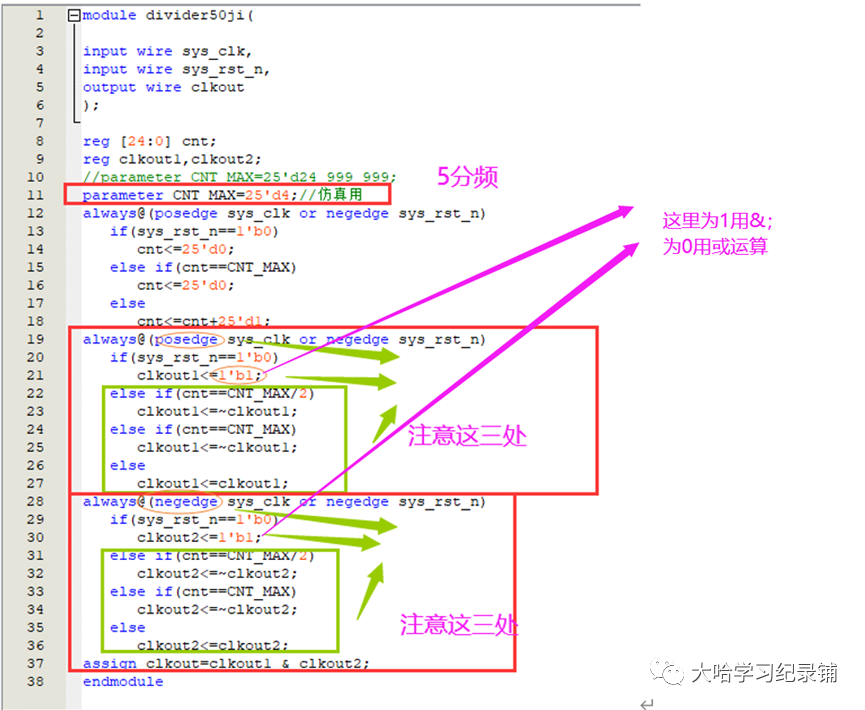

5.3占空比50%实现5分频方法(即5.1方法)

通过always语句,做一个上升沿的分频,与一个下降沿的分频,将分频后的结果取与运算。例如5分频:先做一个上升沿触发的5分频,三个周期低电平,两个周期高电平。在做一个下降沿触发的5分频,三个周期低电平,两个周期高电平。最后将两个分频后的结果取与运算,就是常规的5分频。

5.3.1源码

5.3.2测试源码

5.3.3仿真图

5.4标志位方法与5.2一致(不再赘述)在高速系统中,仍采用flag信号的方法进行分频。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

一文读懂奇数代和偶数代的差别 奇数代和偶数代有什么不同?2023-05-23 2180

-

偶数分频、奇数分频、半整数分频和小数分频详解2023-03-29 7175

-

奇数分频器的设计2023-03-23 2160

-

奇数分频器的介绍和实现2021-03-12 7418

-

奇数分频如何得到呢? 解读奇数分频和逻辑分析仪(ILA)的使用2020-12-28 3786

-

PCB多层板为什么都是偶数层?奇数有何风险?2020-10-30 1645

-

基于复杂可编程逻辑器件和VHDL语言实现半整数分频器的设计2020-06-26 1557

-

如何利用Verilog实现奇数倍分频2019-07-09 2689

-

利用Verilog实现奇数倍分频2019-06-14 2141

-

分频器的作用是什么 半整数分频器原理图分析2019-02-01 19064

-

请问AD9518 VCO偶数分频失锁是什么原因2018-08-19 2117

-

LED奇数号灯和偶数号灯的交替显示程序详解2018-05-12 13636

-

用Verilog实现基于FPGA的通用分频器的设计2016-07-14 1274

-

基于Verilog的FPGA分频设计2011-11-09 1500

全部0条评论

快来发表一下你的评论吧 !