如何设计一个对按键信号进行计数的计数器?

电子说

描述

实验任务: 本实验中要设计一个对按键信号(key_in)进行计数的计数器。

实验原理: 整个实验电路包含四个模块:

① erzp模块完成按键消抖功能,默认抖动时间为10MS;

② detect_module模块用于检测按键信号的下降沿,当检测到下降沿后,输出一个时钟周期的高电平。

③ get_state模块:将按键信号转换成状态信号,当按键按下后,状态转换0→1→0→1→……..。

④ cnt10模块:完成对按键信号进行计数。clk:系统时钟,cnt_en:计数使能(1:计数,0:暂停),cnt_single:计数信号,rst_n:复位信号,updown_state:加1计数或减1计数控制(1:加1计数,0:减1计数)。data:计数结果输出。

源代码撰写:

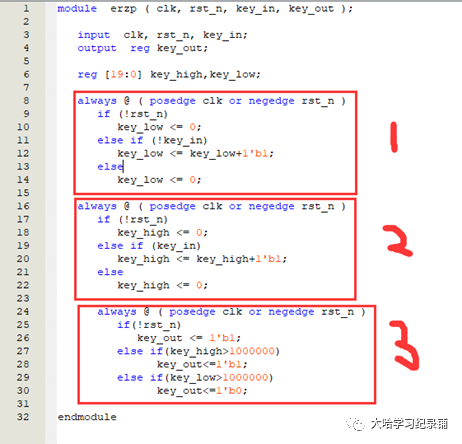

erzp****模块:

默认抖动时间最多为10ms,框1与框2的功能就是,计数当前电平若处于一直处于低电平就key_low一直自加1 ,一旦不是低电平了key_low就清0.高电平key_hign同理。当key_low或key_hign当前计数到了10ms,说明当前已经过了抖动状态。并且输出当前消抖后的对应电平。

detect_module****模块:

这里主要是利用了一个寄存器,让上一个时钟状态的按键状态和当前的对比,不一样说明有了边缘变化。

get_state****模块:

cnt10****模块:

原理图绘制顶层文件流程:

1.将以上四个.v文件依次转换为电路器件,生成BSF文件如右图所示

2.建立一个顶层原理图bdf(后建立的要设为顶层,与项目工程名称一致。)

在原理图中可以放置器件,可以看到刚刚生产的器件。并按逻辑进行连接。并修改对应端口名。完成之后,为了之后仿真,可以转成.v文件。

生成如图所示:以后也可将此项目作为整个调用的器件,生成BSF文件

RTL视图:

测试代码撰写: 测试时,需将原理图移除,将转化的.V文件加进来。

测试结果

-

计数器同步和异步怎么判断2024-07-23 3803

-

同步计数器和异步计数器的区别2024-05-24 8427

-

计数器怎么用 计数器的作用有哪些2024-02-03 10836

-

同步计数器和异步计数器各有什么特点2023-12-15 3501

-

同步计数器和异步计数器的区别主要在哪里2023-12-13 16254

-

同步计数器和异步计数器是什么 同步计数器和异步计数器的主要区别?2023-03-25 30212

-

异步计数器的主要类型2022-10-11 7737

-

单片机应用系统设计技术——计数器2021-11-25 895

-

什么是计数器芯片?2021-07-13 16234

-

按键次数计数器2016-03-21 661

-

计数器,计数器的工作原理是什么?2010-03-08 62510

-

环形计数器和扭环形计数器2010-01-12 10408

-

计数器的级连使用2007-11-22 4550

全部0条评论

快来发表一下你的评论吧 !