组合逻辑电路实验分析

电子说

描述

一、实验目的

1、掌握组合逻辑电路的分析方法与测试方法

2、了解组合电路的冒险现象及其消除方法

二、实验原理

1、组合电路是最常见的逻辑电路,可以用一些常用的门电路来组合成具有其它功能的门电路。例如,根据与门的逻辑表达式Z=A·B=A·B得知,可以用两个与非门组合成一个与门。还可以组合成更复杂的逻辑关系。

2、组合电路的分析是根据所给的逻辑电路,写出其输入与输出之间的逻辑函数表达式或真值表,从而确定该电路的逻辑功能。

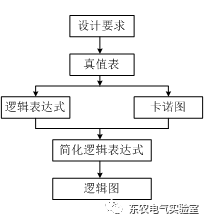

3、组合电路设计过程是在理想情况下进行的,即假设一切器件均没有延迟效应。组合逻辑电路设计的一般流程如下:

▶明确设计任务和要求;

▶建立输入和输出变量,列真值表;

▶逻辑表达式(逻辑代数/卡诺图);

▶根据器件类型修改逻辑表达式;

▶画逻辑图;

▶搭建逻辑电路;

▶实验测试。

4、半加器原理

半加器是实现两个一位二进制数加法运算的器件。输入A和B是相加的两个数,输出S是半加和数,C是进位数。。

由与非门组成的半加器逻辑电路及逻辑表达式分析如下图所示:

所谓半加就是不考虑进位的加法,它的真值表如下:

半加器真值表

5、全加器原理

全加器是实现两个一位二进制数及来自低位进位信号加法运算的器件。由与非门组成的全加器逻辑电路及逻辑表达式分析如下图所示:

一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci。

半加器真值表

三、实验设备与器件

- +5V直流电源

- 双踪示波器

- 连续脉冲源

- 逻辑电平开关

- 0-1指示器

- 74LS00 CC4011 CC4030 CC4071

四、实验内容

1. 分析、测试用与非门组成的半加器的逻辑功能

按半加器逻辑电路图接线。其中电源Vcc接+5V,GND接COM地,输入信号A、B分别接逻辑电平开关,输出Z1、Z2、Z3、S、C分别接LED。调整输入信号,观测输出信号。

实验步骤- 实测结果1(A、B输入为00、01)

实验步骤- 实测结果2(A、B输入为10、11)

列出半加器真值表,并画出卡诺图判断能否简化。

表4-1

卡诺图

2. 分析、测试用与非门组成的全加器的逻辑功能

按全加器逻辑电路图接线。其中电源Vcc接+5V,GND接COM地,输入信号Ai、Bi、Ci-1分别接逻辑电平开关,输出S、X1、X2、X3、Si、Ci分别接LED。调整输入信号,观测输出信号。

实验步骤- 实测结果1(Ai、Bi、Ci-1输入为000、001)

实验步骤- 实测结果2(Ai、Bi、Ci-1输入为010、011)

实验步骤- 实测结果3(Ai、Bi、Ci-1输入为100、101)

实验步骤- 实测结果4(Ai、Bi、Ci-1输入为110、111)

列出全加器真值表,并画出卡诺图判断能否简化。

表4-3

3、实验内容-选做

分析 、 测试用异或门、 或非门和非门组成的全加器逻辑电路。

根据全加器的逻辑表达式:

可知一位全加器可以用两个异或门和两个与门一个或门组成。

(1)画出用上述门电路实现的全加器逻辑电路。

(2)按所画的原理图,选择器件,并在实验箱上接线。

(3)进行逻辑功能测试,将测试结果填入自拟表格中,判断测试是否正确。

-

组合逻辑电路分析和设计方法2023-08-16 11871

-

组合逻辑电路的分析和设计2023-03-06 6348

-

组合逻辑电路实验原理2018-01-30 67925

-

组合逻辑电路的分析设计实验2016-12-29 825

-

组合逻辑电路的分析、设计和调试2009-11-19 1547

-

组合逻辑电路的设计及实验2009-10-10 3272

-

组合逻辑电路实验分析2009-07-15 2287

-

组合逻辑电路的分析与设计-逻辑代数2009-04-07 4109

-

SSI组合逻辑电路的实验分析2009-03-28 12170

-

组合逻辑电路实验2009-03-20 3354

-

基本组合逻辑电路2008-09-24 2961

-

组合逻辑电路设计实验2008-09-12 2559

全部0条评论

快来发表一下你的评论吧 !