浅析射频电路的接地孔与回流问题

电子说

描述

前沿

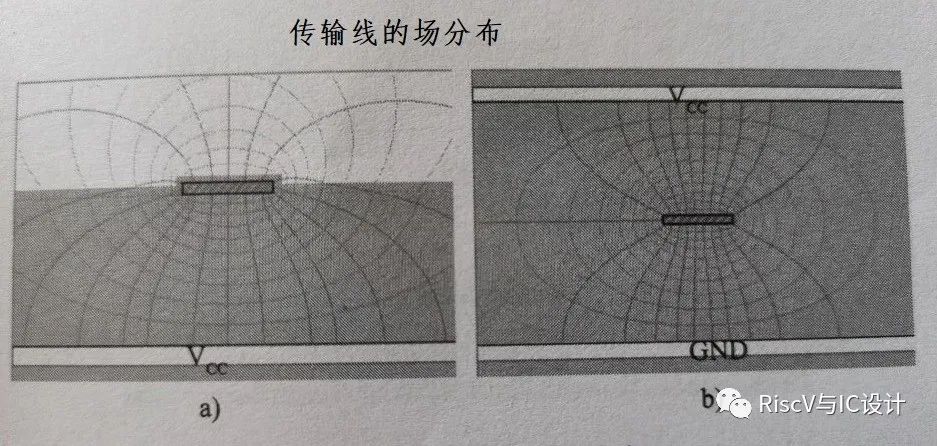

下图是PCB走线排板时常见的微带线(左图)和带状线(右图)的电磁场分布示意图,其电力线从走线层发出,终止于相关平面层,相关平面层不一定是地线层,可以是电源层,甚至是任意的网络层,在终止的相关平面层里会产生镜像电流,这个电流就叫走线层电流的"回流",回流与信号电流构成闭合回路,频率不是太高时满足电路理论的基尔霍夫电流定律,两者相等。

一般高速信号线的回流,我们都会尽量有意安排在地线层或某电源层上,而不是某信号走线层上,否则其串扰可能很大,不适合高速走线,具体分析见后面(三)

一、微带线的回流分布

微带线回流密度的大小分布如下图所示。回流分布在微带线的下方,且随着距离微带线正下方的距离越远(d越大),回流电流密度越小。

回流电流密度的分布,可以近似用以下公式表示:

随着d的距离的增大,在距离d范围以内的回流电流越多,其数据关系如下表所示:

表中也可以通过对上式电流密度I(d)积分,然后进行计算得到。比如对于d/h=2时,则在d=2h以外的电流归一化数值为(对I0/(pi*h)归一化):

而归一化的总电流为

所以包含在-d~d以内的电流的百分比为:

与上表中吻合。按同样的计算方法,可计算出当d=3h/5h/10h/20h时,分别对应的值为79.5%、87.4%、93.7%96.8%,也非常吻合。

二、带状线的回流分布

上图是带状线的回流分布,每个回流层的电流密度依然满足公式,只不过I0分别对应 I上和I下:

上下两个回流层的电流总和等于中间走线层的总电流,即I走线 = I上+I下

它们的比例 I上/I下 = h下/h上 。

下图是上下两回流层占总走线电流比例的仿真计算结果,例如下层厚度10mil,上层厚度30mil时,从图示可知上层回流占总回流的比例为25%,则下层为75%,刚好是上下层厚度比例的倒数!

三、相互干扰

当两根PCB走线靠近时,由上分析可知它们的回流会出现交叠,会相互干扰,靠得越近,交叠越多,干扰越大,如下图所示:

当d=3h时,根据前式计算可知其密度已经减小为中心位置处的10%,包含的总电流如前计算达到信号电流的79.5%,工程应用中认为d>3h时,相互交叠的影响已经比较小,可以不考虑,这就是抗串扰的走线3h准则。对于射频模拟信号,简单使用3h准则是不行的,3h准则主要针对高速数字信号线,而射频微波的模拟信号走线线,一般都是要加屏蔽的,走成共面波导 CPWG ,CPWG要求两边大面积接地,如下图所示:

CPWG两边的接地线打了很多过孔,连接到地平面上

四、CPWG接地孔怎么加?

射频板上一眼望去,都是密密麻麻的接地孔,据说密集综合症者看了会起鸡皮疙瘩。接地孔,主要就是防止干扰别人以及被别人干扰。那接地孔一般怎么打?基本规则就是遵循λg/20规则,当然此规则的要求相当低,实际操作时会进行改进。

微带线周围加"接地孔"的步骤:

(1) 首先用EDA软件计算合适的走线宽度和间距,这是在PCB叠层设计时就需要确定的参数,CPWG的信号线到两边地线的距离即是我们要知道的接地孔距离微带线的距离。计算软件可以使用si9000,这是绝大多数电路板厂家计算阻抗的工具,allegro里面的计算主要针对普通微带线,无法计算CPWG传输线。

(2) 然后按照λg/20来估算接地孔之间的距离,比如信号频率100MHz, 板材介电常数4.3,那么等效波长λg=c/(f*sqrt(Eff)), Eff为等效介电常数,由于微带线的上面是空气,介电常数为1,下面是4.3,所以等效的介电常数既不是1也不是4.3,而是介于两者之间,和介质厚度密切相关,可以借助keysight的ads里的传输线计算工具计算如下:

则λg/20=82.2mm。

对于CPWG传输线也是类似的:

如果从这个计算来看的话,整个射频板可能只需要打几个过孔就行了,不过一般射频板都是被打成筛子状,主要原因有两个:

- 如果是CPWG传输线,尽量沿着铜皮的边界打孔,保证孔的焊盘与所在的铜皮的边界重叠;在文献”Southwest microwave,Optimizing Test Boards for 50 GHz End Launch Connectors“中提到,沿着边界打接地孔,可以拓展CPWG信号的带宽。

下图是沿边界打接地孔,其S21在25GHz频率以上时明显衰减小于上图,话又说回来,有多少设计的板子需要工作在25GHz以上?所以普通的射频微波电路板,没有那么高工作频率时,可以不一定非要沿边界打接地孔,前后偏移一些问题不大

- 打密集接地孔可以增加隔离度

在文献”Peter Vizmuller, “RF Design Guide: Systems, Circuits and Equations,” 1995, Artech House“中利用波导截止频率的观点分析指出:打密集的接地过孔可以使PCB的CPWG走线向CPWG外其他地方的辐射降低数个db(3-5db),这是把射频板子打成筛子的主要原因之一,另外一个原因就是实现充分良好接地。

实际操作时,如果计算出来的λg/20比较大(通常都是这样),可以选择2mm~2.5mm的间隔打接地孔,如果λg/20比较小就适当减小间隔,但是需要保证:

- 满足PCB厂家加工要求,接地孔太密集,PCB厂家加工有问题

- 接地孔不要把其他平面层打破,这样会造成回流面积增大,容易引起信号完整性问题,特别是使用通孔时这个问题要注意,有时板子密度非常大,无法满足不要把其他平面层打破且明显引起信号完整性问题,此时可以使用埋孔或盲孔(当然成本会比较高)。

五、差分线的保护地

如果需要给差分信号加保护地,为了不破坏差分线之间的对称平衡关系,要求两边都要同时加地,而且要求地与差分线的距离至少要大于两倍的差分线的间距,如下图。

-

SMT焊接工艺介绍:回流焊、波峰焊、通孔回流焊2023-11-18 12586

-

通孔回流焊的定义2023-09-28 1922

-

分享一下波峰焊与通孔回流焊的区别2023-04-21 1777

-

通孔回流焊工艺在PCB组装中有什么样的作用2020-12-15 1269

-

通孔回流焊接工艺的特点2020-10-26 6171

-

什么是通孔回流焊工艺,在电子组装中有什么作用2020-07-09 10152

-

通孔回流焊工艺原理_通孔回流焊接工艺的优缺点2020-04-14 20392

-

通孔回流焊工艺的优点_通孔回流焊工艺的缺点2019-10-01 6202

-

通孔回流焊锡膏的选择2018-11-27 2796

-

通孔回流焊接组件的本体材料和设计2018-09-05 2233

-

通孔回流焊简述2018-09-04 2952

-

什么是通孔回流焊?有什么优点?2018-08-01 9765

-

单点接地和多点接地的接地策略2016-07-20 1078

-

回流通孔件的简易方法2010-01-25 1670

全部0条评论

快来发表一下你的评论吧 !