OPENHW开源CORE-V-MCU移植RT-Thread

电子说

描述

前期准备

开发环境:ubuntu18.04

验证示例工程

本次实验验证的平台是PLCT提供的QEMU,在Linux下的QEMU可以使用上述的笔者编译好的,也可以使用自己尝试编译PLCT提供的源码。

OPENHW提供了基于FreeRTOS的示例工程,由于使用的是PLCT提供的QEMU,所以IDE中自带的工程并不能直接使用,为了避免不必要的麻烦,本文采用PLCT提供的示例工程。

下载好示例工程,进入到app目录,执行以下命令配置编译工程:

source ../env/core-v-mcu.sh

make RISCV=xxx //xxx为工具链的路径

编译完成后将生成的cli_test可执行文件拷到qemu的安装目录,运行下述命令验证工程;

./qemu-system-riscv32 -M core_v_mcu -bios none -kernel cli_test -nographic -monitor none -serial stdio

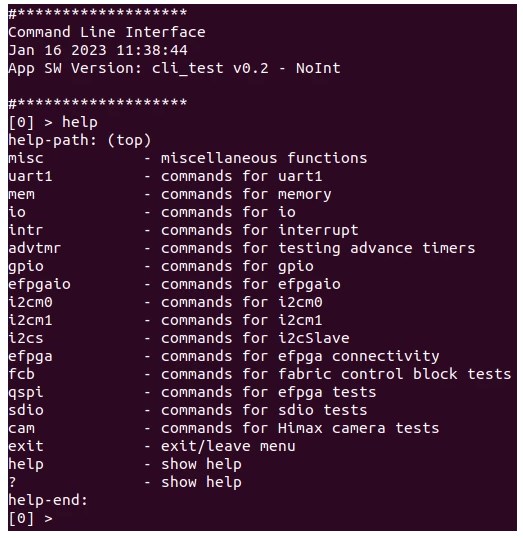

运行结果:

出现上述结果,则表示示例工程运行正常,这样我们就有一个可移植的模板工程,后续移植基于该工程开展。

移植RT-Thread

CV32E40P内核是一个RISC-V架构的内核,移植RTOS不可避免的会涉及到汇编部分的修改,所以在移植前期学习一下RISC-V架构与汇编会产生事半功倍的效果,同样在一之前需要熟悉CV32E40P的内核资源。

cv32e40p继承自pulp开源的RI5CY内核,而RI5CY内核的对接代码在RT-Thread的仓库libcpu/riscv/rv32m1已经实现,所以以RI5CY中的代码为基础,移植cv32e40p的对接代码。

成功移植RT-Thread有如下几个关键的阶段:

节拍定时器正常工作

线程可以正常创建,调度(这步最难,需要前面好多工作来保证)

shell可以正常使用(从这开始就顺利多了)

RTOS的最小时间单位是系统节拍,系统正常工作需要节拍定时器的支持,因而以节拍定时器的移植为切入点展开移植。

core-v-mcu.c中放置的是系统初始化,中断处理相关代码。其中system_init函数完成了时钟初始化,串口,I2C等外设的初始化,以及中断函数的绑定。在文件的开头可以找到如下一个指针数组:

void (*isr_table[32])(uint32_t);

该数组用于绑定中断入口函数。

for (int i = 0 ; i < 32 ; i ++){

isr_table[i] = undefined_handler;

handler_count[i] = 0;

}

isr_table[0x7] = timer_irq_handler;

isr_table[0xb] = (void(*)(uint32_t))fc_soc_event_handlzer1;

在system_init函数中我们可以找到上述代码,浏览该文件我们可以知道,timer_irq_handler即系统定时器的中断入口函数,

在原有FreeRTOS工程中该函数内容如下:

void timer_irq_handler(uint32_t mcause)

{

#warning requires critical section if interrupt nesting is used.

if (xTaskIncrementTick() != 0) {

vTaskSwitchContext();

}

}

该函数实现系统节拍的产生,所以将这里的内容修改为RT-Thread的节拍产生的方式,修改如下:

void timer_irq_handler(uint32_t mcause)

{

#warning requires critical section if interrupt nesting is used.

rt_interrupt_enter();

rt_tick_increase();

rt_interrupt_leaves();

}

涉及到中断,我们就得考虑系统的中断的实现方式,中断一般会分为向量中断与非向量中断。RISC-V常在启动后文件中进行中断模式的配置。从crt0.S文件可以找到如下代码:

/* set vector table address /

la a0, __vector_start

or a0, a0, 1 / enable vectored mode (hardcoded anyway for CV32E40P) */

csrw mtvec, a0

RISC-V规范定义中断、异常的入口地址,以及模式使用mtvec寄存器配置,上述代码将系统的中断模式配置为了向量模式,向量模式下,每个函数均包含一个独立的入口函数用来处理中断。所以我们切换至写中断向量表的文件vector.S,我们可以很明显的看到一段代码,从名字就可以看出下面是一张向量表 :

vector_table:

j freertos_risc_v_trap_handler // irq0

j freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler // irq3

j freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler //ctxt_handler // irq 7 mtime or timer

j freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler

j h7// freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler // irq 11 Machine (event Fifo)

j freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler

j freertos_risc_v_trap_handler // IRQ16

j freertos_risc_v_trap_handler // IRQ17

j freertos_risc_v_trap_handler // IRQ18

j freertos_risc_v_trap_handler // IRQ19

j freertos_risc_v_trap_handler // IRQ20

j freertos_risc_v_trap_handler // IRQ21

j freertos_risc_v_trap_handler // IRQ22

j freertos_risc_v_trap_handler // IRQ23

j freertos_risc_v_trap_handler // IRQ24

j freertos_risc_v_trap_handler // IRQ25

j freertos_risc_v_trap_handler // IRQ26

j freertos_risc_v_trap_handler // IRQ27

j freertos_risc_v_trap_handler // IRQ28

j freertos_risc_v_trap_handler // IRQ29

j freertos_risc_v_trap_handler // IRQ30

j freertos_risc_v_trap_handler // IRQ30

PS:上述向量表看的我懵了好久啊,相信对于刚接触底层不久的小伙伴也会有同样的感受吧,向量表不是一张多姿多彩的表吗,怎么感觉都一样啊???不急,我们在看一下core-v-mcu.c这个文件,又会发现一段非常显眼的代码:

void vSystemIrqHandler(uint32_t mcause)

{

uint32_t val = 0;

// extern void (*isr_table[32])(uint32_t);

isr_table[mcause & 0x1f](mcause & 0x1f);

}

结合上文,思考一下大致可以明白这个函数的作用了:分发中断。即所有的异常与中断触发后均会执行这个函数,那我们全局搜索一下这个函数,找一下是哪里调用了.全局搜索可以找到如下代码:

CPPFLAGS += -DportasmHANDLE_INTERRUPT=vSystemIrqHandler

继续搜索DportasmHANDLE_INTERRUPT可从portASM.S找到如下代码;

load_x sp, xISRStackTop /* Switch to ISR stack before function call. */

jal portasmHANDLE_INTERRUPT

j processed_source

浏览代码可知,系统触发中断或异常后最终均会执行vSystemIrqHandler函数,该函数是在freertos_risc_v_trap_handler函数中被调用,至此我们大致可以明白整个过程了,当中断或者异常出发后,会查询向量表,执行freertos_risc_v_trap_handler函数,该函数会调用vSystemIrqHandler,经其分发后最终执行到系统初始化时绑定的中断入口函数。

在RT-Thread 中由interrupt_gcc.S中的函数实现vSystemIrqHandler函数的调用,所以我们修改中断向量表的内容如下:

vector_table:

j IRQ_Handler // irq0

j IRQ_Handler

j IRQ_Handler

j IRQ_Handler // irq3

j IRQ_Handler

j IRQ_Handler

j IRQ_Handler

j IRQ_Handler //ctxt_handler // irq 7 mtime or timer

j IRQ_Handler

j IRQ_Handler

j IRQ_Handler // IRQ_Handler

j IRQ_Handler // irq 11 Machine (event Fifo)

j IRQ_Handler

j IRQ_Handler

j IRQ_Handler

j IRQ_Handler

j IRQ_Handler // IRQ16

j IRQ_Handler // IRQ17

j IRQ_Handler // IRQ18

j IRQ_Handler // IRQ19

j IRQ_Handler // IRQ20

j IRQ_Handler // IRQ21

j IRQ_Handler // IRQ22

j IRQ_Handler // IRQ23

j IRQ_Handler // IRQ24

j IRQ_Handler // IRQ25

j IRQ_Handler // IRQ26

j IRQ_Handler // IRQ27

j IRQ_Handler // IRQ28

j IRQ_Handler // IRQ29

j IRQ_Handler // IzRQ30

j IRQ_Handler // IRQ30

浏览IRQ_Handler可知,触发中断或异常均会执行该代码,该函数的主要的功能就是实现了软件保存上下文。根据RISC-V规范可知,RISC-V架构定义不支持硬件压栈,所以需要软件实现这部分,这样做的出发点大概是为了简化RISC-V架构的内核的设计吧!!!

libcpu/riscv/rv32m1中的IRQ_Handler函数存在如下内容

/* switch to interrupt stack */

la sp, __stack // 移植时需修改

/* interrupt handle */

call rt_interrupt_enter

csrr a0, mcause

csrr a1, mepc

mv a2, sp

call SystemIrqHandler // 移植时需修改

call rt_interrupt_leave

这部分的作用是,加载中断栈的栈顶地址与执行保存上文之后的工作,这里是调用SystemIrqHandler函数进行中断分发,修改如下:

/* switch to interrupt stack */

la sp, __freertos_irq_stack_top //栈顶地址 位于链接脚本中

/* interrupt handle */

call rt_interrupt_enter

csrr a0, mcause

csrr a1, mepc

mv a2, sp

call vSystemIrqHandler // 调用vSystemIrqHandler函数

call rt_interrupt_leave

在board.c的rt_hw_board_init函数中,添加如下代码:

vPortSetupTimerInterrupt();//初始化定时器

volatile uint32_t mtvec = 0;

__asm volatile( "csrr %0, mtvec" : "=r"( mtvec ) );//声明仅有一张向量表

__asm volatile( "csrs mie, %0" :: "r"(0x880) );//使能定时器中断与外部中断

至此,基本的移植工作已经完成,可以采用静态创建任务的方式,实现多任务的创建与调度。

动态内存

在board.c添加下述代码:

#if defined(RT_USING_USER_MAIN) && defined(RT_USING_HEAP)

#define RT_HEAP_SIZE (64*1024)

static rt_uint8_t rt_heap[RT_HEAP_SIZE];

void *rt_heap_begin_get(void)

{

return rt_heap;

}

void *rt_heap_end_get(void)

{

return rt_heap + RT_HEAP_SIZE;

}

#endif

在rt_hw_board_init添加下述代码:

#if defined(RT_USING_USER_MAIN) && defined(RT_USING_HEAP)

rt_system_heap_init(rt_heap_begin_get(), rt_heap_end_get());

#endif

完成上述工作便可使用RT-Thread的动态内存相关接口,同样可以种动态创建线程的函数。

shell

在链接脚本的.text段添加如下内容

/* section information for finsh shell */

. = ALIGN(4);

__fsymtab_start = .;

KEEP(*(FSymTab))

__fsymtab_end = .;

. = ALIGN(4);

__vsymtab_start = .;

KEEP(*(VSymTab))

__vsymtab_end = .;

. = ALIGN(4);

实现以下函数:

char rt_hw_console_getchar(void)

{

return udma_uart_getchar(0);

}

void rt_hw_console_output(const char str)

{

writeraw(0, strlen(str), (uint8_t )str);

}

注:writeraw函数来自udma_uart_writeraw,去掉了其中涉及FreeRTOS的API.

完成上述部分便可以使用RT-Thread的shell。

自动初始化

在链接脚本的.text段添加如下内容:

/* section information for initial. */

. = ALIGN(4);

__rt_init_start = .;

KEEP(*(SORT(.rti_fn*)))

__rt_init_end = .;

. = ALIGN(4);

添加上述代码后便可使用RT-Thread的自动初始化接口。

结果验证

在生成的目标文件的目录下,输入运行命令,示例命令:

/home/wangshun/bin/qemu-riscv/bin/qemu-system-riscv32 -M core_v_mcu -bios none -kernel rtthread.elf -nographic -monitor none -serial stdio

使用时,/home/wangshun/bin/qemu-riscv/bin/修改为用户的qemu的路径。

运行结果如下:

| /

RT - Thread Operating System

/ | 5.0.0 build Dec 16 2022 11:25:07

2006 - 2022 Copyright by RT-Thread team

Hello RT-Thread

msh >help

RT-Thread shell commands:

finshToCLI - Switch to CLI: CLI component of Core-V-MCU

pin - pin [option]

clear - clear the terminal screen

version - show RT-Thread version information

list - list objects

help - RT-Thread shell help.

ps - List threads in the system.

free - Show the memory usage in the system.

msh >ps

thread pri status sp stack size max used left tick error

tshell 20 running 0x00000160 0x00001000 22% 0x00000009 OK

tidle0 31 ready 0x000000f0 0x00000100 98% 0x1c05e62d OK

timer 4 suspend 0x000000e0 0x00000200 43% 0x00000008 OK

msh >

至此,移植RT-Thread至OPENHW开源的基于CV32E40P内核的CORE-V-MCU便移植完成。

CORE-V-MCU bsp

core-v-mcu的bsp已经合并至RT-Thread的主仓库,并配有详细的使用说明,链接。

小结

在为RISC-V移植RTOS时,笔者认为要具备RISC-V架构规范与编程规范的基本的了解,磨刀不误砍柴工嘛,虽然在写本文时洋洋洒洒写的很自在,但是在移植的过程中每遇到一个坑就会卡好久,不过也不要妄自菲薄,经过这么一个过程就好很多了,此时不禁让人感慨“两岸猿声啼不住,轻舟已过万重山”。

-

i.MX RT1170:VGLite移植RT-Thread Nano过程讲解(上)2023-11-09 4443

-

RT-Thread文档_内核移植2023-02-22 679

-

OPENHW开源CORE-V-MCU移植RT-Thread的流程2023-02-09 1499

-

OPENHW开源CORE-V-MCU移植RT-Thread2023-02-01 4285

-

RT-Thread操作系统的FreeRTOS兼容层2023-01-14 3524

-

机智云设备移植RT-Thread2022-04-19 1940

-

基于 Keil MDK 移植 RT-Thread Nano2022-01-26 1408

-

RT-Thread系统移植到STM32f1032021-12-09 1328

-

RT-Thread移植到GD32F150系列MCU2021-12-07 961

-

【国产MCU移植】移植RT-Thread到国产芯片FM33LC0262021-11-30 1263

-

【国产MCU移植】移植RT-Thread到国产芯片HC32F460PETB2021-11-23 1383

-

【国产MCU系列】在 HK32F030 上移植 RT-Thread Nano2021-11-21 1112

-

【国产MCU移植】HC32F460基于Keil MDK 移植 RT-Thread Nano2021-11-18 1448

-

移植RT-Thread的原理与方法2021-09-17 10261

全部0条评论

快来发表一下你的评论吧 !