经典电路分析:峰值保持电路

电子说

1.4w人已加入

描述

峰值保持电路是用于捕捉变化的输入信号的峰值,是利用记录仪记录峰值的关键电路,其有各种电路结构,分析也相对简单。

电路设计最简单的就是功能设计,比如设计峰值保持器,最头疼的就是设计时要求电路满足一定的指标,比如要求峰值保持器满足2mv的跟踪精度、能对4Mhz的波形进行跟踪,一下子问题就复杂了,在不讲指标要求的情况下,谈电路设计是毫无意义的,这里介绍两种经典实现:一种是TI公司的参考设计,采用高速运放;另一种是采用高速比较器的实现方式。

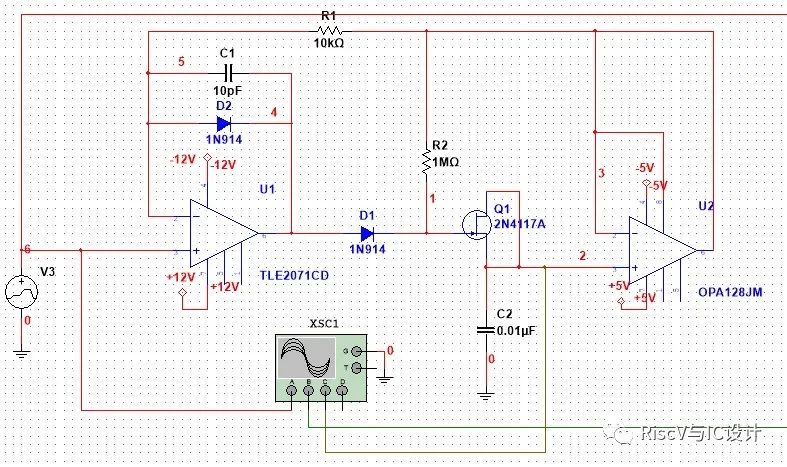

1)采用高速运放

- 此电路的Q1是保持开关,这里使用JFET原因是其反向漏电流远远小于二极管或晶体管;

- U2是TI的静电计运放,其输入偏置电流非常低,可以达到十几fA,因而电容C2基本不会向外放电;

- C2电容最好采用聚苯乙烯电容,其容量范围(100pF~0.01uF),具有负温度系数、绝缘电阻高达100GΩ、极低泄漏电流;

- D2电容的主要作用是让运放不要开环应用,始终工作在线性状态,因为运放开环应用时,其内部的放大管可能工作在深度饱和状态,当状态开关切换时会比较慢,这也是运放与比较器的最大区别!一般有指标要求时,都不会用运放当比较器使用,因为这会使运放内部管子工作在开关截止状态,开关切换速度慢。

2)采用高速比较器

此电路更加简洁,工作速度更快,可以跟踪MHz以上的信号,是非常实用的电路

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

评论(0)

发评论

-

jf_38395046

2025-05-19

0 回复 举报作者你好,我想请问一下我的峰值保持电路不能正常保持峰值,呈现平滑下降是什么原因呢 收起回复

jf_38395046

2025-05-19

0 回复 举报作者你好,我想请问一下我的峰值保持电路不能正常保持峰值,呈现平滑下降是什么原因呢 收起回复

-

NI Multisim 10经典教程分享--峰值检出电路2023-01-16 2871

-

峰值电压采样保持电路2020-01-21 18193

-

峰值保持电路设计2016-07-28 4231

-

一种实用的峰值保持电路2016-03-16 3475

-

高速脉冲峰值保持电路的设计2012-06-28 7548

-

单脉冲电压正向峰值保持电路2010-05-05 4909

-

峰值保持2电路图2009-07-17 686

-

正峰值保持电路图2009-07-15 1140

-

脉冲峰值保持电路图2009-06-20 1658

-

低漂移峰值保持电路2009-04-11 1359

-

电压脉冲峰值保持电路2008-10-20 4284

全部0条评论

快来发表一下你的评论吧 !