LogiCORE IP AXI UART 16550内核简介

描述

PG143中文文档简介

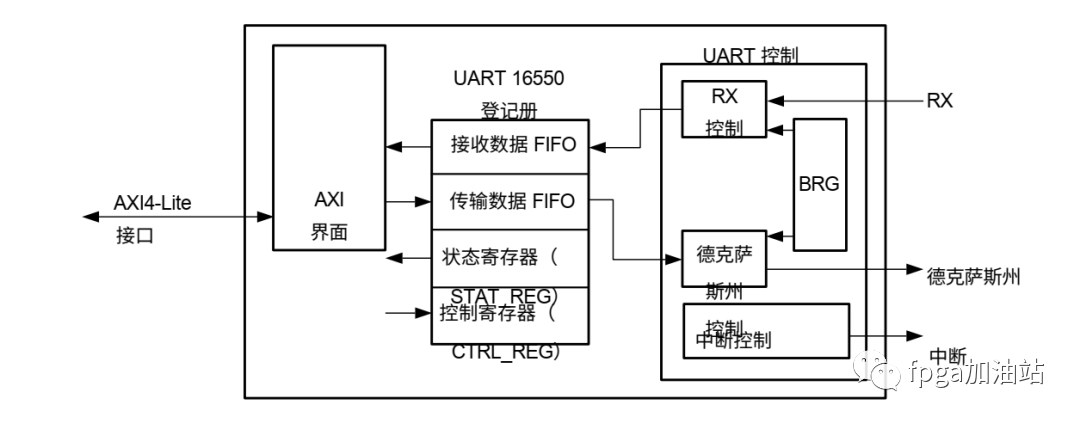

LogiCORE IP AXI 通用异步接收发送器 (UART) 16550 连接到高级微控制器总线架构 (AMBA) AXI,为异步串行数据传输提供控制器接口。该软 IP 核旨在通过 AXI4-Lite 接口进行连接。

本文档详述的 AXI UART 16550 集成了带 FIFO 的PC16550D 通用异步接收器/发送器数据表 [参考文献 1] 中描述的功能。

AXI UART 16550 IP 核实现了 PC16550D UART 的硬件和软件功能,可在 16450 和 16550UART 模式下工作。有关完整的详细信息,请参阅带 FIFO 的 PC16550D 通用异步接收器/发送器数据表 [参考文献 1]。

AXI UART 16550 内核对接收到的字符进行并行到串行转换。AXI UART 16550 能够发送和接收 8、 7、 6 或 5 位字符, 2、 1.5 或 1 个停止位,奇 偶 校 验 或无奇偶校验。AXI UART 16550 能够发送和接收 8 位、 7 位、 6 位或 5 位字符, 2 位、 1.5 位或 1位停止位,奇数、偶数或无奇偶校验。AXI UART 16550 可以独立发送和接收。

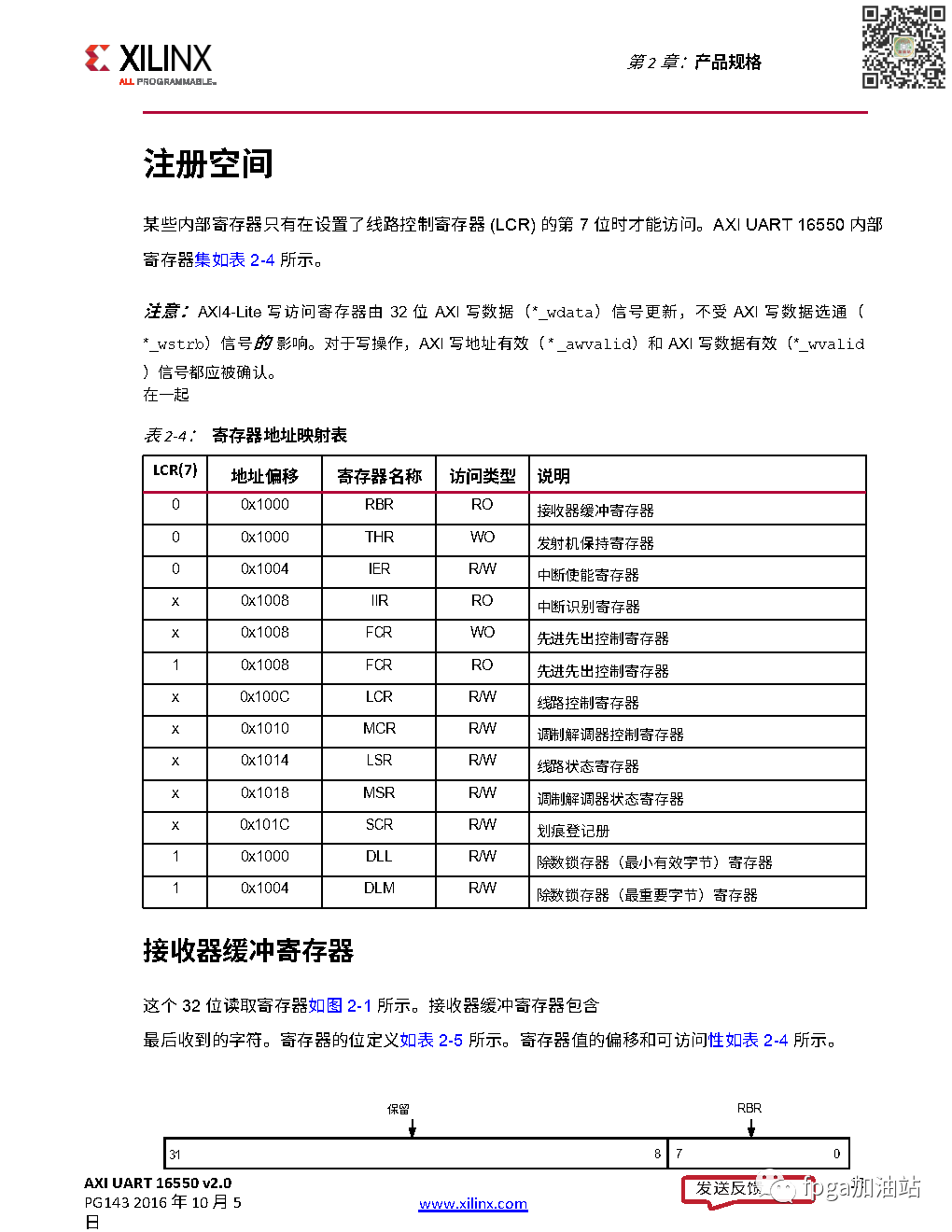

AXI UART 16550 内核具有内部寄存器,用于监控其在配置状态下的状态。该内核可发出接收器、发送器和调制解调器控制中断信号。这些中断可进行屏蔽和优先级排序,并可通过读取内部寄存器来识别。该内核包含一个 16 位可编程波特率发生器和独立的波特率发生器、16 个字符长度的发送和接收 FIFO。可以通过软件启用或禁用 FIFO。

AXI UART 16550 内核的顶层框图如图 1-1 所示

PG143中文文档前20页预览

审核编辑:汤梓红

-

如何获得UART16550的额外端口?2020-04-29 0

-

AXI UART 16550上的rx和tx端口在哪里?2019-03-22 0

-

Logicore IP CAN过滤问题2019-04-02 0

-

请问AXI UART16550无法接地额外的控制信号的原因是什么?2020-04-22 0

-

Zynq UART 16550 FIFO大小是多少?2020-05-25 0

-

UG157 LogiCORE IP Initiator/Ta2008-07-28 570

-

Xilinx的LogiCORE IP Video In to AXI42017-02-08 595

-

AXI接口简介_AXI IP核的创建流程及读写逻辑分析2018-06-29 16314

-

Xilinx Logicore IP直接数字合成器DDS的用户手册免费下载2019-09-09 1050

-

Xilinx LogiCORE IP块内存生成器的产品指南2020-12-09 999

-

LogiCORE IP AXI4-Stream FIFO内核解决方案2023-09-25 1384

-

AXI中断控制器(INTC)v4.1简介2023-10-07 1558

-

LogiCORE JTAG至AXI Master IP核简介2023-10-16 1057

-

LogiCORE IP JESD204内核概述2023-10-16 966

-

Xilinx LogiCORE IP视频定时控制器内核简介2023-10-16 573

全部0条评论

快来发表一下你的评论吧 !