ADC前端运算放大器及RC滤波器设计案例

电子说

描述

前言:

开关电源中采样电路的设计是一个重点也是难点

而采样电路更多的设计在于滤波器设计。

一般有两种形式,一种是 有源滤波器(抗混叠滤波器)+RC(用于给ADC内部保持电路提供电荷缓冲) 另一种是 单RC滤波器;

这部分内容理解起来来比较难,一方面是比较抽象,另一方面包含的知识点非常多, 讲解起来也很有难度。但也不用过于担心,实际电路设计中大多是通过调试确定参数。所以这里只需要对结论有个全面的把握,在后续的章节会逐一分解其中涉及到的知识点。

一、ADC内部电路

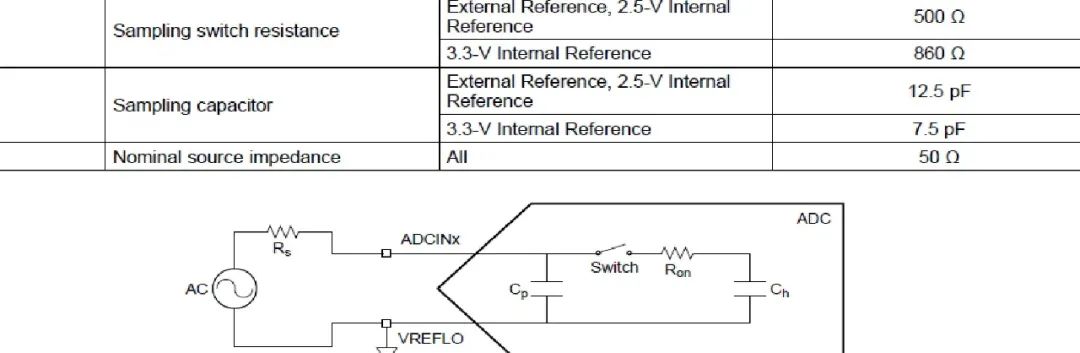

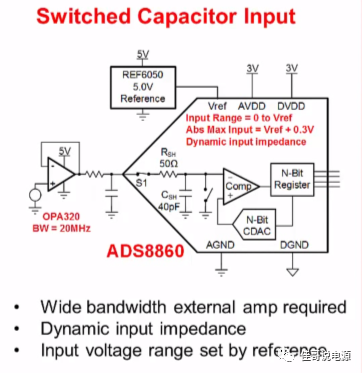

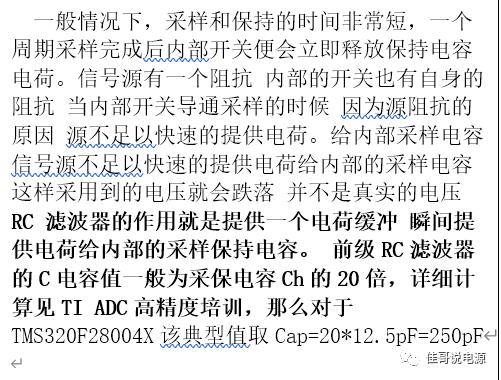

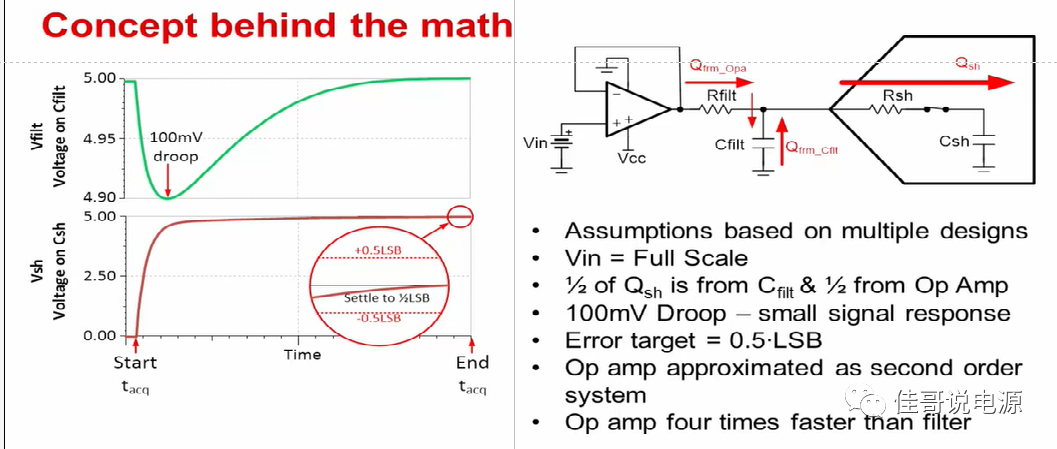

上图是TMS320F28004X内部ADC采样保持电路,其中:

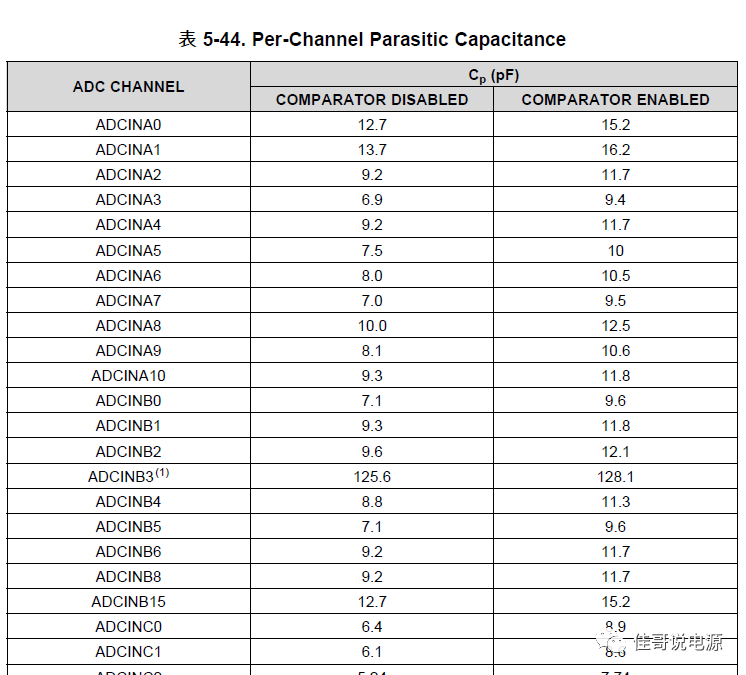

Cp: 寄生电容 Ron、Ch:采样保持器

更准确的描述应该如下图

二、抗混叠滤波器

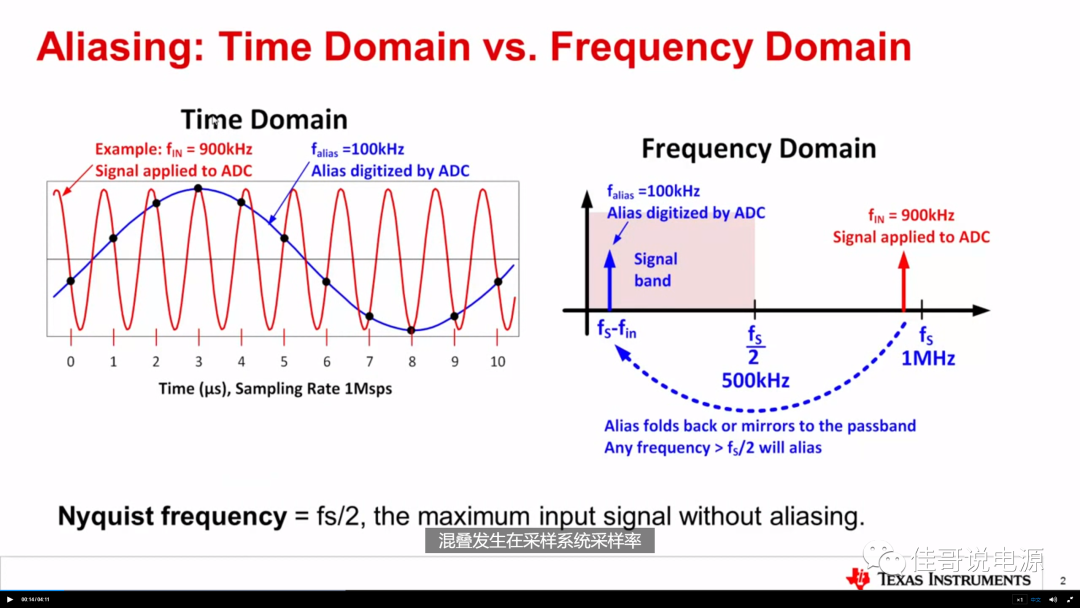

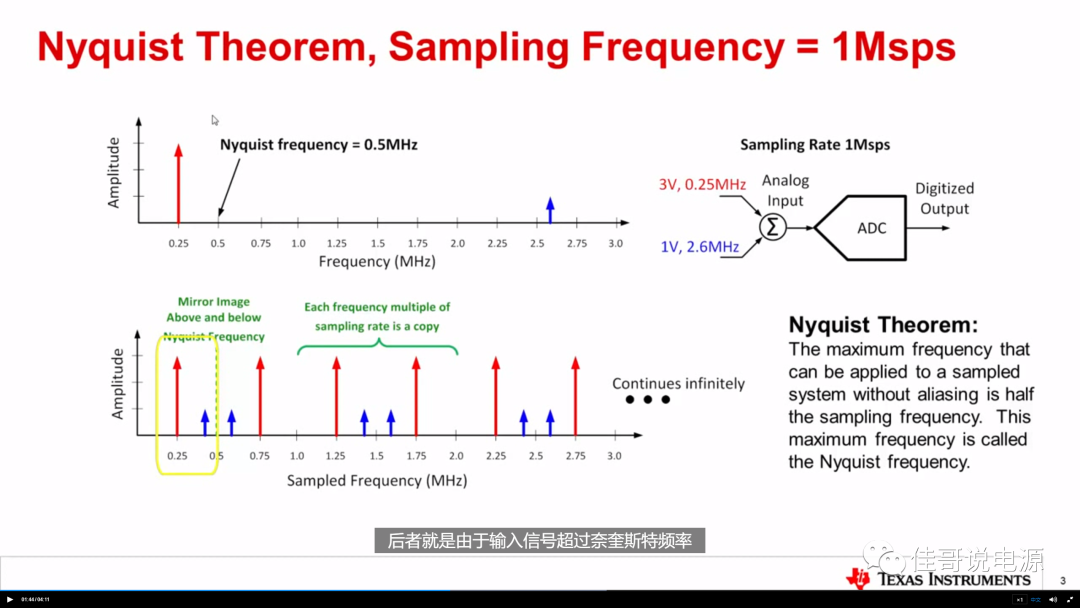

混叠是一种误差我们希望将这种误差降到最低 通常来说 混叠发生在采样系统采样率 不够快的情况下经常看到车轮转得很快但实际我们眼睛发现转得很慢 甚至反转

实际上就是眼睛的采样率不够高 导致的混叠信号 可以从时域和频域两个维度来探讨 ADC 的混叠现象 左图是时域的混叠 输入信号是 900kHz 采样率是 1M 所以每一个黑点代表一个采样点 将这些点集中起来 就是一个100kHz的信号 这个信号叫做混叠信号 实际上任何超过采样率一半的输入信号 都会产生混叠信号 这个频率限制叫做奈奎斯特频率 超过奈奎斯特频率的信号都会产生混叠。这些混叠信号(或者说噪声)会干扰真实信号,所以需要抗混叠滤波器将其滤除。

2.1、开关电源采样抗混叠滤波器选型设计

与一般的仪表或监控等只需要考虑数据精度和抗干扰性(不考虑时延或相移,可以用高阶有源滤波器获得高Q值)。开关电源是一个典型的负反馈自动控制系统,对可靠性和动态响应有非常高的要求,用于反馈的电流或电压采样信号要求尽量跟踪原信号,所以要求ADC采样滤波前后尽可能小的相位差,以获得更高的环路带宽。所以在电源里面采样一般用到的是 一阶滤波器 ,最典型的就是RC滤波器。

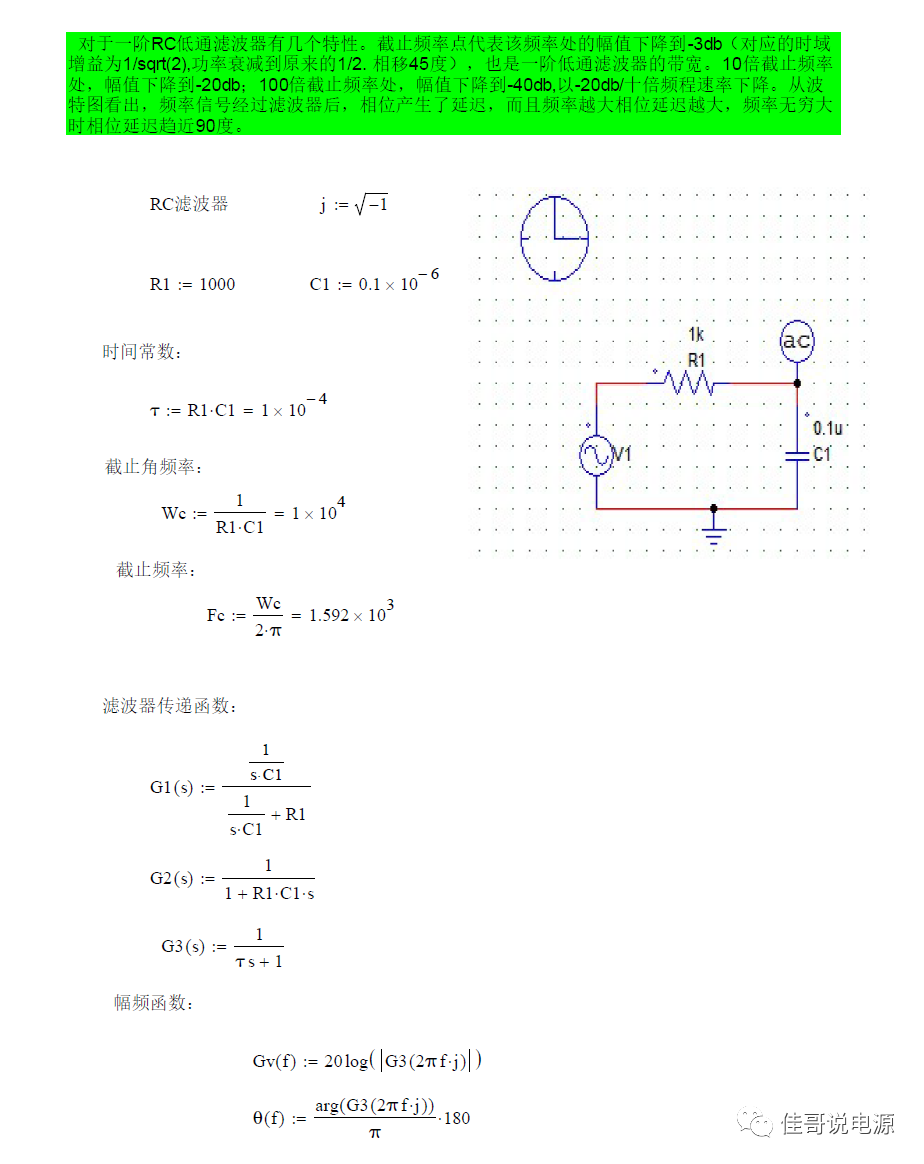

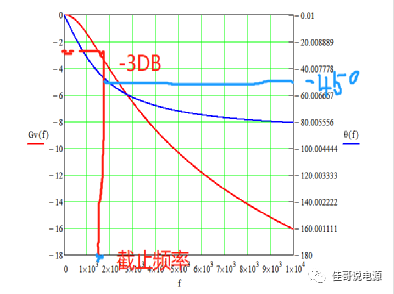

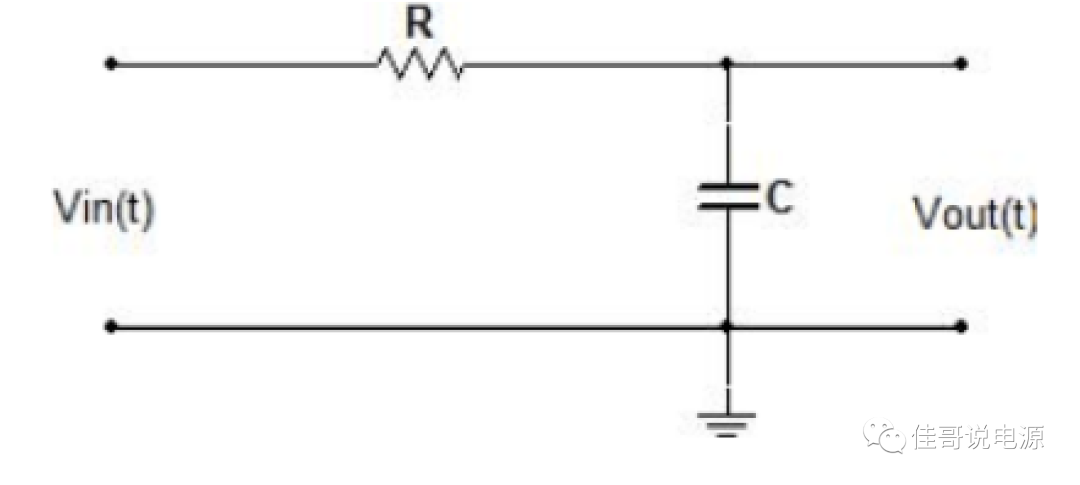

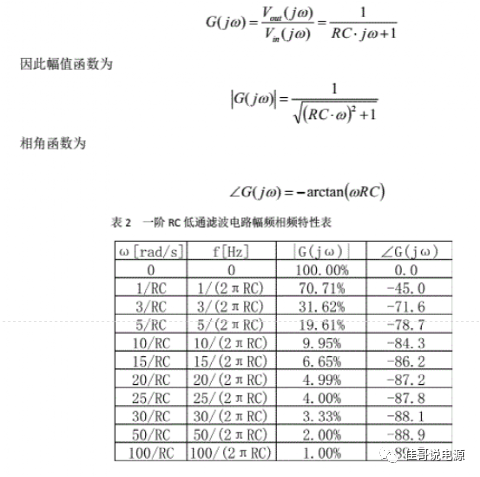

先回顾一下RC滤波器的特征:

为简化分析:假定信号为周期性方波(对于RC滤器来讲可以理解为阶跃激励信号),对于数字电源,一般是PWM周期性触发ADC,为了满足动态响应及精度,要求RC滤波器响应在每个周期开通Ton的前25%上升到待测信号95%。滤波设计主要考虑以下三点

1、 尽可能保证滤波后波形不失真

2、 尽量宽的带宽保证尽量小的相移 ;

3、尽可能衰减干扰信号

时域上的考虑:

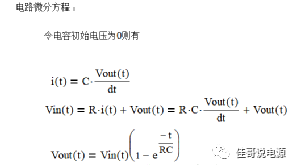

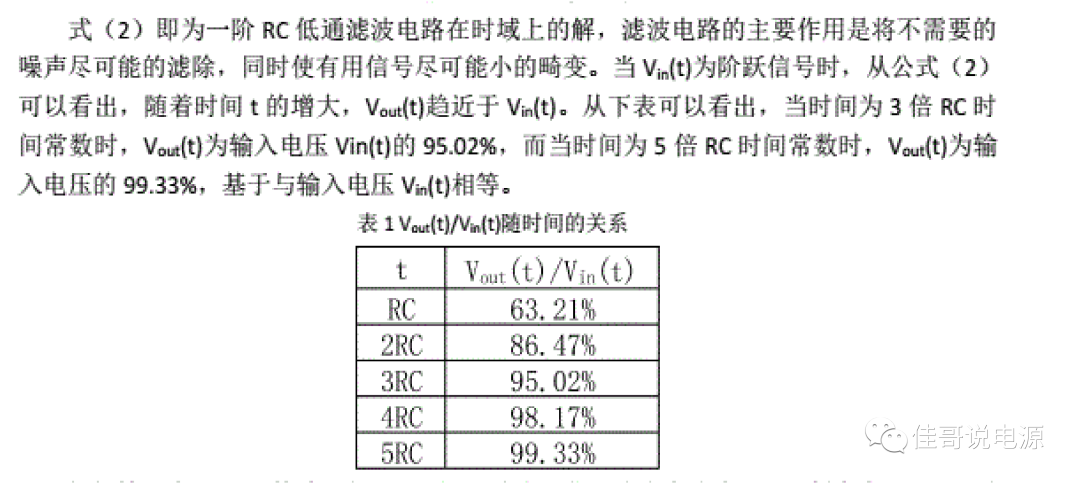

从上表可知,信号加在RC滤波器时间为1倍时间常数时,上升到信号的63.21%,3倍时间常数时,上升到原信号的95.02%。

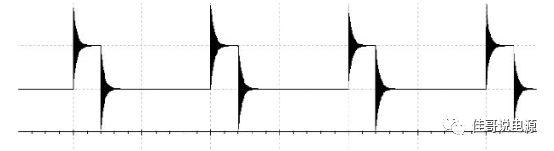

假设开关电源的开关频率为100KHZ,则ADC采样频率也为100KHZ,波形如下,该信号最小占空比为20%,频率为100Khz(周期10us),同时在上升沿和下降沿叠加了高频振荡干扰噪声。

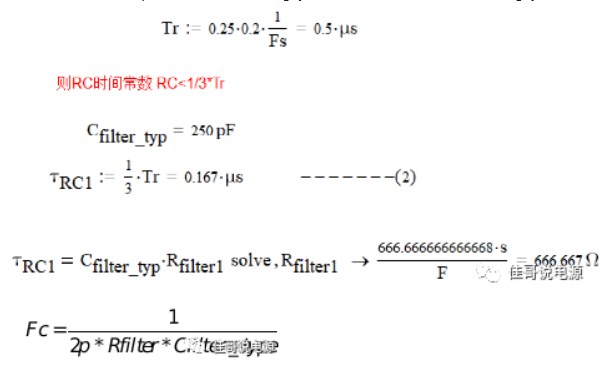

为了滤除干扰信号,并使波形尽可能小的畸变。则一阶RC低通滤波电路的时间常数不应过大。现在要求经过滤波后的信号从低电平上升到95%高电平的时间小于整个高电平时间的25%,即

Tr≤25%*20%*10us = 0.5us

因此 RC时间常数应小于Tr的1/3即

RC≤Tr/3=0.17us

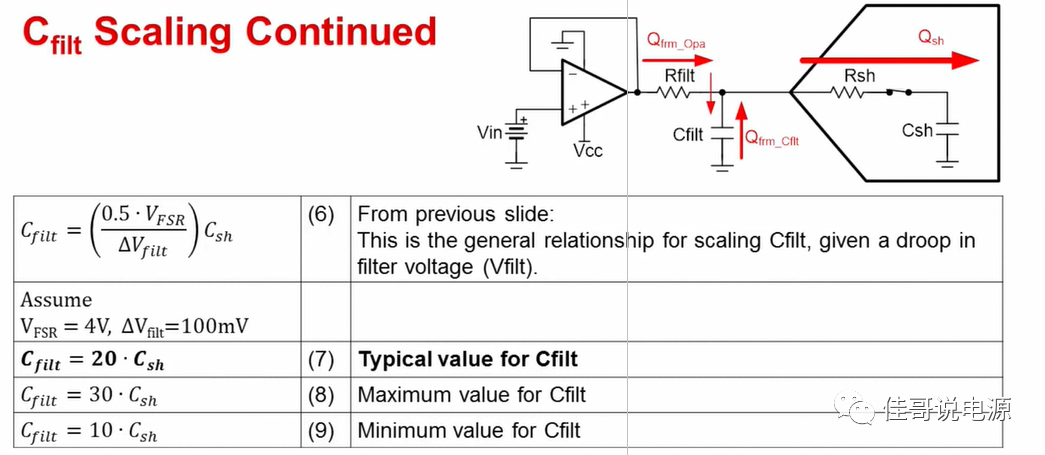

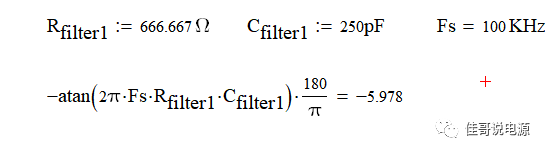

由于在采样保持电容要求RC滤波电容典型要求为20*Cap_ch =250pF,

求得RC滤波电阻为Rfilter<< span="">666.667ohm,这仅是从时域角度考虑得到的阻值,以下再从频率滤波和角度考虑

兼顾滤波效果和动态性能一般滤波器截止频率Fc选取经验值为开关频率Fs的5-10倍

取6

=600Khz

=600Khz

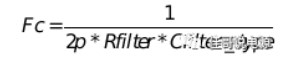

计算该滤波器的截止频率

= 954.9Khz

954.9Khz > 600Khz

对比4.5Mhz干扰信号滤波前后效果,满足要求

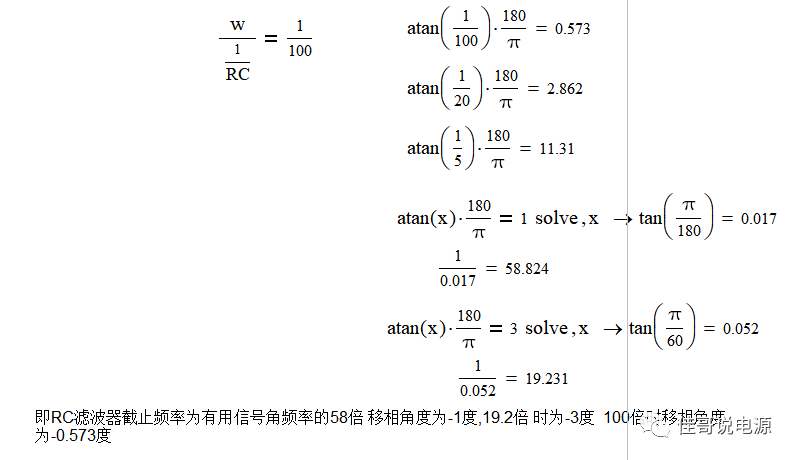

计算信号滤波前后相移

本例中:

即信号经过RC滤波器后的相移为-5.978度。

-

Texas Instruments RC4580音频运算放大器数据手册2025-07-10 1645

-

运算放大器在滤波器设计中的作用2024-12-18 2788

-

精密SAR模数转换器的前端放大器和RC滤波器的设计2023-11-24 634

-

基于运算放大器实现的信号平均器电路2023-07-15 4617

-

AN-0991: 用于标准SOIC运算放大器的有源滤波器评估板2021-03-19 868

-

如何设计RC滤波器及运算放大器的选择2021-01-16 5651

-

通用运算放大器(Op-Amp)应用及分析2020-09-15 10120

-

无源RC滤波器与有源滤波器介绍2020-07-24 5407

-

运算放大器放大信号供adc采集,运放前端需要怎么处理?需要额外的滤波降噪电路吗?2020-04-17 2580

-

运算放大器怎么构成带通滤波器?2019-09-30 2664

-

如何将单极点滤波器与运算放大器配合使用2019-07-09 3834

-

RC有源滤波器的设计2017-11-22 31949

-

精密SAR模数转换器的前端放大器和RC滤波器设计2016-01-07 1231

-

运算放大器构成的带通滤波器2009-12-07 7744

全部0条评论

快来发表一下你的评论吧 !