无线通信系统中的数字变频技术

描述

在无线通信系统中,我们经常在说基带、中频、射频、天线等物理底层,本文简单介绍中射频部分的数字变频。

数字转换是许多数字无线电系统的基本组成部分,包括在发射机将离散基带信号流上转换为高分辨率无线电信号,在接收机将高分辨率无线电信号下转换回基带信号。

在本文中,将介绍数字转换(模拟到数字和数字到模拟)的基础知识,数字上变频器(DUC)和数字下变频器(DDC)在中频(IF)和基带之间转换的功能。

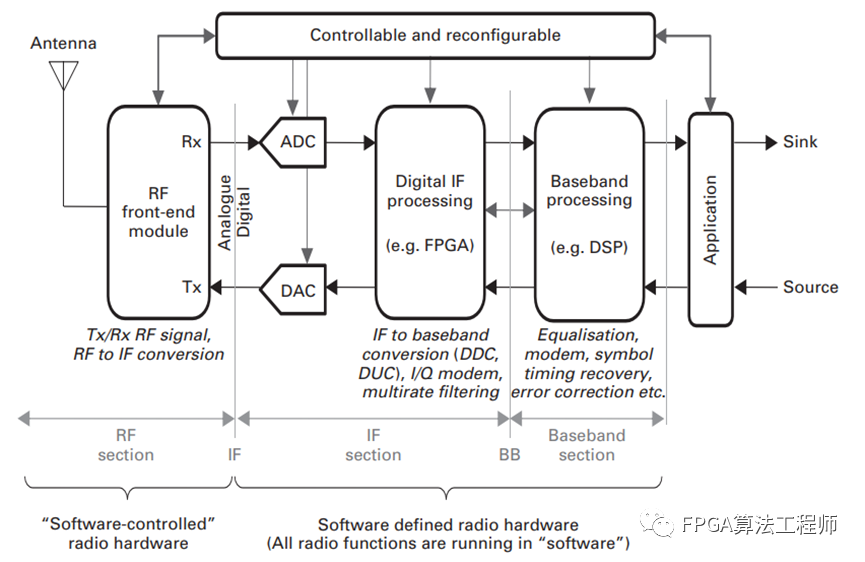

在通信系统中,DDC和DUC是射频前端(DFE)中的重要组成部分。图1示出了一个超外差架构的数字无线电收发器示例。这是一个双级转换架构,其中,在第一阶段,射频(RF)信号被下转换为中频(IF),然后,在第二阶段,它被从中频转换为基带信号。如图所示,射频、中频和基带部分的硬件部分是由软件控制和可重构的。这种无线电收发器架构被称为软件定义无线电(SDR)。

图1 SDR框图

在提出的SDR架构中,射频前端(也称为模拟前端)是唯一的模拟部分,它包括混频器、低噪声放大器(LNA)、功率放大器(PA)、射频合并器、带通滤波器(抗混叠)和天线。射频前端负责射频和中频之间的转换,并发送/接收射频信号。一些先进的射频前端允许通过软件进行一定程度的可控性,例如频率调谐。

SDR体系结构的其他部分都是数字处理组件。在中频部分,中频载波的采样和分离以及上/下频率到基带的转换由通常在FPGA中实现的数字中频处理来完成。以接收路径为例;中频信号通过模数转换器(ADC)数字化,通过数字中频处理转换为基带信号。数字中频处理执行DDC操作,如数字合成、数字NCO、数字混频器、I/Q解调、多速率抽取滤波。类似地,它以与DDC相反的顺序执行DUC。现场可编程门阵列(FPGA)等数字系统通常用于执行中频到基带转换,因为它们能够处理由于高速采样和数字转换而产生的严格实时约束。最后,在SDR体系结构的后端,基带进程主要完成符号时序恢复、均衡、调制、信道编码等数字通信功能。这些函数通常由数字信号处理器(DSP)计算,实时约束稍松。

SDR体系结构倾向于利用通用数字系统。在SDR中利用FPGA和DSP将允许在接收器上生成发射信号和调谐/检测接收到的无线电信号,通过软件进行数字操作,而不是传统的模拟信号通过单个硬件组件执行特定功能的方法。软件定义的无线电系统提供了可编程性、可重构性和可定义性的极大扩展。SDR的目标是实现一个灵活、通用和多标准的无线电系统。

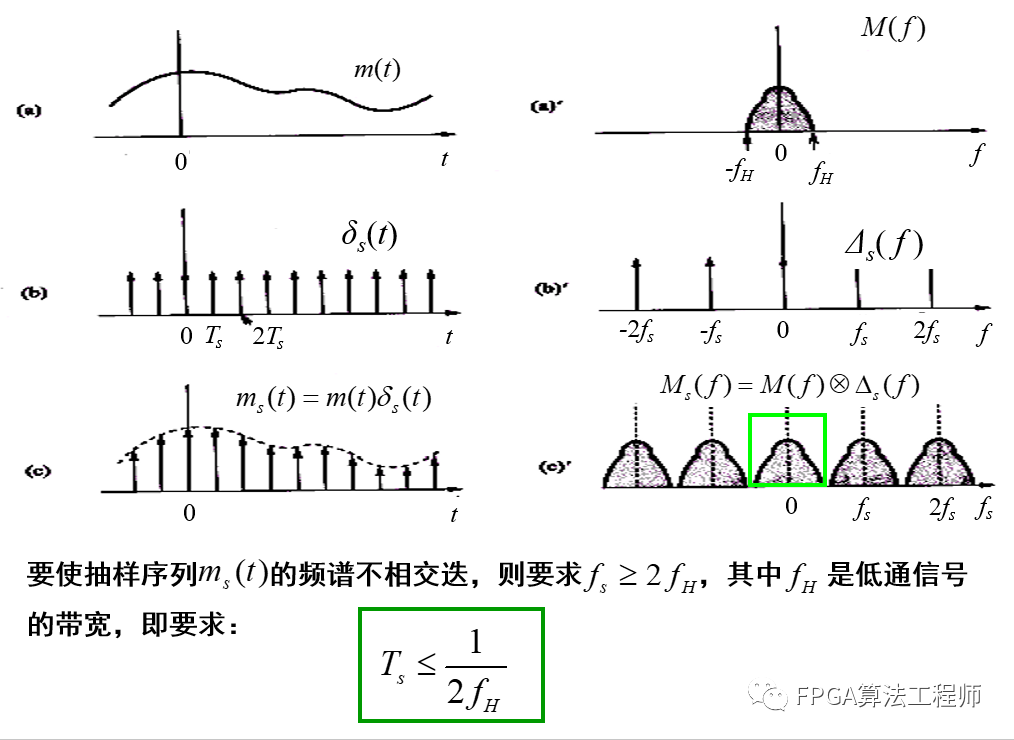

在无线通信中,奈奎斯特采样定理是DSP中一个被广泛讨论的话题,它指出采样频率Fs必须大于或等于信号最高频率分量的两倍(即)。小于奈奎斯特采样率规定的采样率会导致折叠或“混叠”效应,在这种情况下,如果需要,原始信号不能准确地转换回模拟信号。这种将模拟信号转换为数字域的方法称为低通采样。如图2所示。

图2 低通采样

低通采样可能不适用于某些应用,例如通信系统。这是因为窄带信号的带宽B与信号的上下带边频率(和)相比通常非常小,特别是在数字处理硬件无法处理如此高采样率的数据处理的情况下,以的速率使用低通采样是不实际的。

带通采样

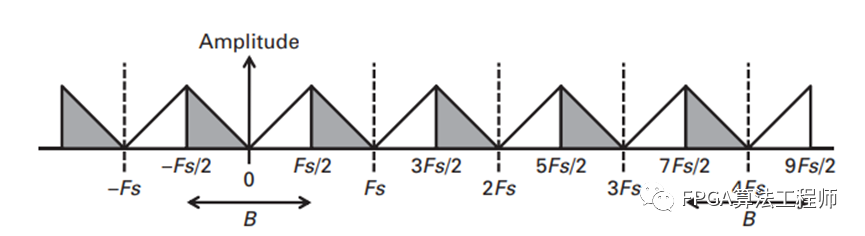

在实际设计中,采用带通采样(欠采样)可以实现对高频窄带信号的采样,并且避免混叠。该技术利用了如图3所示的采样过程引起的频谱重复。可以看出,窄带信号在采样频率的每一次倍数上重复。

使用欠采样,窄带信号可以在没有混叠的情况下以理论最小速率进行采样。但是,要求信号带边频率和为信号带宽B的整数倍;例如,其中为整数。

图3 奈奎斯特频谱重复

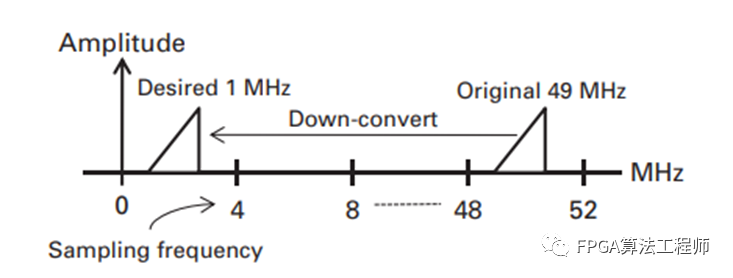

从本质上讲,带通采样也可以用作频率下变频器。图4显示了带通采样如何将49 MHz中频的信号转换为所需的1MHz中频。如图所示,原始信号从48 MHz偏移1 MHz,这是采样频率(4 MHz)的倍数。因此,应用上面讨论的原理,通过在4MHz采样信号,原始信号以1MHz的偏移量移位到直流,并实现到所需频率的转换。在DDC中,多级多速率滤波也能起到同样的作用。

图4 欠采样频率转换

根据到目前为止的讨论,使用相对低速的ADC在非常高的频率(例如中频)对信号进行采样并仍然恢复基带信息是可行的。带通采样方法可以实现高中频下变频的全数字实现,即40 MHz - 250 MHz。在实践中,还有许多其他因素需要评估,例如ADC要求,这些要求在很大程度上影响结果和整体可行性。在决定特定子采样应用的ADC之前,需要仔细分析要求,例如动态范围,抖动,时钟抖动,孔径不确定性和失真(信噪比,SINAD, SFDR)。针对特定应用的设计问题可以在许多ADC设备数据表中找到。

过采样

过采样是用明显高于奈奎斯特频率(通常是奈奎斯特频率的整数倍)的采样频率对信号进行采样的过程。对次采样信号进行过采样将具有在更宽的频率范围内传播量化噪声能量的优点。该技术通常用于DSP行业,以降低信号频带中的噪声水平,并克服ADC的一些限制,例如扩展ADC分辨率,通过可能的噪声整形降低本底噪声,从而可以使用更低的分辨率。通常,四次过采样可以提高6dB的信噪比,并为ADC的位宽增加一个额外的位。

抗混叠滤波

抗混叠滤波器通常用于数字处理系统的输入和数字中频处理过程中。要数字化的模拟信号除了折叠频率之外还可以包含频率成分,例如高频干扰。因此,为了满足采样要求,使用抗混叠滤波器来限制信号带宽,从而去除折叠频率以上的所有频率分量。其优点是在满足采样要求的同时,信号和图像光谱之间的距离更宽。对于不以直流为中心的信号,抗混叠滤波器通常是带通滤波器。在这种情况下,滤波器通常用于射频和/或中频的通道选择。低通抗混叠滤波器通常用于数字中频处理,特别是数字混频器、谐波抑制、频谱屏蔽等。抗混叠滤波器设计的一般经验法则是在通带纹波、相位线性、群延迟和通带与阻带之间的陡峭过渡方面实现良好的性能,同时插入损耗最小。

基带信号基本上是在一个分配的和专用的射频频段上传递的,该频段通常在MHz和GHz范围内。超外差无线电结构使数字系统在处理基带和中频之间的频率转换时更加灵活。在数字域,频率转换从中频到基带进行下变频,从基带到中频进行上变频。

频率下变频的操作包括:

选择目标窄带信号并采样到数字域;

通过数字信道滤波将其与宽带源隔离;

将所选窄带信号的频率降低,通常从中频转换为基带;

将数据速率降低到基带信息速率的整数倍。

频率上变频的操作包括:

将窄带信号源的频率向上转换,通常是从基带到中频;

结合多个窄带信号进行上转换;

将数据速率提高到数字中频速率。

为了进行上述操作,需要几个重要的信号处理模块,如直接数字合成器(DDS)、混频器、数字滤波器和多速率滤波器。

DDS

直接数字合成器(DDS),有时称为数控振荡器(NCO),是一个简单的函数,产生正交正弦波,即正弦和余弦,用于DDC和DUC,也用于数字调制器。DDS使用带有查找表的寻址方案来创建具有所需频率的正弦波。在实际实现中,查找表存储正弦和余弦波形的数值表示。

数字混频器

数字混频器只是一个算术函数,它将输入的数字源信号(即I和Q)与由NCO生成的载波波形(即正弦和余弦)相乘。在DUC中,数字混频器与正交调制器一起使用,以产生所需频率的单边带中频发射信号。类似地,在DDC中,将单边带中频接收信号馈送到正交解调器中,以便将其区分为I和Q信号。

数字滤波器

有限脉冲响应(FIR)滤波器广泛应用于DUC和DDC实现中,与无限脉冲响应(IIR)滤波器相比,FIR滤波器可以在其实现中实现具有无条件稳定性的精确线性相位响应。这对于确保频率转换处理(上/下转换)后输出信号的表示很重要,这可能涉及几个阶段的滤波。正是由于这个原因,为了实现DUC和DDC的稳定实现,使用了不同类型的FIR,例如积分梳状滤波器(CIC),多相插值器和抽取器。

DDC与DUC

超外差接收机是一种众所周知的接收机结构,其中射频信号被转换成中频频率,然后由ADC采样,并由DDC进行数字处理。在DDC中, I/Q分量被提取并解调到基带。由于中频和基带的采样率不同,需要多速率滤波器来实现采样率转换。

类似地,在发射端,基带信号被上采样到中频采样频率。频谱需要通过I/Q调制转换到相应的中频通道。在此之后,中频信号进行DAC转换和上变频到RF频率。

审核编辑:汤梓红

-

无线通信频谱分析仪的技术原理和应用场景2024-11-07 3845

-

测量与控制用无线通信技术介绍及目录2009-11-18 3694

-

WiMAX无线通信技术2010-04-24 1986

-

智能电网中的无线通信技术解析2012-02-23 4391

-

无线通信技术2013-03-29 3665

-

大话无线通信2015-03-28 3862

-

无线通信在应用中的优势2020-05-27 1708

-

浅谈无线通信技术的应用2021-07-22 3573

-

现代无线通信系统电波传播2010-03-15 778

-

无线通信系统的类型2009-06-30 5176

-

无线通信系统中的闭环MIMO技术综述2010-01-16 1027

-

光无线通信技术,光无线通信技术是什么意思2010-03-12 2682

-

嵌入式系统无线通信技术研究2017-11-24 1451

-

无线通信技术的应用2023-05-10 3388

-

无线通信系统的基本结构2023-05-24 698

全部0条评论

快来发表一下你的评论吧 !