数字电路实验—4位奇偶校验器设计

电子说

1.4w人已加入

描述

实验目的

- (1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;

- (2)通过实验理解和掌握奇偶校验器原理;

- (3)掌握用Verilog HDL描述奇偶校验器的方法。

实验任务

设计一个4位奇偶校验器电路。要求当输入的4位二进制码中有奇数个“1”时,输出为“1”,否则输出为“0”。

实验原理

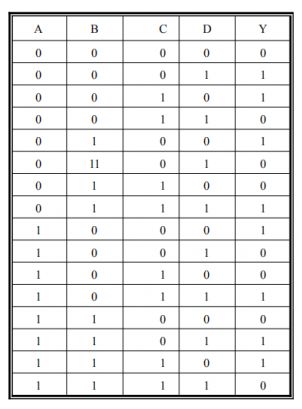

奇偶校验,即判断输入变量中1的个数。当输入变量中1的个数是奇数时,输出为1。当输入变量中1的个数是偶数时,输出为0。真值表及逻辑表达式如下所示:

Y=A’B’C’D+A’B’CD’+A’BC’D’+A’BCD+AB’C’D’+AB’CD+ABC’D+ABCD’

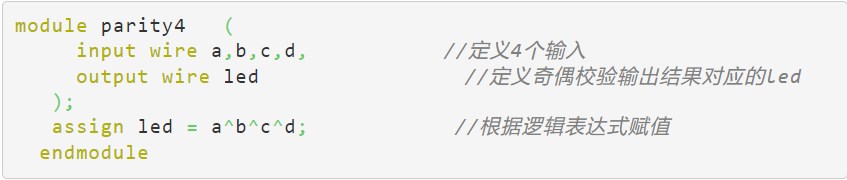

经过化简得到:Y=A⊕B⊕C⊕D

逻辑电路

Verilog HDL建模描述

实验步骤

- 打开Lattice Diamond,建立工程。

- 新建Verilog HDL设计文件,并键入设计代码。

- 综合并分配管脚,将输入信号(a,b,c,d)分配至拨码开关(M7,M8,M9,M10),将输出信号led分配至板卡上的LED(N13)。

- 构建并输出编程文件,烧写至FPGA的Flash之中。

- 改变拨码开关,观察输出结果。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

8位到9位奇偶校验总线收发器数据表2024-05-15 462

-

什么是奇偶校验 奇偶校验的基本原理 奇偶校验电路什么意思2023-10-17 6005

-

FPGA奇偶校验的基本原理及实现方法2023-05-14 4467

-

UART中有奇偶校验位和无奇偶校验位的数据传输是怎样的?2022-12-08 1212

-

增强FIFO模式下的奇偶校验2022-11-02 1928

-

单片机串口分析起始位停止位奇偶校验位2021-11-20 1877

-

stm32串口奇偶校验2021-07-23 12734

-

奇偶校验器_奇偶校验设计程序2011-11-11 6095

-

奇偶校验码,奇偶校验码原理是什么?2010-03-17 63675

-

奇偶校验器,奇偶校验器是什么意思2010-03-08 2604

-

奇偶校验码2009-10-13 5803

全部0条评论

快来发表一下你的评论吧 !