射频识别技术漫谈(21)——RC系列射频芯片的天线设计

电子说

描述

个人感觉使用RC系列射频芯片开发卡片读写器,主要的关键点有两个,分别涉及硬件和软件。软件上的关键是如何正确设置RC系列射频芯片内部的64个寄存器,硬件上的关键则是RC系列射频芯片的天线设计。天线提供了卡片和读写器交换数据的物理通道,直接决定了读写器的读写性能和读写距离,在此基础上加上对64个寄存器的正确操作,读写器才能正常高效的工作。

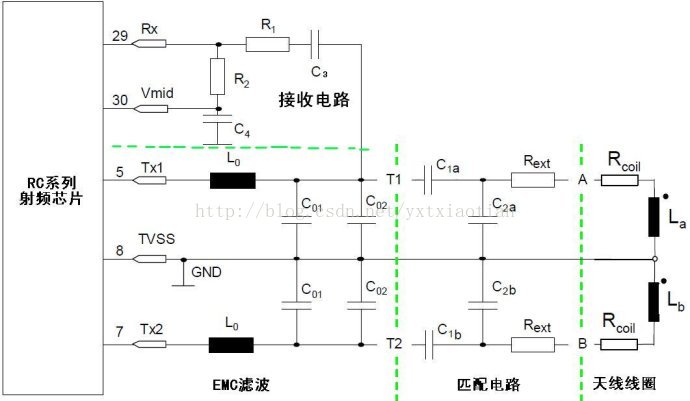

在数字电路中设计模拟信号的天线还是比较复杂的,因为天线设计牵扯到好多因素,诸如电磁感应、场强、共振、干扰、Q值等等。好在芯片的制造商为了推销产品,多数都提供了参考的电路设计,芯片的使用者在参考电路的基础上设计自己的电路,则要容易的多,RC系列芯片的天线设计也提供了参考电路,如下图所示。

天线结构上可以分为四部分:EMC滤波、匹配电路、天线线圈和接收电路。

EMC滤波电路是一个低通滤波,L0为1uH,C01和C02都是68pF,这些都是典型值,实际电路中可以围绕典型值上下调节以满足设计要求;

天线电路中的天线线圈直接布线在PCB板上,采用中间抽头接地的对称方式,一般的应用中天线直径4-6公分,天线直径直接影响读卡距离,直径小读卡距离近,但也并不是直径越大越好。天线的圈数一般2-6圈,也就是说对称接地的情况下每一边1-3圈。

匹配电路用来连接天线电路和EMC滤波电路,匹配电路中的电容与天线电感组成谐振电路。C1a和C1b可取16pF或27pF,对读写距离影响不大,C2a和C2b是谐振电容,这两个电容值非常关键,它们直接影响谐振程度,进而影响天线电压的振荡幅度,最终影响读写距离。通常天线电压的峰峰值大于10伏就可以读到卡片,也并不是峰峰值越大越好,还要看卡片或标签上天线的大小、天线周围的干扰,尤其是金属干扰等因素。C2a和C2b通常可在82pF-220pF的范围内调节。

接收电路中的C3容量为1nF,C4为100nF,R1与R2组成分压电路,R2固定为820Ω,R1根据天线的震荡幅度在470Ω-10KΩ的范围内调节,典型值为2.2KΩ。

电路中的电阻和电容一般使用0402、0603或0805的贴片封装。稳定性要好,误差不能太大。

以上的参考电路可以说是懒汉设计法,更好的设计应该使用精密仪器,严格测量天线的电感值,等效的电容值,然后用公式计算,并对天线的Q值进行校核。不过估计大部分开发人员的测量工具也就仅限于万用表和示波器,在此情况下,使用参考电路基本上能满足要求。

设计读写器天线的时候,通常我们最关心的指标是读写距离,影响天线读写距离的因素主要有以下几方面:

(1)读写器和卡片的天线尺寸

(2)天线本身的匹配程度

(3)天线和匹配电路的品质因数

(4)读写器的功率

(5)环境影响

卡片上天线的尺寸我们没办法改变,我们只能设计天线的大小。好像有个理论说最大设计的读写距离应该等于天线的半径,而RC系列芯片的最大操作距离都是10公分,我们总不能做个直径20厘米的天线吧,除非特殊要求,这样的巨无霸很难有市场。

天线的匹配程度、品质因数和功率通过调整参考电路的元件参数是可以调节的。周围环境影响因素中金属干扰最为严重,金属干扰将导致操作距离减小,数据传输出错。金属与读写器天线之间的距离应大于有效的操作距离,为减小金属的影响,应使用铁氧体进行屏蔽。最好金属与天线的距离大于10cm,最小也要3cm,而且使用紧贴的铁氧体屏蔽。

另外,设计天线时为天线增加屏蔽可以有效抑制干扰,比如天线设计使用4层板,在两个中间层布天线线圈,在顶层和底层对应中间层线圈的地方布上一圈屏蔽地,当然这一圈屏蔽地本身不能闭合。

调整天线的最好方法还是直接用卡片或标签试验,边调节元件参数边测试读写距离,直到满足设计要求为止,时间长了,对天线电路的习性就心中有数了。

审核编辑 黄宇

-

射频识别技术漫谈(29)——射频接口芯片TRF79602023-11-14 2318

-

射频识别技术漫谈(25)——Felica简介2023-10-20 5555

-

射频识别技术漫谈(22)——RC系列射频芯片的寄存器操作2023-10-17 2305

-

射频识别技术漫谈(16)——Mifare UltraLight2023-10-16 4656

-

射频识别技术漫谈(10)——识别号的格式变化2023-10-11 2981

-

射频识别技术漫谈(8)——动物标签2023-10-10 2225

-

射频识别技术漫谈(1)——概念、分类2023-10-09 2191

-

基于RC系列射频芯片的天线设计2019-07-12 2142

全部0条评论

快来发表一下你的评论吧 !