FSMs低功耗设计

电子说

1.4w人已加入

描述

低功耗FSMs

低功耗设计是当下的需要!这篇文章:低功耗设计方法论的必要性让我们深入了解了现代设计的意图和对功耗感知的需求。在低功耗方法标签下的时钟门控和电源门控的后续文章中,讨论了一些SoC低功耗设计的方法。在这篇文章中,我们将考虑一个这样的低功耗设计的FSM,可以推广到任何低功耗时序电路的设计。

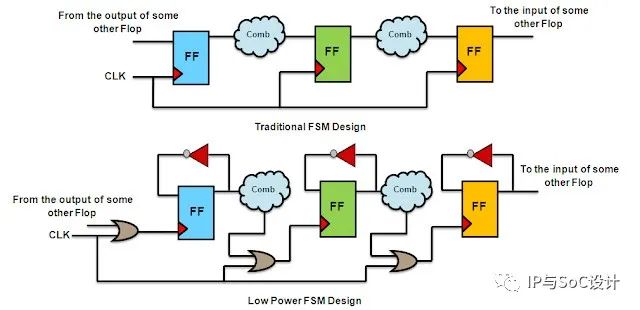

考虑以下传统和低功耗FSM的通用设计:

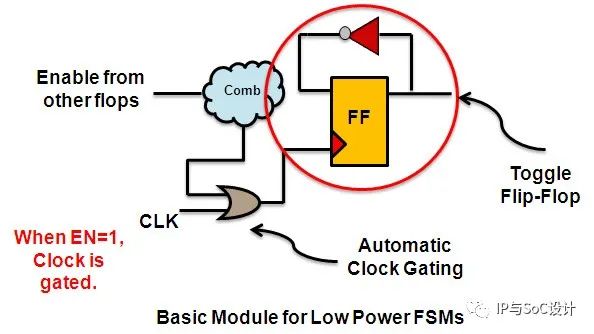

让我们来讨论一下我们在这里使用过的基本构建块。"或"门作为触发器的时钟门。我们使用的触发器是一个触发器。当 enable = 0 时,触发器接收时钟,并切换其状态。所以,每当我们需要改变翻牌的状态时,我们可以给出一个时钟脉冲。

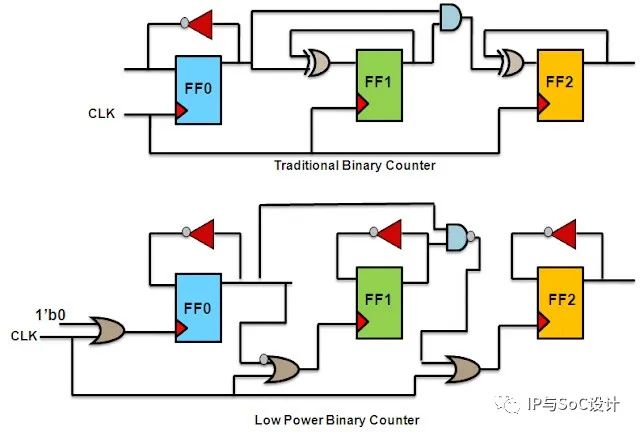

说得够多了!现在我们来讨论一个基本同步计数器的真实例子。以及如何利用上述方法设计一个低功耗同步计数器。

在任何二进制计数器中:

·最低阶位在每个时钟周期后切换。

·只有当所有低阶位都在逻辑1时,任何高阶位才进行切换。

记住这一点,我们现在可以建立低功耗计数器!!

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

什么是低功耗设计,如何评估低功耗MCU性能?2025-12-12 178

-

#硬声创作季 #STM32 手把手教你学STM32-044 待机唤醒实验-低功耗-M4-1水管工 2022-10-29

-

超小蓝牙模组,远距离,低功耗#蓝牙芯片 #低功耗蓝牙 #物联网 #硬声创作季fly 2022-08-23

-

基于ESP32的低功耗蓝牙触摸键盘迪文智能屏 2022-04-07

-

低功耗设计2021-11-06 1136

-

低功耗WiFi模块和低功耗蓝牙模块哪个好2021-01-04 2080

-

超低功耗MCU如何降低功耗2020-11-12 2667

-

什么是低功耗,对FPGA低功耗设计的介绍2020-10-28 3927

-

还在了解什么是低功耗?FPGA低功耗设计详解2020-10-26 3831

-

AD,低功耗2018-06-21 2750

-

低功耗蓝牙怎么低功耗?如何界定2018-02-06 3852

-

【专题】低功耗电路设计__低功耗设计技巧2015-06-29 4002

-

低功耗电路设计_低功耗设计方法2015-06-27 10312

全部0条评论

快来发表一下你的评论吧 !