FPGA数字信号处理-FIR滤波器及AM解调

电子说

描述

1.AM解调概论

AM解调中一般的方式是进行全波整流或者半波整流,然后经过一个低通滤波器即可。

本文为数字AM解调。本文采取全波整流加FIR低通滤波器的方式进行解调。

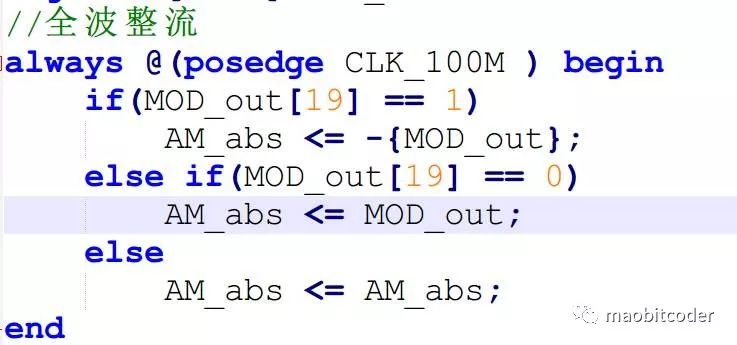

在数字通信系统中一般全波整流实现方式就是取绝对值,半波整流就是直接舍弃负值。

下面一小段代码就是取绝对值的。

那为什么取绝对值,然后经过低通滤波器就能出来包络信号呢?关于此处的理论推导。去看书吧。

2.FIR滤波器概述

FIR滤波器是什么样的结构,有什么样的特性等等等为了避免大家烦我在这里就不抄课本了。接下来我们就简单的理解下FIR滤波器。

注意本说法仅仅为新手入门了解。直观了解FIR滤波器的特性。许多定义和概念可能存在纰漏。希望广大读者理性参考。

FIR滤波器的结构如下:

我们假设图中的n就为10。接下来我们抛开FIR这个概念。假设我就是要实现10个数字取个平均数。那么我只要让h(0),h(1),h(2)……h(9),均为0.1。那么每个数字进来被乘以0.1。然后把10个数字加起来。这就是一个均值滤波。(这种把两组数据对应相乘然后再加载一起的操作就是卷积的概念)。

依据经验我们知道,当取的数字越多(即n越大)这个滤波器的输出值就更稳定。消耗的资源对应着也会越多。

上述举得例子为求均值。但是假设说我们现在要做更复杂的需求,比如滤除一定频率的波形。那就需要更加准确的计算各个参数。所幸我们生于伟大的时代,有很多工具可以代替我们算出更合适的抽头系数。例如matlab的FDATools以及FilterSolutions 2015。

3. FIR滤波器 参数计算

打开Filter Solutions这个软件。选择数字滤波器(这个工具功能十分强大,可以设计有源,无源,微带线,数字等等不同种类的滤波器)。

打开软件设置如下,因为再实现的时候FIR滤波器采用了完全对称的结构。我们选择一个125阶的FIR滤波器。选一个合适的窗函数,至于不同的窗函数有什么不同的性能表现在这里就不赘述了。

由于我们的包络信号是1M。选择一个2M的低通滤波器。

左上方有各种选项,我们来查看一下它的频率响应。看起来还是可以的。

然后点击右上角的SynthesizeFilter、

点击选项卡的Vec选项,然后Copy Num/Den ,FIR滤波器的抽头系数就复制到剪切板上了。

4. FIR滤波器 XILINX IP核实现

添加一个FIR滤波器,把系数复制进去(注意只复制括号内的内容)。

可以看到左侧的频率相应图。其中红色线为设计的参数。蓝色线为经过定点量化后的抽头系数的频率响应。图中的横坐标为归一化的频率(不知道什么叫归一化频率的自行百度),纵坐标为幅度的衰减。可以看到设计效果还是可以的。

滤波器也可以选则抽取或者插值或者希尔伯特或者最简单的单速率滤波器。关于抽取核插值我会在后面更新的文章中写出,希望大家持续关注。

为了节约资源我们可以设计成抽取滤波器。但是为了避免造成大家的困惑,本文中依然采用单速率的滤波器。

我们进行第二页的设置

时钟频率核输入采样频率均为100M。

接下来进行第三页的设置最上面的哪个就是抽头系数的相关设置,在这里我们可以调节量化(定点化)的参数。从而让前文提到的红线和蓝线更接近(即实现效果更接近设计效果)。当然调节不同的参数,其资源占用和性能表现也会有所不同。下面的几个选项大家可以自行研究。

后面两页内容是设计实现时的面积或者速度优化啥的。大家自行研究在本设计中不做修改。

在implementation Details (实现细节中)可以看到数据的输出格式。其中定点数为[34:17]。也可以发现资源占用为63个乘法器,因为本设计中的FIR滤波器为对称结构。所以可以省下一半的资源。

这样我们的FIR滤波器就基本设计完成了。

5. FIR滤波器 XILINX 实现与验证。

这部分的代码比较简单,我们讲上节课的Modout信号接出来后进行取绝对值。得到的信号是20bit的。我们选取其中的高16bit送入FIR滤波器。然后就可以得到输出了,FIR滤波器的输入输出信号还有一些有效,握手信号之类的,大家自行查阅手册了解。

接下来进行仿真,仿真中我们把FIR输出的[33:17]位单独拿出来进行显示即可。最终效果如图。

-

DSP in FPGA:FIR滤波器(一)2014-06-27 10985

-

DSP in FPGA:FIR滤波器(二)2014-06-30 2599

-

进群免费领FPGA学习资料!数字信号处理、傅里叶变换与FPGA开发等2025-04-07 15070

-

【参考书籍】基于FPGA的数字信号处理——高亚军著2012-04-24 13951

-

什么是fir数字滤波器 什么叫FIR滤波器2008-01-16 17659

-

基于MATLAB与FPGA的FIR滤波器设计与仿真2012-09-25 1326

-

数字信号处理的FPGA实现2015-12-23 1049

-

轻松设计数字FIR滤波器2017-06-07 1009

-

基于FPGA的硬件加速器的FIR流水结构滤波器实现、设计及验证2017-11-18 2196

-

FPGA的FIR抽取滤波器设计教程2018-04-28 1676

-

基于FIR滤波器结构实现级联型信号处理器FPGA的设计2019-04-22 7509

-

如何使用FPGA实现FIR抽取滤波器的设计2020-09-25 1182

-

FIR滤波器代码及仿真设计2023-06-02 2758

-

IIR滤波器和FIR滤波器的区别2023-06-03 21059

-

基于FPGA实现FIR数字滤波器2024-11-05 3020

全部0条评论

快来发表一下你的评论吧 !