一种基于逐次逼近的压阻式加速度计低功耗CMOS接口电路

电子说

描述

本文提出了一种基于逐次逼近的压阻式加速度计低功耗CMOS接口电路。该接口电路包括放大器、累加器、比较器、双向可逆计数器、锁存器、启动控制逻辑和D/A转换器。该电路通过电流传感结构检测压电电阻的变化,并使用一个简单的一阶delta-sigma调制器将产生的输入电流转换为输出数字位流。

仿真结果表明,该电路在单电源3.3 V运行的情况下,可以达到60 dB的信噪比,非线性误差小于0.25%。该电路适用于单片机CMOS智能传感器。

接口电路结构

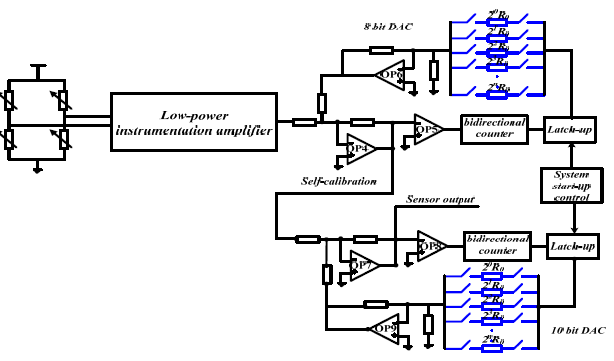

接口电路总框架如下:

它通过二阶逐次逼近校准传感器的零点偏移。整个电路由放大器、累加器、比较器、双向可逆计数器、锁存器、启动控制逻辑和D/A开关组成。当电路处于初始状态时,输入差分信号,放大的零漂移电压与D/A开关的输出校正电压输入到累加器。因为D/A开关在这里作为反馈网络,其输出极性与仪表放大器的输出极性相反,将二者相加可以消除零点漂移。

双向计数器根据比较器的输出结果进行加减运算。从而相应地增加或减少双向计数器的八位数输出转换而来的电压。通过重复上述过程,累加器的输出电压将逐渐接近电路的中心电压。然后启动控制逻辑单元,使锁存器保持当前数字信号,完成零点漂移校正。

电路启动后,八位双向可逆计数器处于原始状态,输出为00000000。这个输出被发送到D/A开关后的锁存器。D/A开关VREF的参考电压为1.65 V。仪表放大器和D/A开关的输出电压相减。得到的值与电路的中心电压同时输入比较器进行比较。

如果输出电压较大,比较器输出为1,双向计数器为减法模式,输出为11111110;如果中心电压较大,比较器的输出为0,双向计数器为加法模式,输出为00000001;计数器的数字输出在锁存器后发送到D/A开关。如果累加器的输出电压高于中心电压,计数器再减1,输出11111101;否则输出00000010。通过反复使用这种方法,逐步达到消除零点漂移的目的。

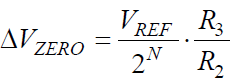

校正精度定义如下:

为了提高校正精度,我们需要提高D/A转换器的比特数,降低加法器的电压反馈增益。

如果将8位D/A转换器输出作为反馈输出,其最大输出范围为0.5 ~ 1.5 VREF,则检测信号增益为25,仪表放大器最大输出偏移量为1 V,则D/A转换器输出反馈增益应大于30.3。假设D/A变换器输出反馈增益为30.3,理论校正精度为215 mV。为了实现系统的增益和最佳的校正效果,需要对一次电路进行校正和放大,因此需要设计第二阶段的偏移校正电路。

第二阶偏置校正电路与第一阶电路拓扑相同,使用10位D/ a转换器和计数器。假设加法器的检测信号增益与第一阶输出偏移210 mV,则第二阶D/A转换器反馈增益应大于2.6。假设反馈增益为2.66,理论上的零偏移校正精度可以达到4.3 mV。

假设仪表放大器增益为2,工作电压为3.3 V,一级电路增益为25,二级电路增益为10,输入偏置为500 mV。压阻式微加速度计接口电路的瞬态仿真结果如下图所示。

可以看出,仪表放大器输出电压为0.65091 V,零偏移量为0.99909 V。通过第一阶段偏移校正电路,偏移量从500mv下降到143.5 mV。通过第二电路的偏移量减小1.9 mV,实现了传感器的零偏移校正。

仿真得到的校正精度与理论计算结果不完全一致。其原因是D/A转换器的微分非线性(DNL)。仿真结果的理论精度误差为0.370,小于DNL/LSB = 0.704,仿真结果满足设计要求。

主电路模块设计与仿真结果

1、运算放大器的设计与仿真

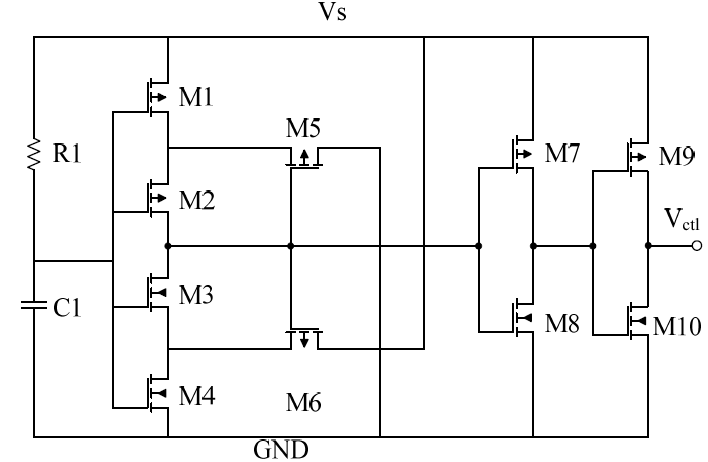

运算放大器在系统性能中起着重要的作用。由于电桥结构传感器的放大幅度较大,对放大器的噪声限制好、低偏置电压是理想的。为了保证系统的线性,运算放大器必须有足够高的增益。此外,还需要考虑集成系统的总功耗。带电容-乘法器频率补偿的三级运算放大器满足上述要求。它可以有效地避免典型的两级运算放大器的低直流增益和高功耗,带电容-乘法器频率补偿的三级运算放大器的原理图如下所示。

运算放大器的仿真结果表明,当负载电容是10 pF时,开环增益是120分贝,单位增益带宽为1.699 MHz,补偿电压是0.3 mV,回转率是1.625 V /μs。电源电压3.3 V,电流只有100μA。

2、启动控制逻辑单元的设计与仿真

电路在运行过程中逐渐接近系统零点,对零点偏移量进行校正。接近零后,输出波形以方波抖动作为计数器的最低频率,最大值与最大值为比较器偏置电压的两倍。为了降低系统的功耗,在完全完成逐次逼近后,关闭仅用于重置系统的比较器、计数器和D/A开关。启动控制逻辑器后,电容C1开始充电。当延迟结束时,电压电平反转。对施密特触发器进行防震处理后,输出控制级Vcrl。控制电平翻转后,电路触发锁存器锁存输出,切断计数器和比较器的电源,降低系统的功耗。

启动控制逻辑电路仿真结果如下。延迟时间可以通过调整R1、C1的s值来改变。由于输入偏移量无法确定,所以延时时间应大于一个完整的计数周期。第二阶段校正电路的延时时间应大于第一阶段校正电路控制逻辑电路的延时时间,但时间差应大于第二阶段校正电路的计算器完成一个完整计数周期的时间。

3、D/A开关的设计与仿真

D/A变换器不仅将双向计数器的结果转换为相应的电压输出,而且在锁存器关闭的对应计数器处保持电压恒定。由于电容式D/A变换器存在基片泄漏等因素,导致输出电压长期保持不变,需要使用电阻型或晶体管电流源来实现。与传统电阻型D/A变换器相比,采用锁存器的R-2R梯形电阻网络结构,节省了大量空间,易于实现。下图为具有R-2R梯形电阻网络结构的D/A变换器。

8位D/A转换器的仿真结果如下图所示。输出范围为0.8467~2.4752 V,对应最小比特数的电压变化为LSB = VREF/2N = 1.65/256 = 6.4453 mV,微分非线性为+DNL = 0.704 LSB, DNL = 0.252 LSB。DNL是D/A变换器中理想值与最大值之间的输出电平差,影响校正精度。

4、双向可逆计数器设计与仿真

同步可逆二进制计数器结构如图6所示。当控制信号X为1时,FF1FF8中的J和K分别与下触发器的Q端相连进行加法计数;当控制信号X为0时,FF1FF8中的J和K分别与下触发器的Q端相连进行减法计数,实现可逆计数功能。

下图显示了计数器输出从11111111更改为00000000。当计数器输入较低时,时钟频率为21.74 kHz。

5、比较器的设计与仿真

过零比较器电路如下图所示。比较器采用二级开环结构,采用推挽逆变器提高了摆频,但增加了输出延迟。

开环瞬态响应和100 pF负载电容比较器的幅频特性如图12 所示。比较器年代传播延迟是358 ns,转换速度是+ 3.6 V /μs和5.15 V /μs,补偿电压约为15μV,开环增益为88.793 dB,其准确性为:

-

一种单片集成高性能三轴MEMS加速度计2023-01-29 2734

-

2227-050加速度计模块2021-05-28 1158

-

振动环境下MEMS加速度计的可靠性评估2020-08-02 6746

-

浅谈Mems电容式加速度计的种类及结构2020-06-08 4156

-

MEMS加速度计的概念,MEMS加速度计的原理2020-06-01 5210

-

请问 ADXL355 加速度计是属于哪一类加速度计?2018-08-01 3980

-

关于一种带数模混合输出的加速度计系统的设计和验证2018-07-03 5537

-

USB微机电加速度计2017-07-10 3487

-

介观压阻效应在硅微加速度计中的应用2009-11-26 582

-

基于微加速度计的低功耗无线惯性鼠标的设计Design of2009-06-09 778

-

压阻加速度计的信号调整电路2009-04-20 951

全部0条评论

快来发表一下你的评论吧 !