双稳态触发器设计

电子说

1.4w人已加入

描述

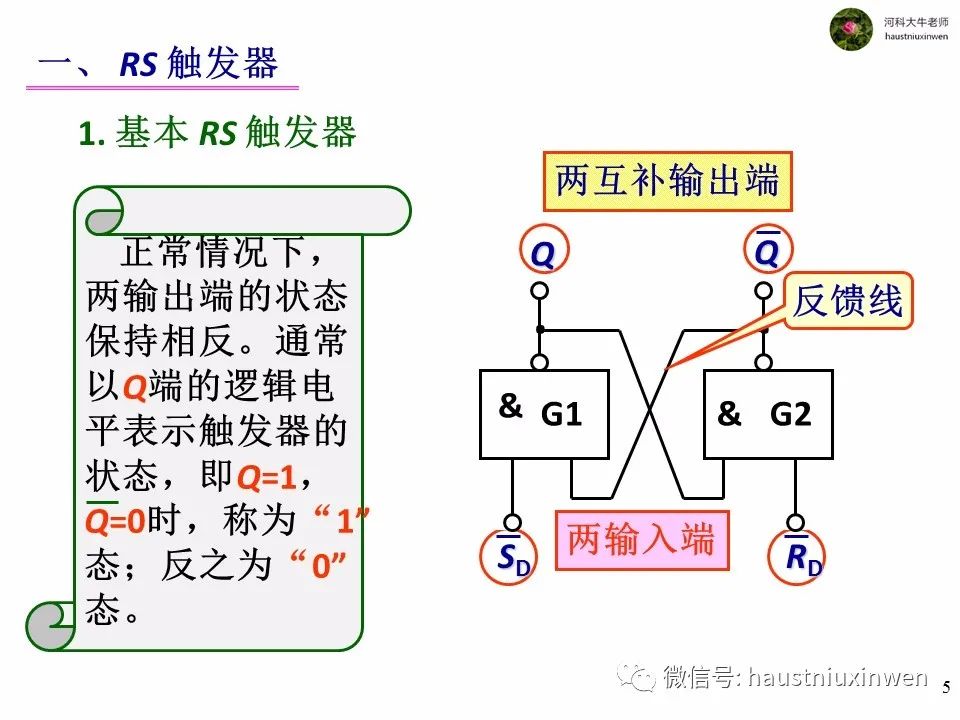

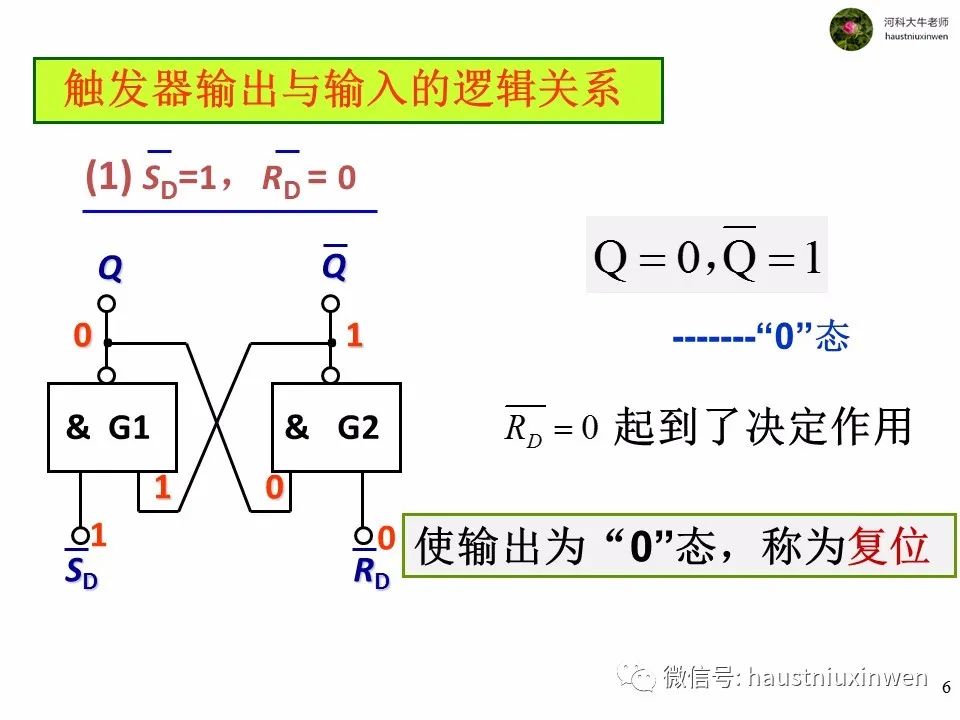

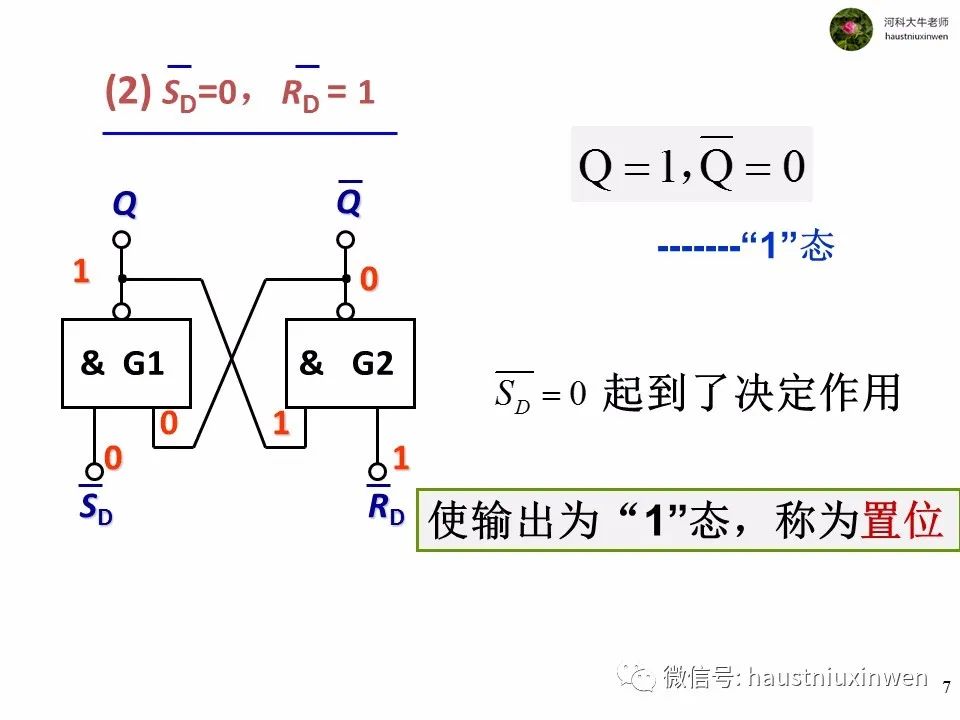

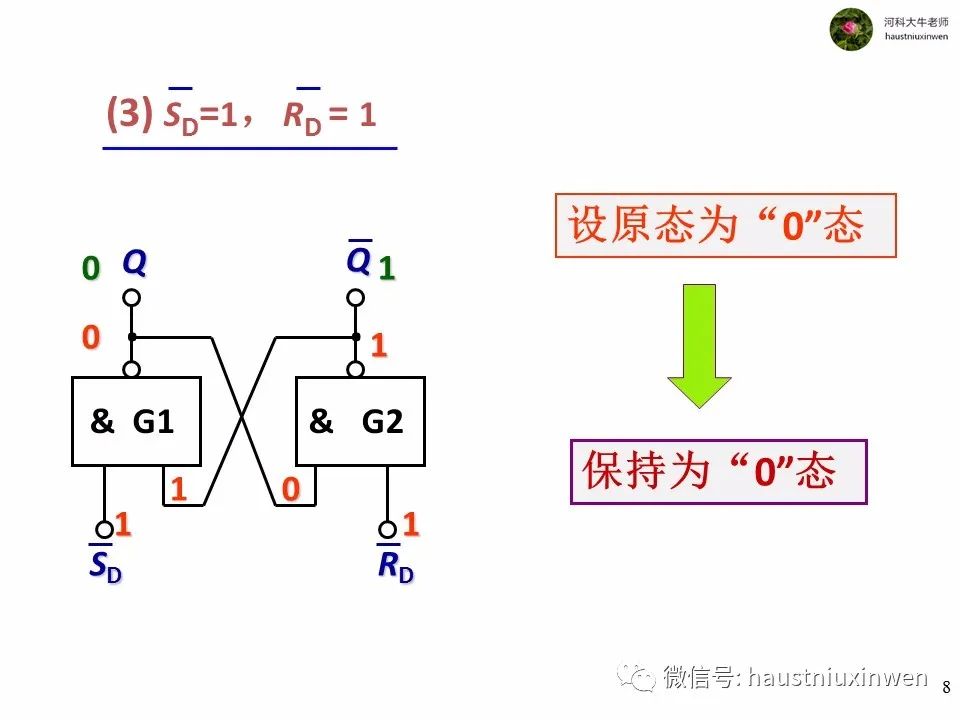

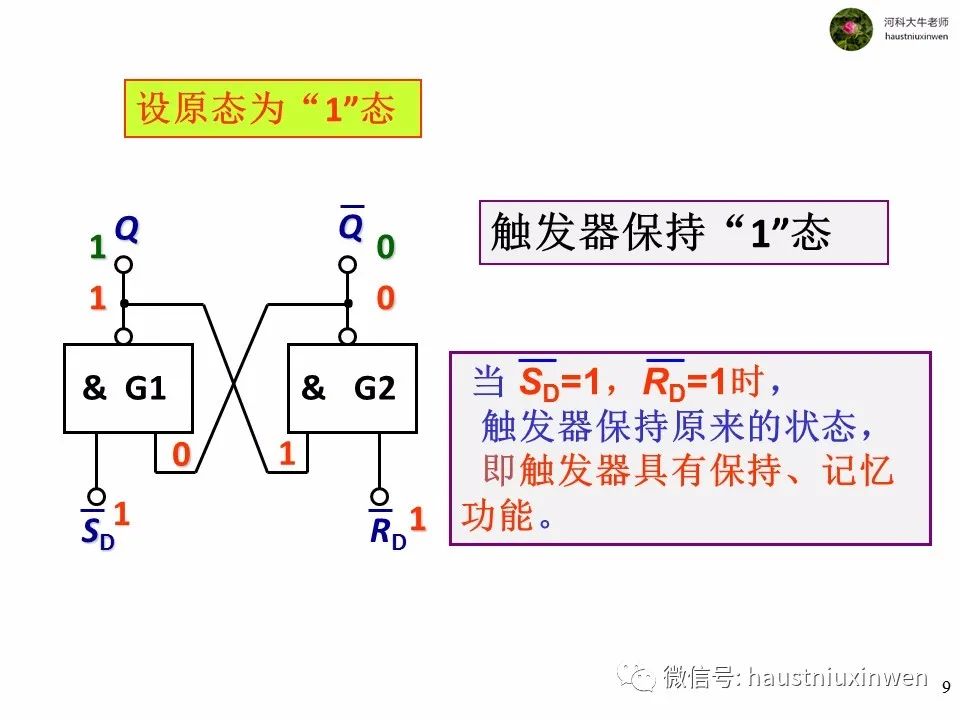

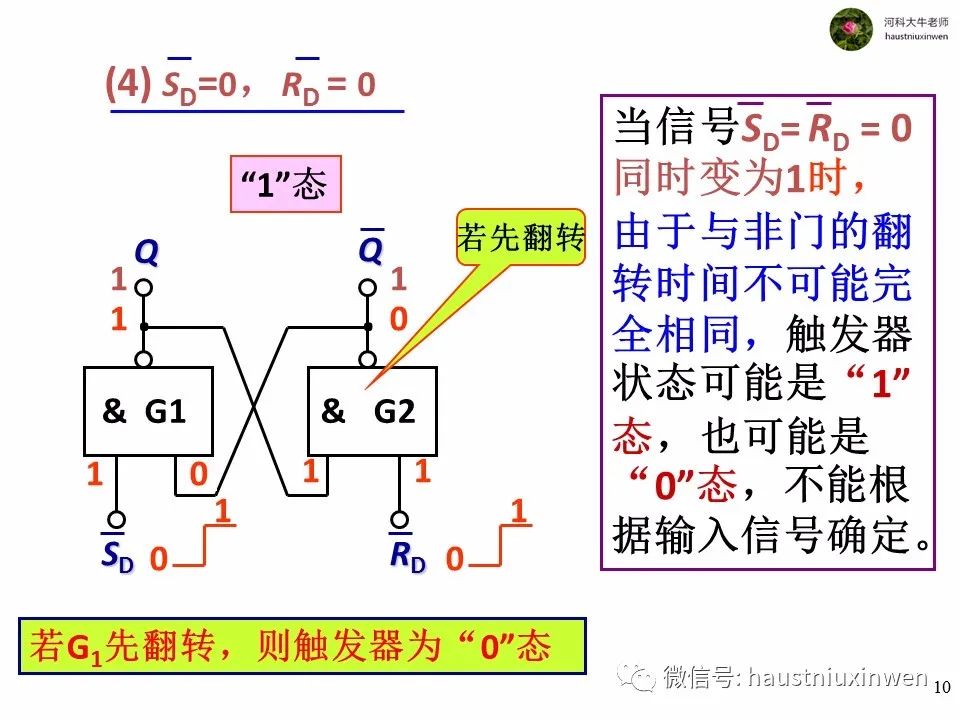

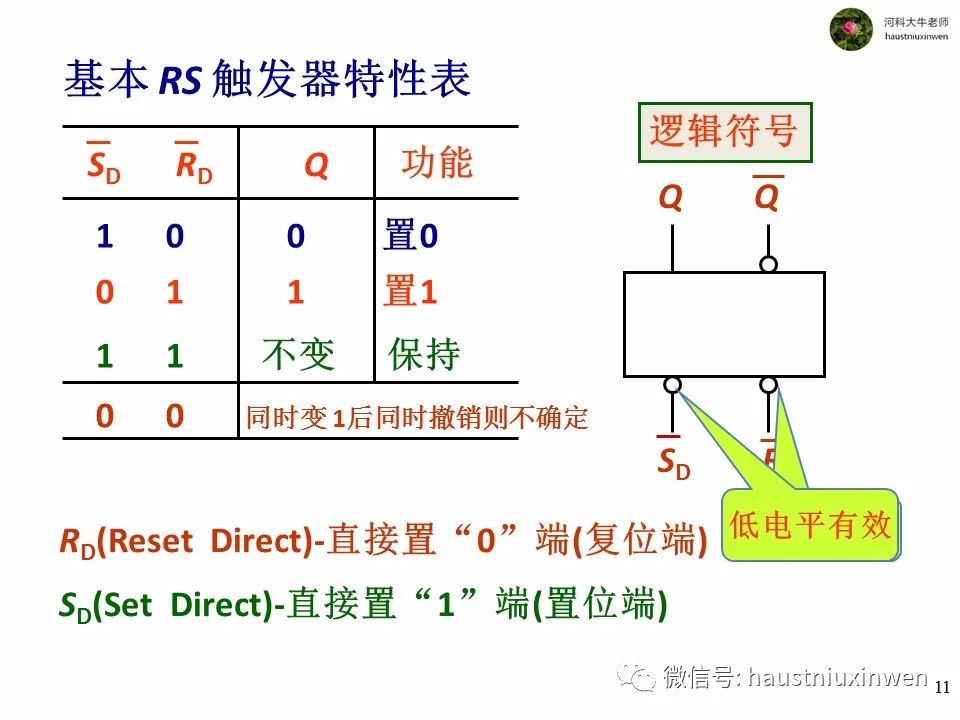

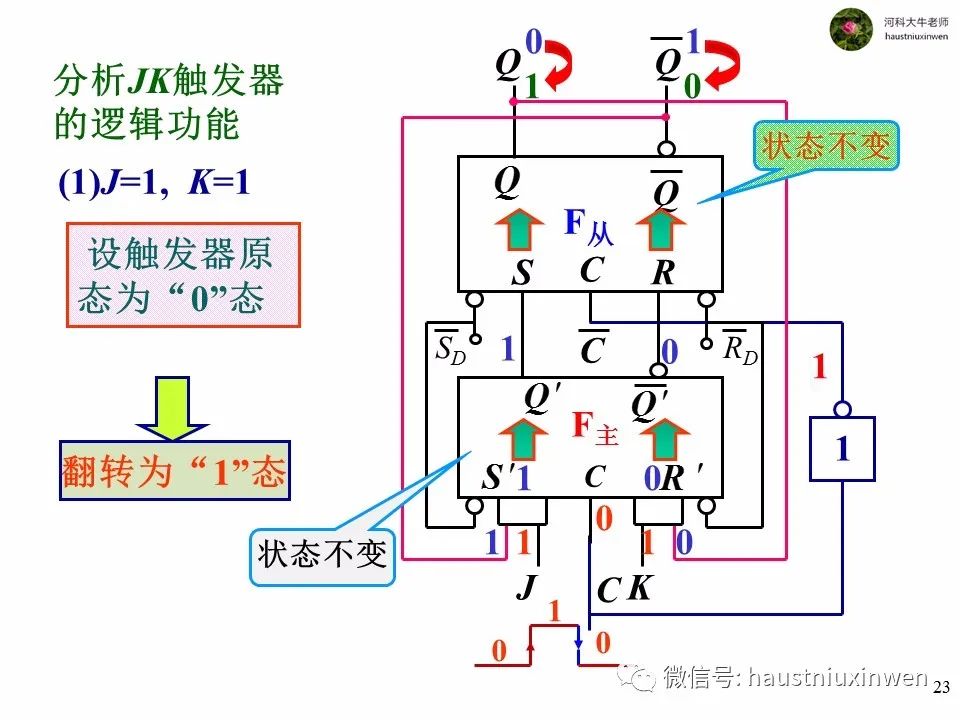

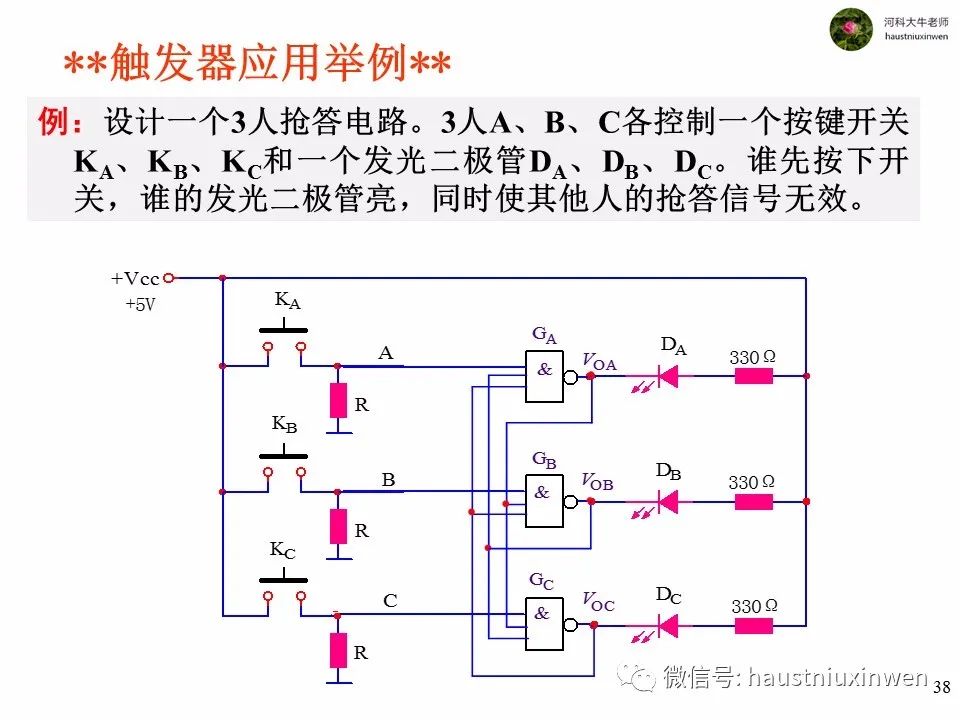

时序逻辑电路与组合逻辑电路的区别在于,时序逻辑电路的输出并不仅仅由输入条件决定,还由输出的前一个状态有关。也就是说,当输入改变时,不能唯一确定输出是什么,还要看输入改变前输出是什么状态,一起决定后面的输出状态。简而言之,这是一个有反馈的电路。

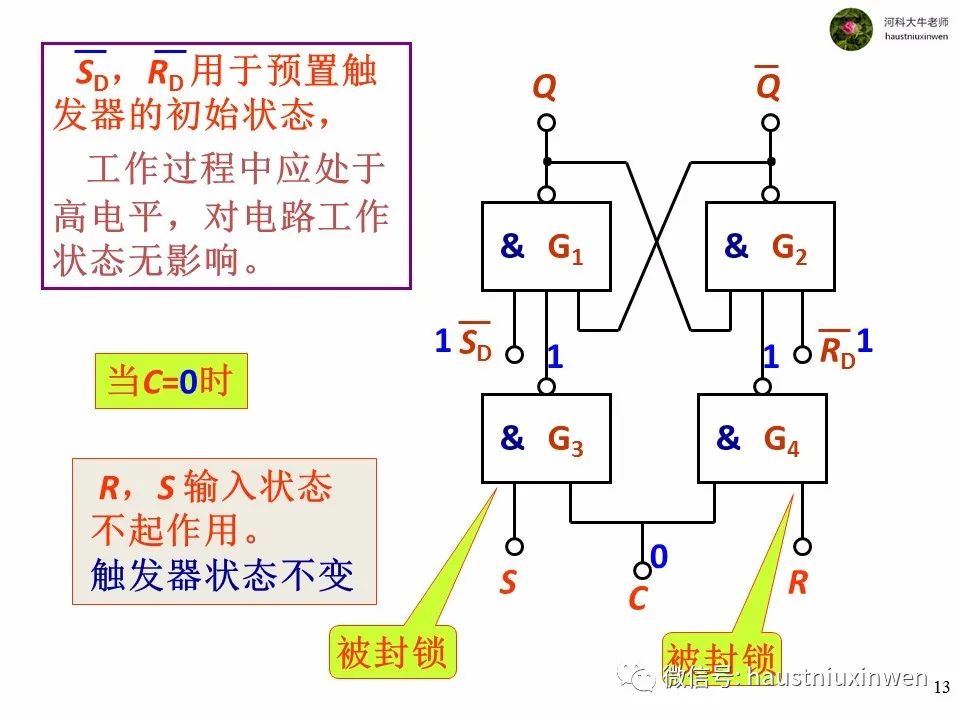

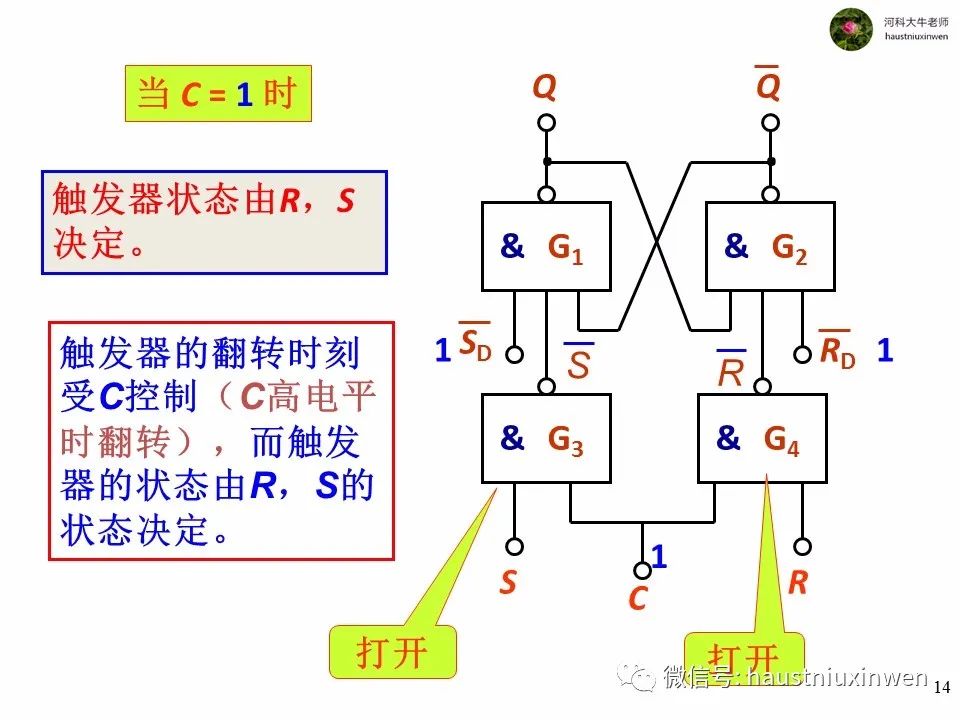

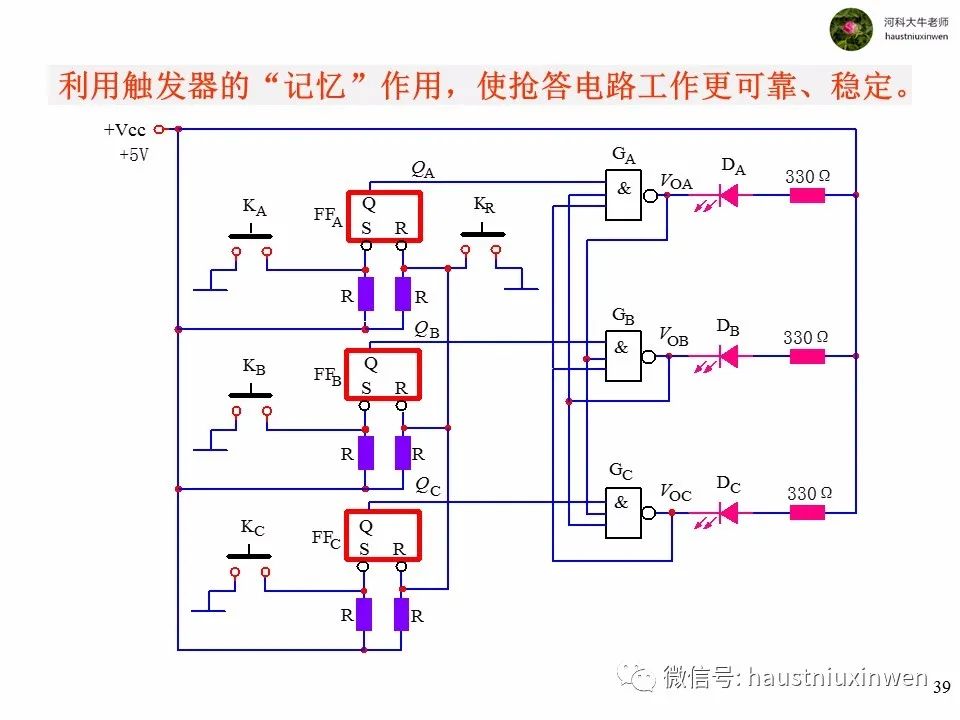

与模拟电路中的反馈不同的是,反馈不是随时随地进行的,而是有节奏的,当有效触发信号来临,才能进行控制输出的作用。触发信号不来,输入信号即便有变化,也不能改变输出。这种动作机制可以保证逻辑电路的多个输入信号动作完成后才去实现逻辑功能,即减少误动作,增加可靠性。

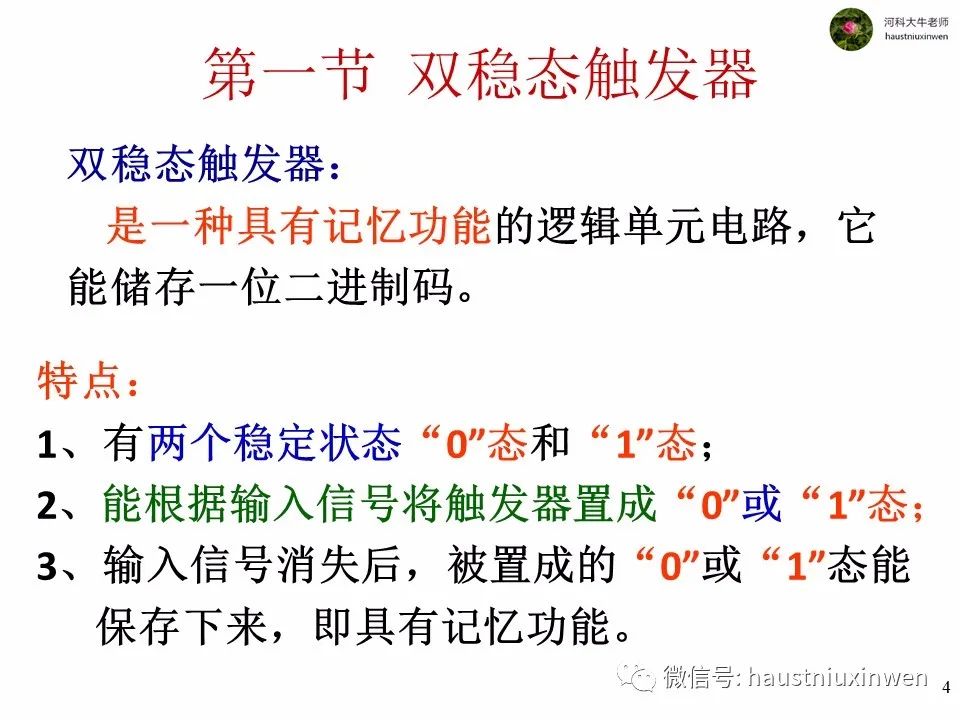

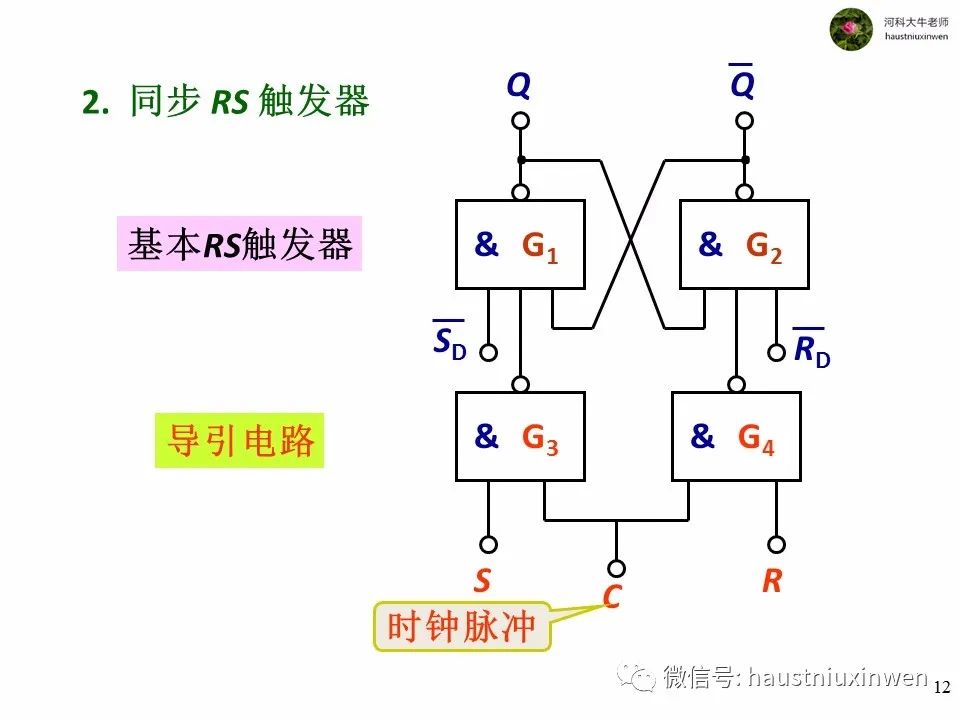

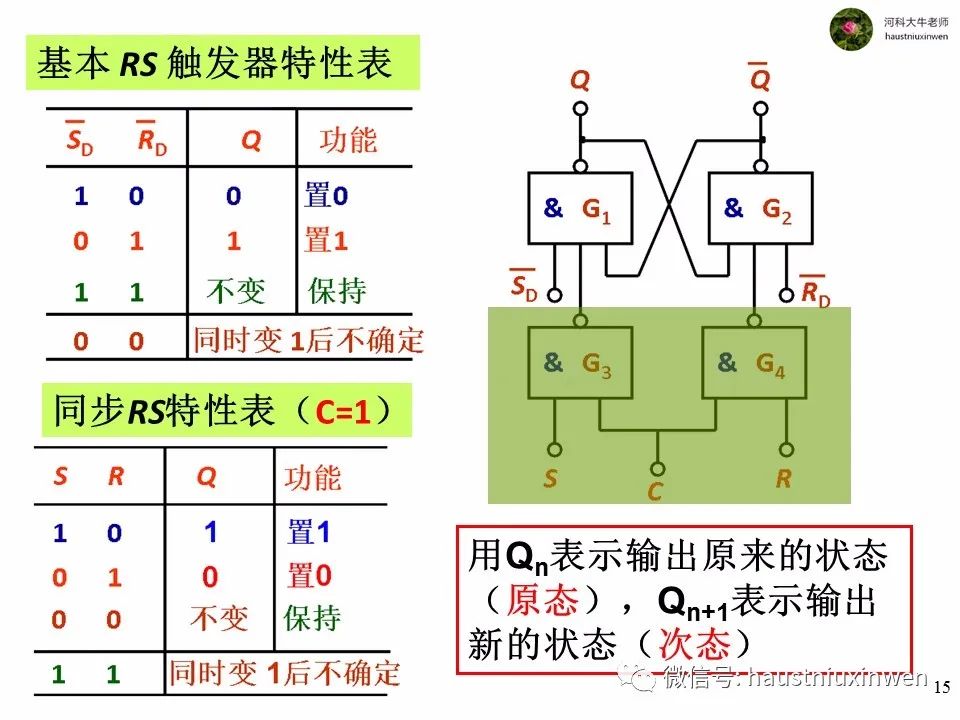

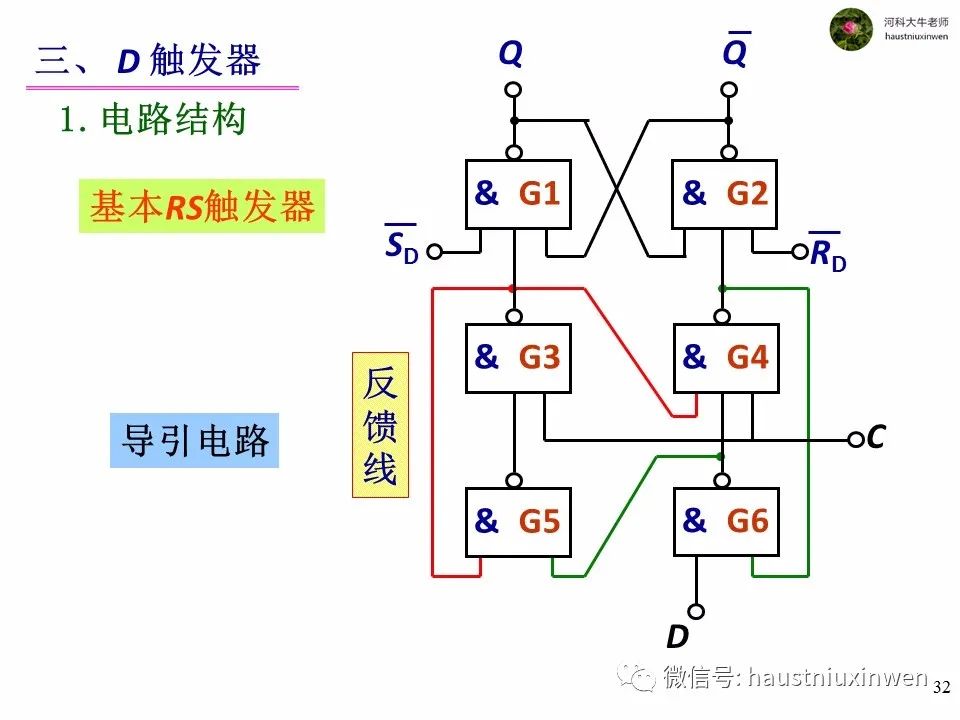

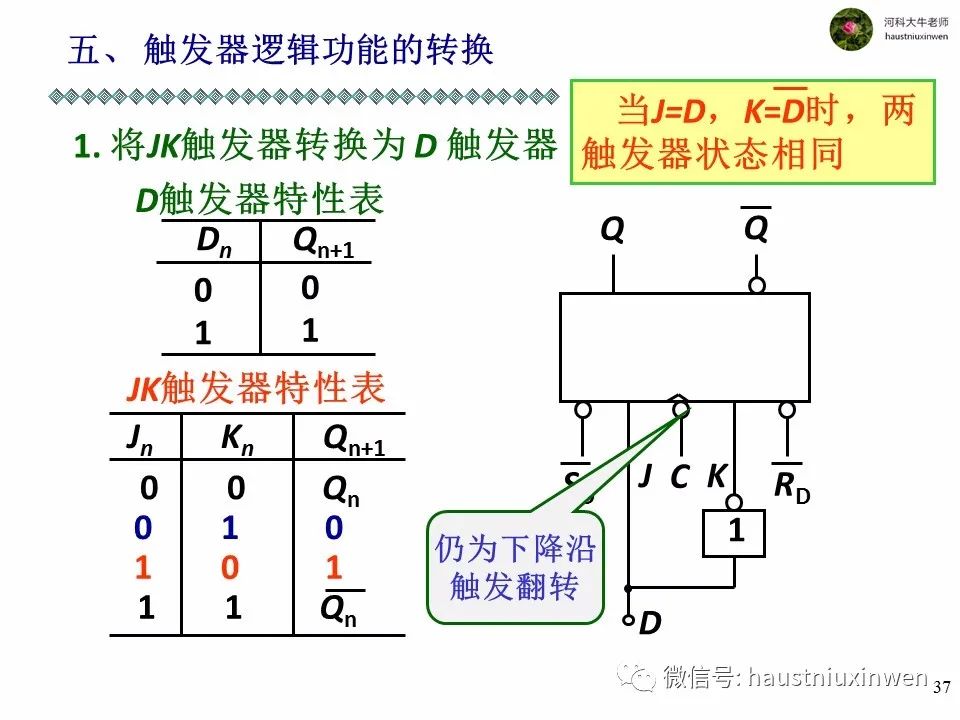

组合逻辑电路的基本单元是门电路,而时序逻辑电路的基础单元是双稳态触发器。

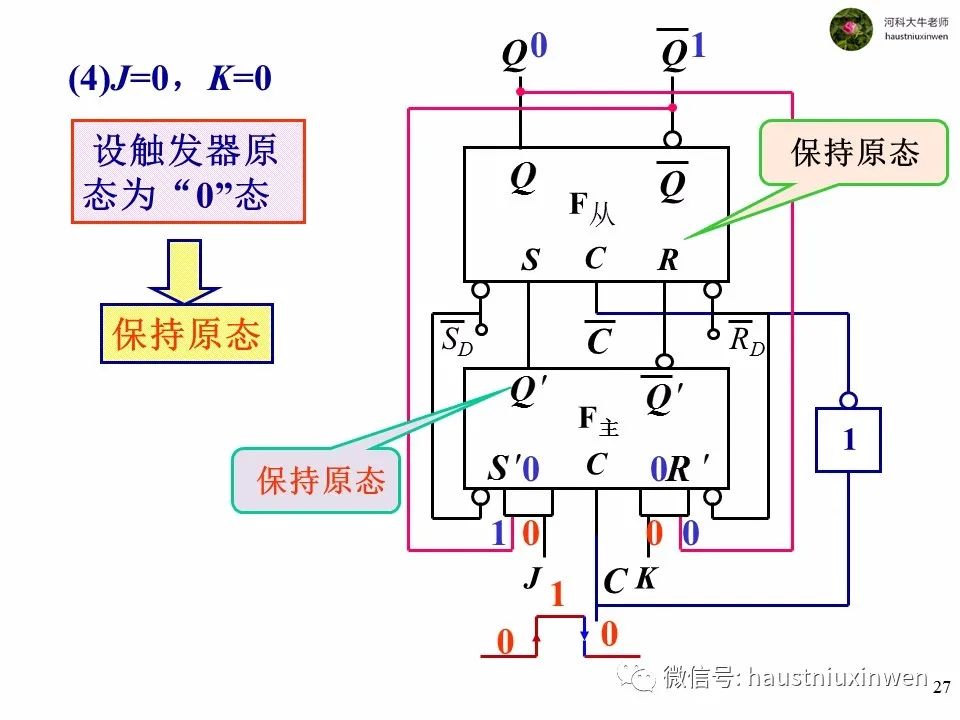

稳态是指在没有有效触发信号时,输出端的状态始终保持不变。

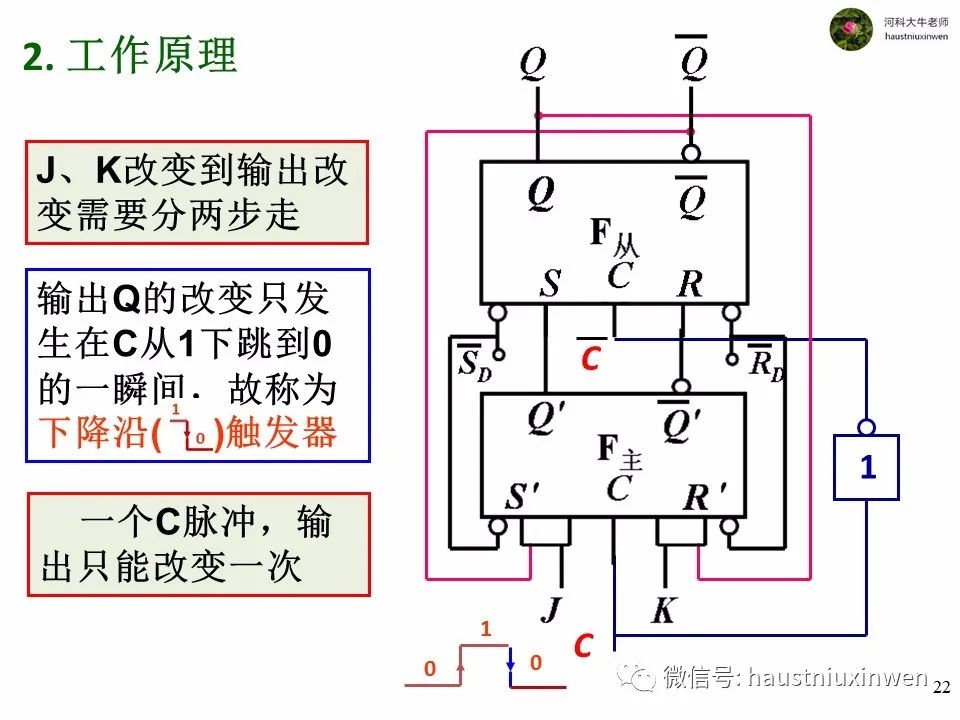

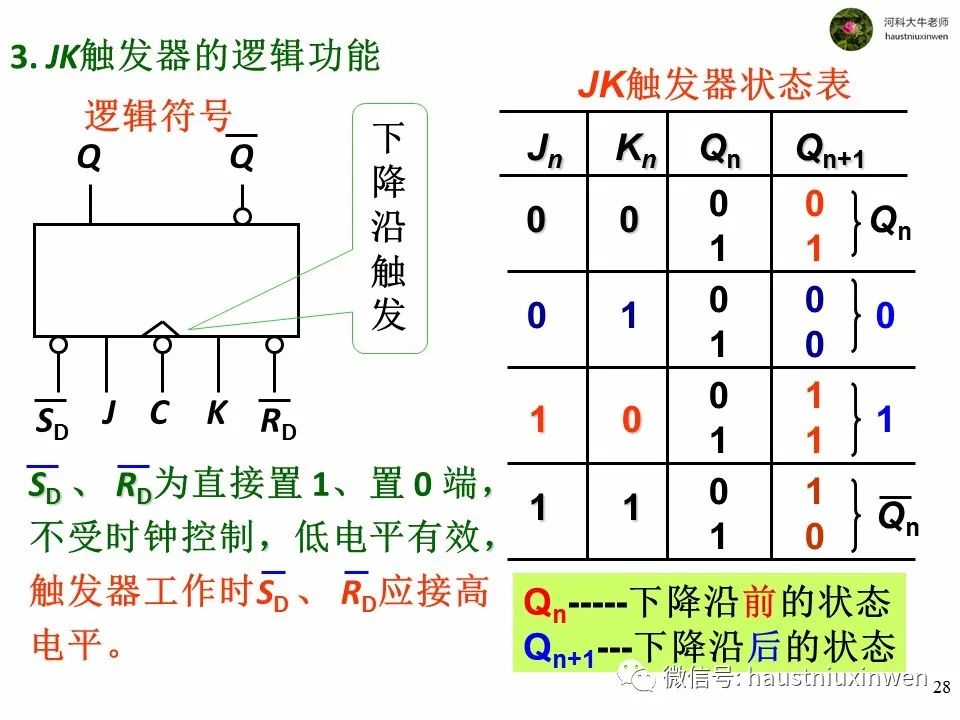

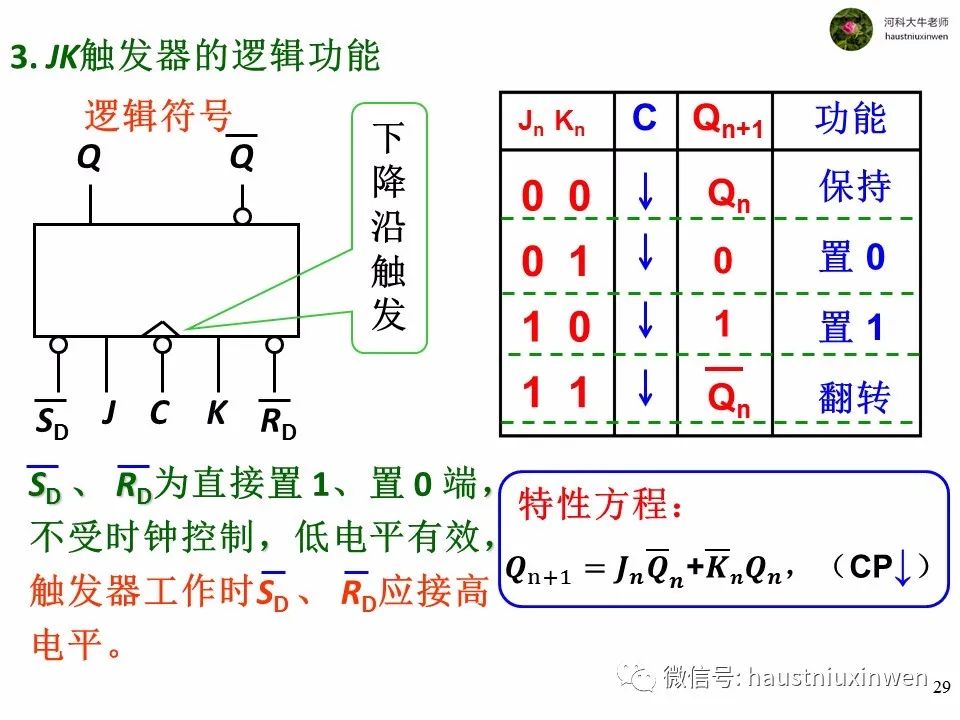

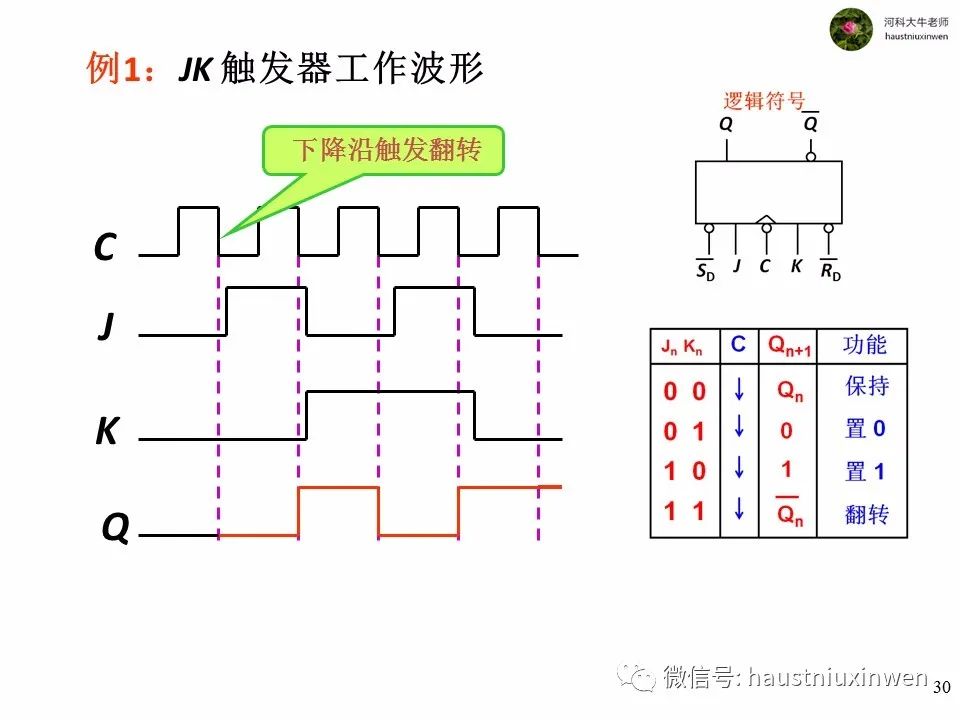

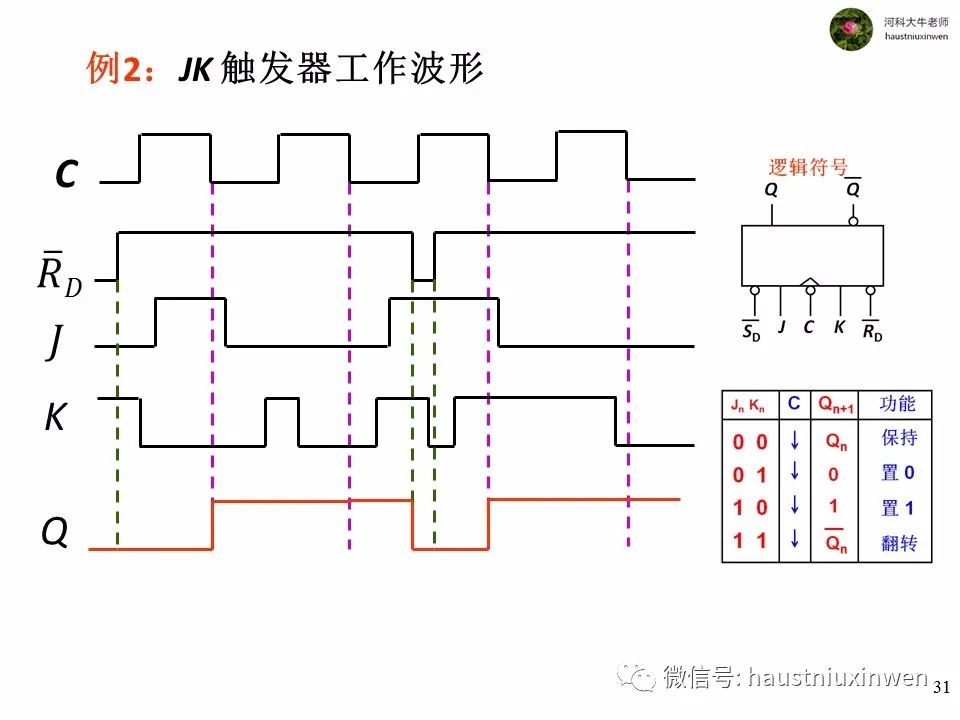

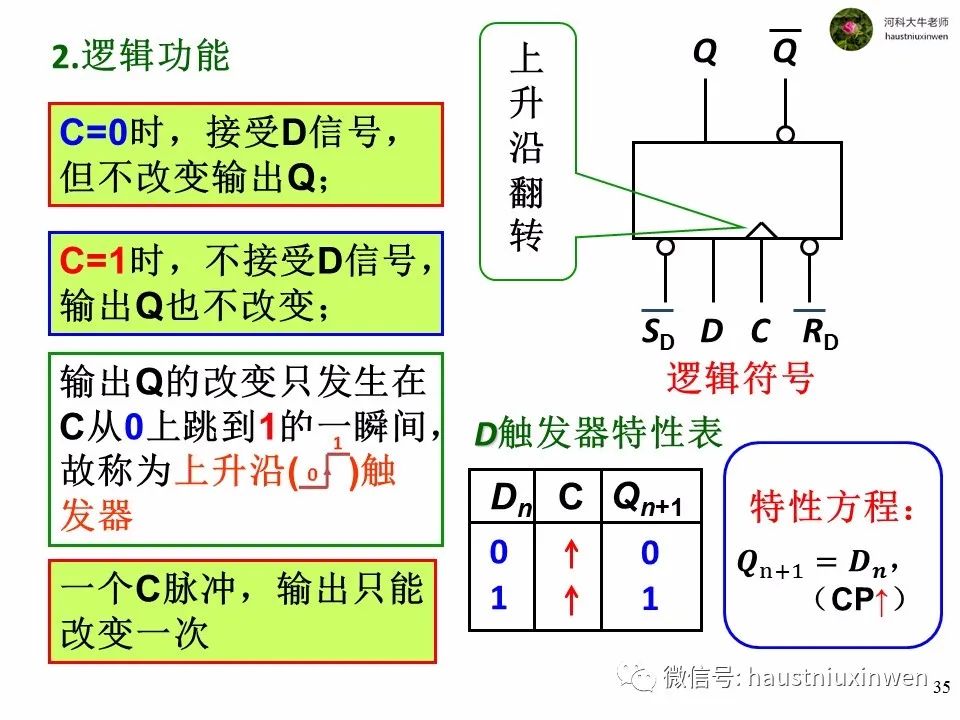

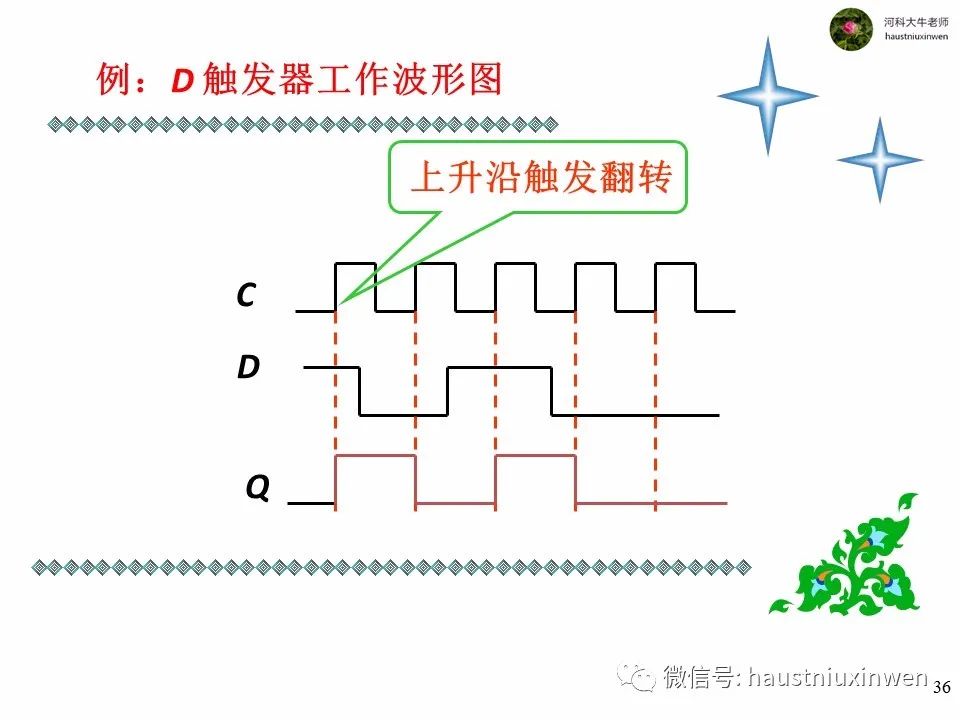

而触发信号有电平触发和边沿触发两种。

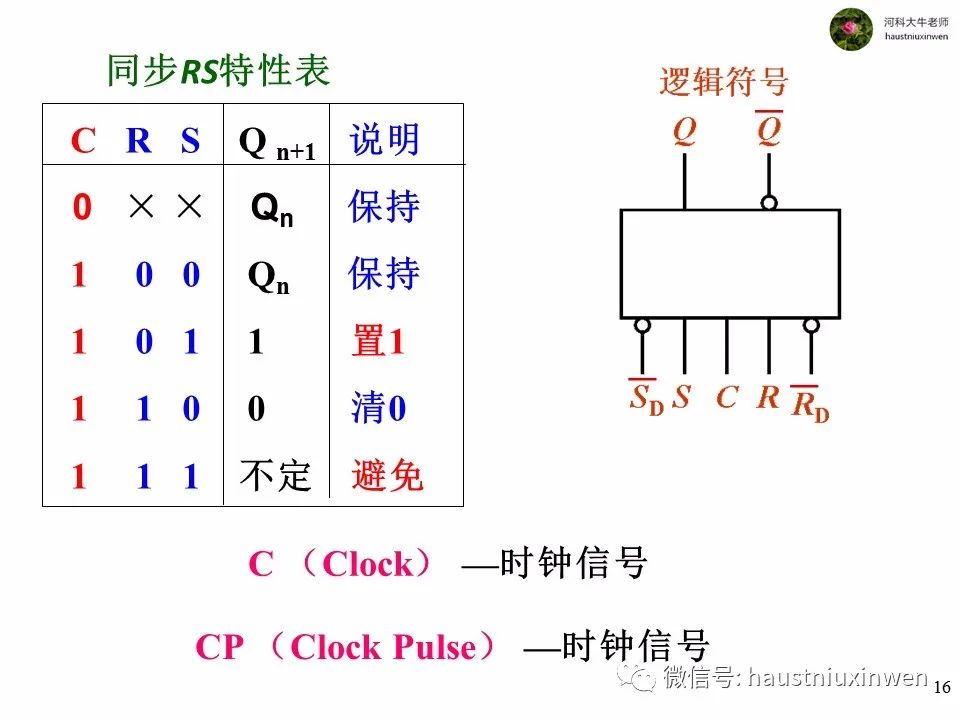

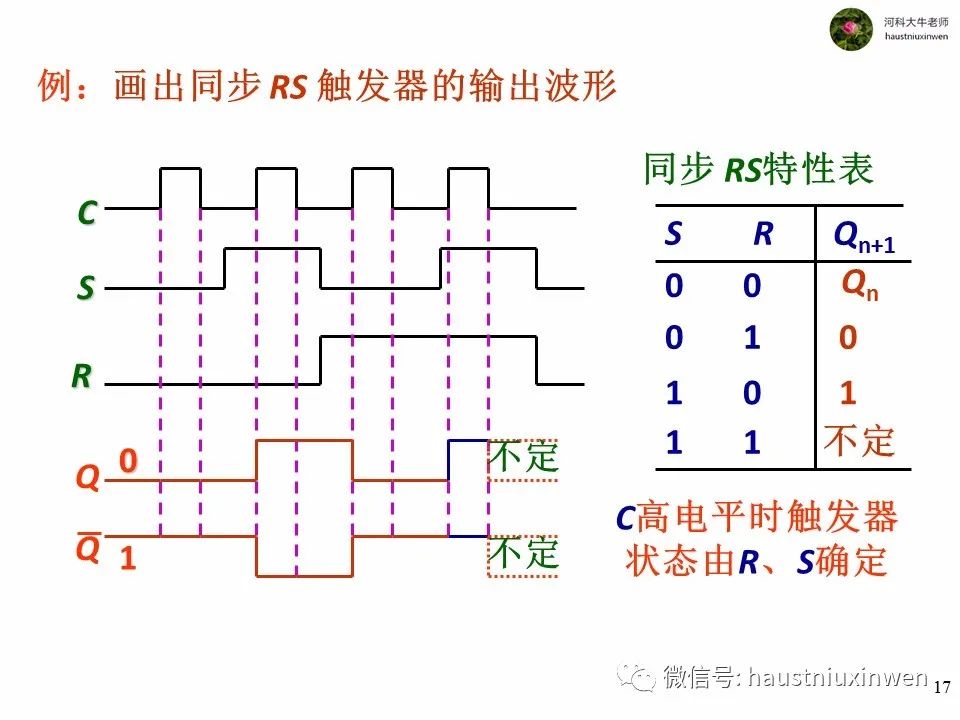

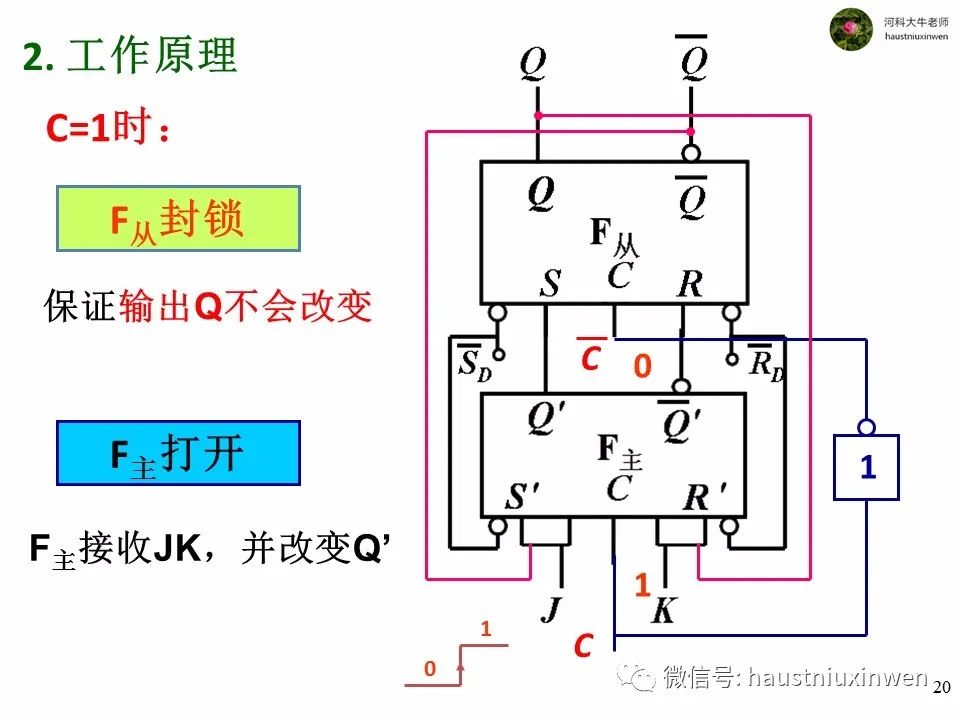

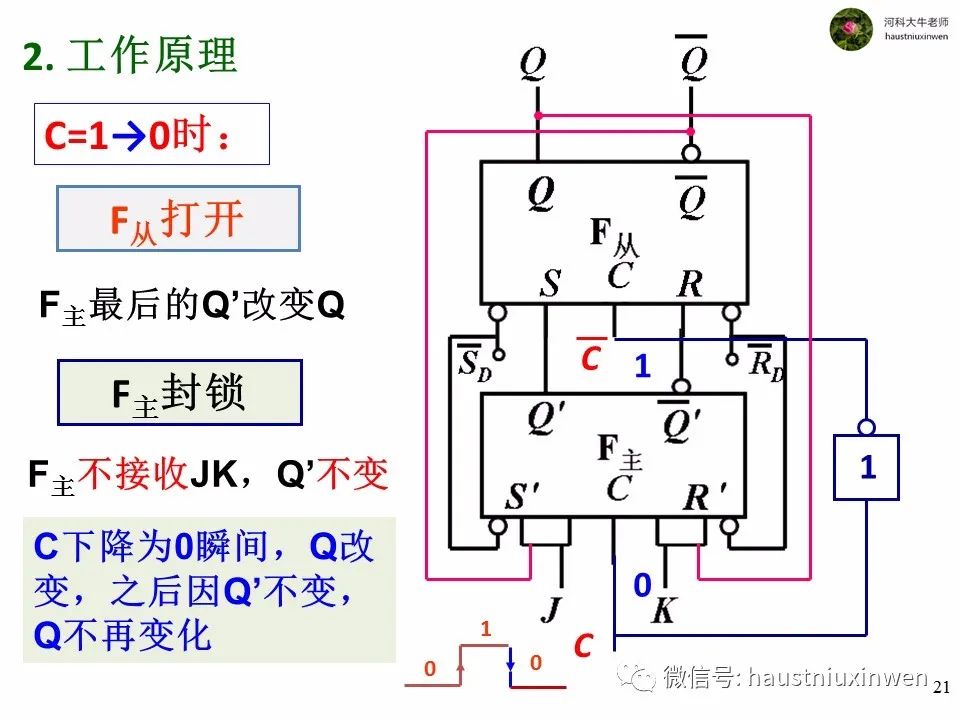

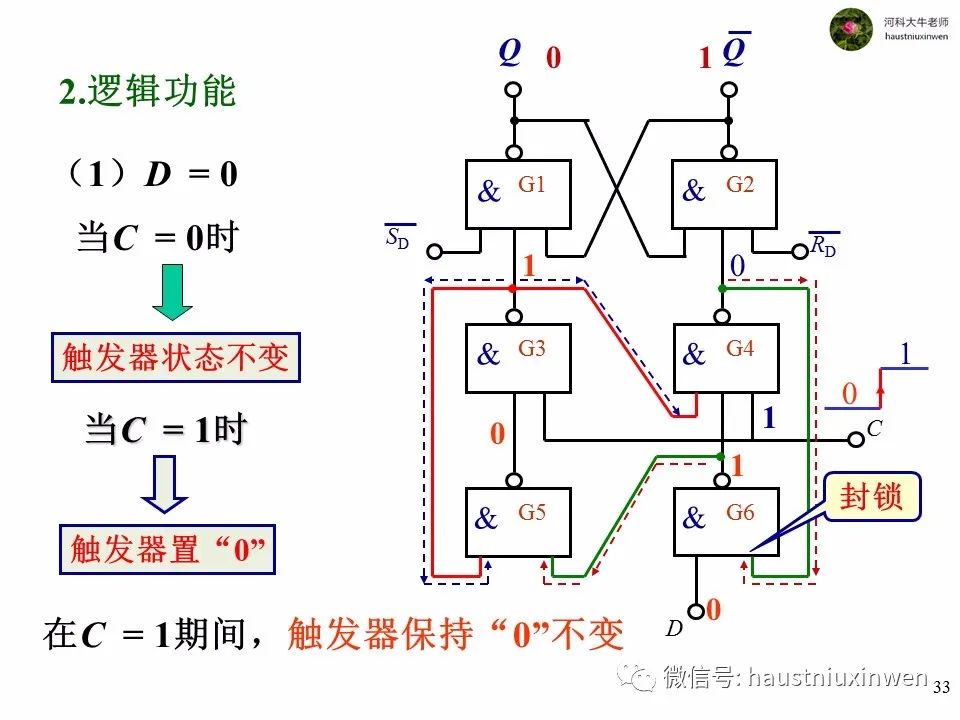

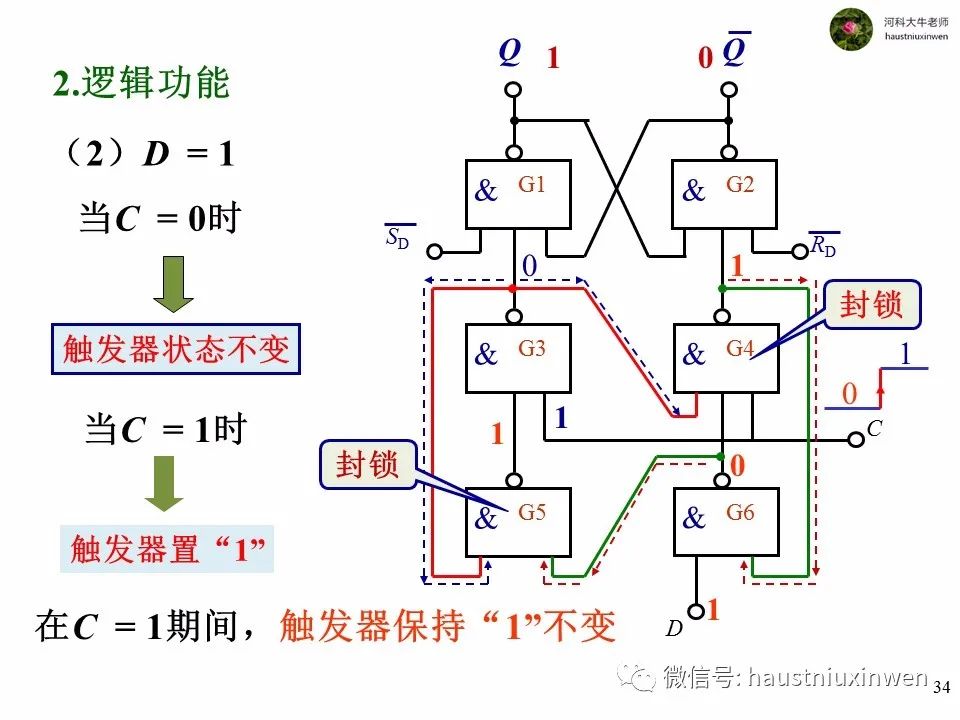

电平触发是指当时钟信号为高电平时,允许输出根据输入和原状态改变。边沿触发是指当时钟信号由0变1或者由1变0时,输出才能根据输入和原状态改变。

电平触发在需要多个信号都满足时才执行功能的情况下经常使用,以避免因多路信号反应时间不一致造成的误操作。

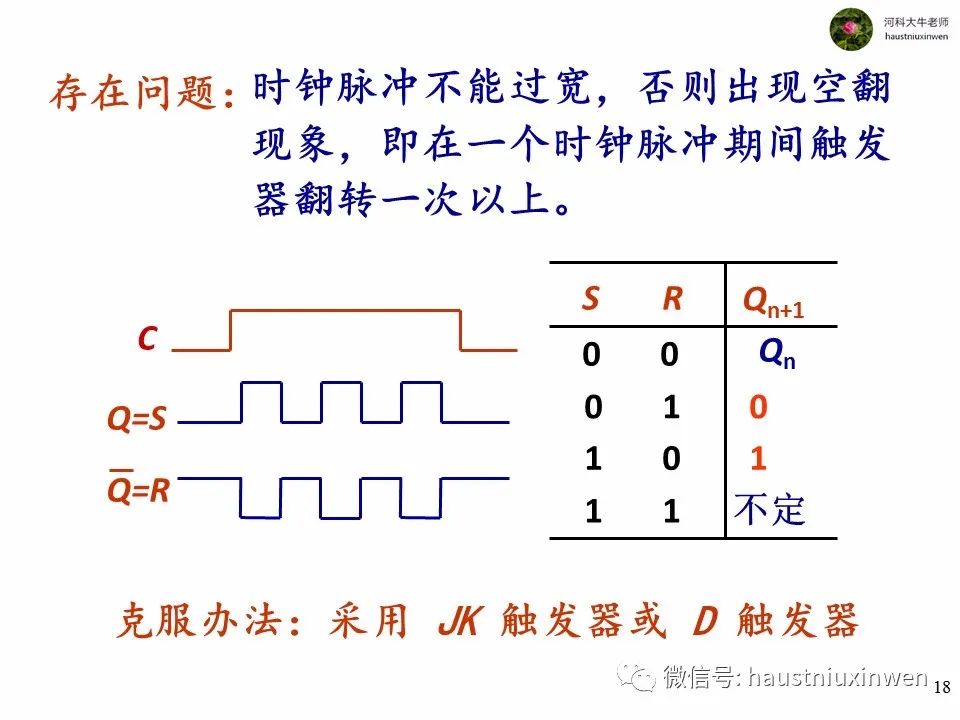

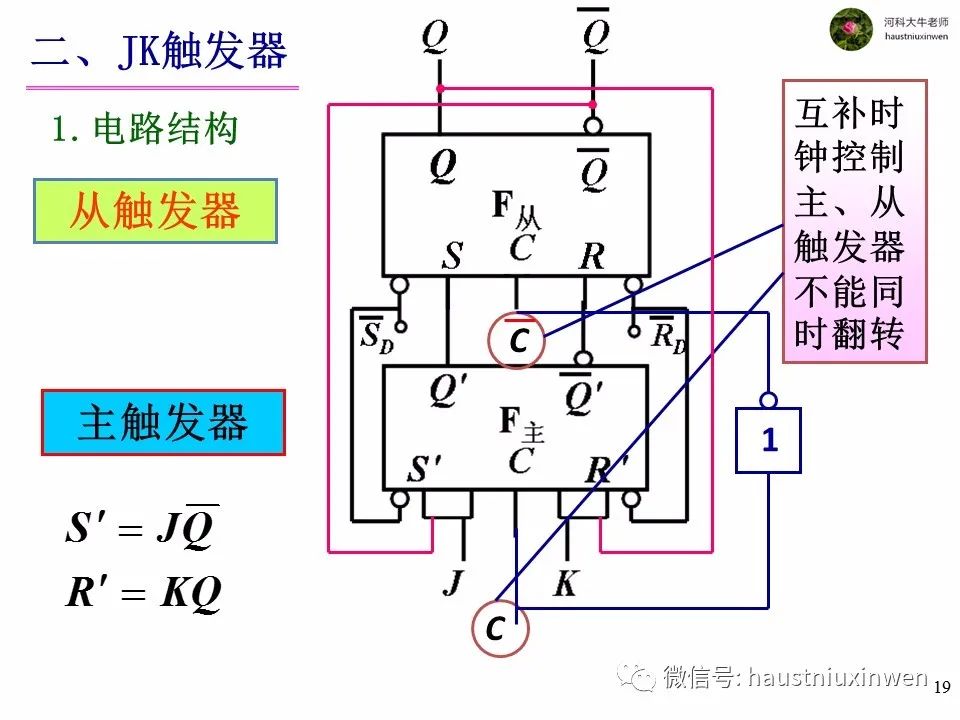

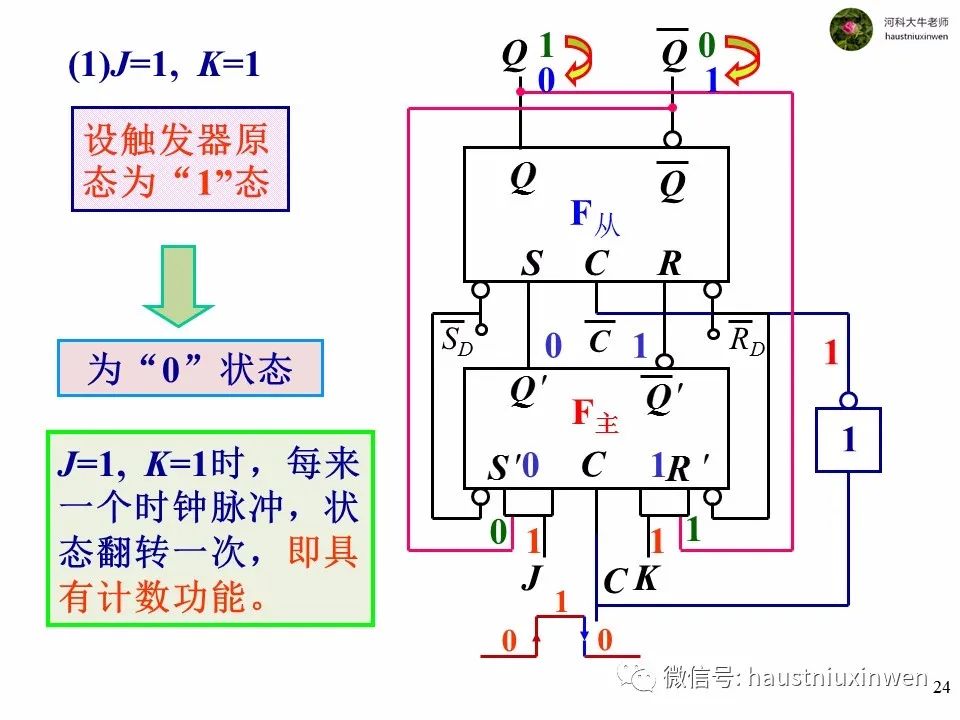

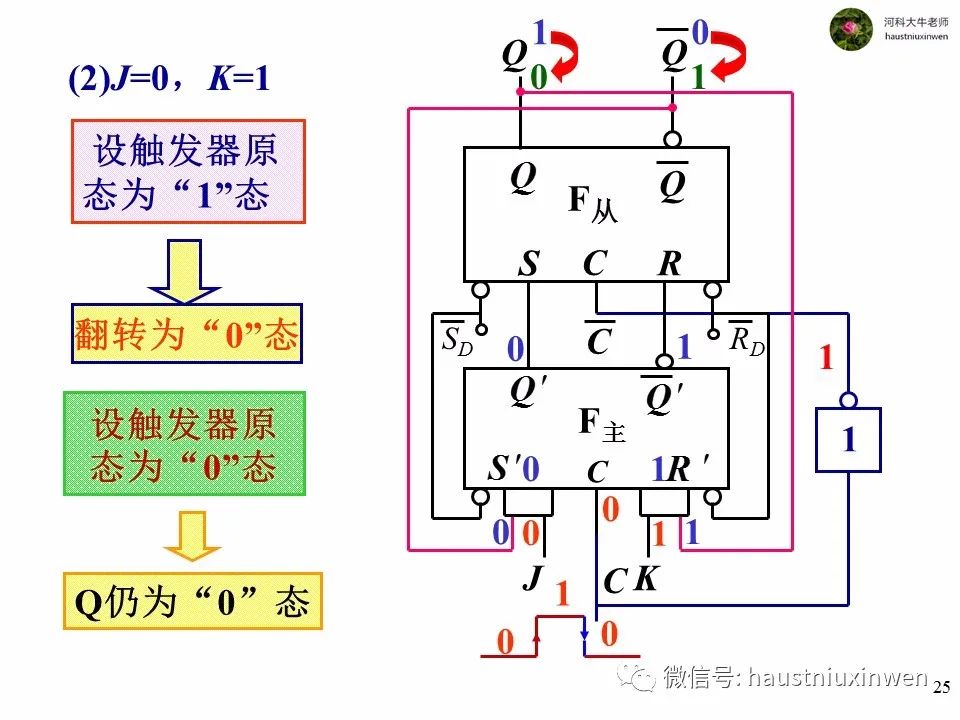

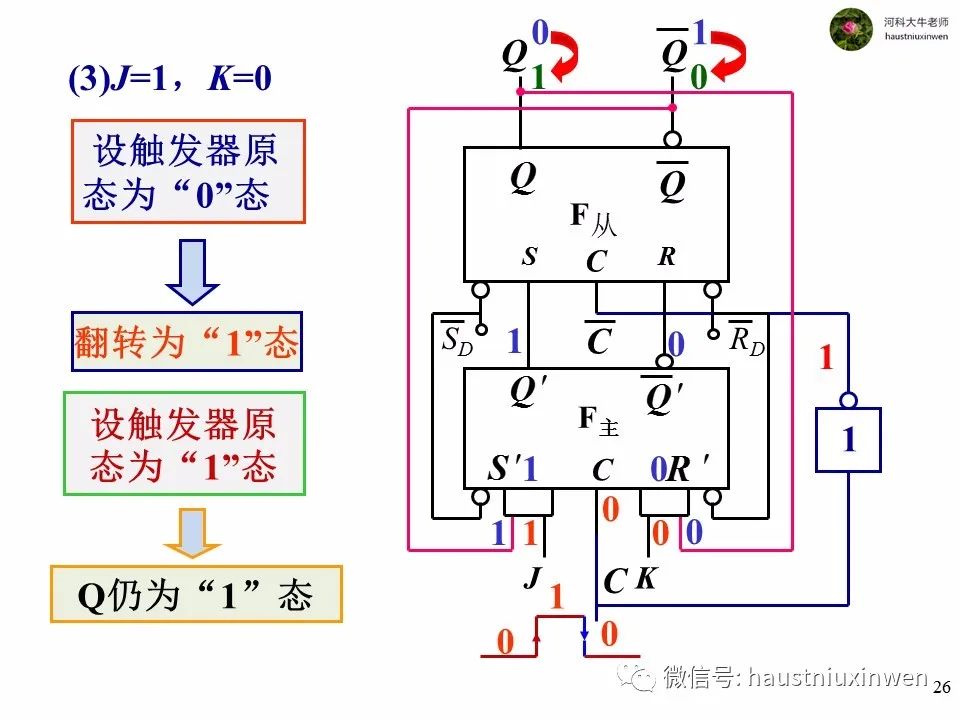

边沿触发可以实现一个触发脉冲信号触发器只动作一次的功能,避免空翻失控。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

双稳态触发器可分为什么类型2024-08-22 1752

-

双稳态触发器的基本特征是什么2024-08-11 1497

-

双稳态触发器的工作原理详解2018-04-04 104531

-

数字电路--触发器双稳态触发器2016-12-20 1207

-

双稳态触发器(按键触发多谐振荡器)2009-09-28 1800

全部0条评论

快来发表一下你的评论吧 !