为什要区分AGND和DGND?搞清楚模数、数模转换中的AGND和DGND

描述

1.为什要区分AGND和DGND?

目前的信号处理系统一般需要混合信号器件,例如模数转换器 (ADC)、数模转换器 (DAC)和快速数字信号处理器 (DSP)。由于需要处理宽动态范围的模拟信号,因此拥有高性能ADC 和 DAC 显得更加重要。在恶劣的数字环境内,能否保持宽动态范围和低噪声与采用良好的高速电路设计技术密切相关,包括适当的信号路由、去耦和接地。

过去,一般认为“高精度、低速”电路与所谓的“高速”电路有所不同。对于 ADC 和DAC,采样频率一般用作区分速度标准。不过,以下两个示例显示,实际操作中,目前大多数信号处理 IC 真正实现了“高速”,因此必须作为此类器件来对待,才能保持高性能。DSP、ADC 和 DAC 均是如此。

所有适合信号处理应用的采样 ADC(内置采样保持电路的 ADC)均采用具有快速上升和下降时间(一般为数纳秒)的高速时钟工作,即使吞吐量看似较低也必须视为高速器件。例如,中速 12 位逐次逼近型 (SAR) ADC 可采用 10 MHz 内部时钟工作,而采样速率仅为500 kSPS。

Σ-Δ 型 ADC 具有高过采样比,因此还需要高速时钟。即使是高分辨率、所谓的“低频”Σ-Δ工业测量 ADC(吞吐速率 10 Hz 至 7.5 kHz)也采用 5 MHz 或更高时钟工作,并且提供高达 24 位的分辨率(例如 ADI 公司的 AD77xx 系列)。

更复杂的是,混合信号 IC 具有模拟和数字两种端口,因此如何使用适当的接地技术就更加茫然。此外,某些混合信号 IC 具有相对较低的数字电流,而另一些具有高数字电流。许多情况下,两种类型必须区分对待,才能实现最佳接地。

数字和模拟设计工程师倾向于从不同角度考察混合信号器件,本教程旨在确立适用于大多数混合信号器件的一般接地原则,而不必了解内部电路的具体细节。

2.接地层电源层

保持低阻抗大面积接地层对目前所有的模拟和数字电路都很重要。接地层不仅用作去耦高频电流(源于快速数字逻辑)的低阻抗返回路径,还能将 EMI/RFI 辐射降至最低。由于接地层的屏蔽作用,电路受外部 EMI/RFI 的影响也会降低。

接地层还允许使用传输线路技术(微带线或带状线)传输高速数字或模拟信号,此类技术需要可控阻抗。

由于“母线 (buss wire)”在大多数逻辑转换等效频率下具有阻抗,将其用作“地”完全不能接受。例如,#22 标准导线具有约 20 nH/ 英寸的电感。由逻辑信号产生的压摆率为 10mA/ns 的瞬态电流,在此频率下流经 1 英寸该导线将形成 200 mV 的无用压降 :

对于具有 2 V 峰峰值范围的信号,此压降会转化为约 10% 的误差(大约 3.5 位精度)。即使在全数字电路中,该误差也会大幅降低逻辑噪声裕量。

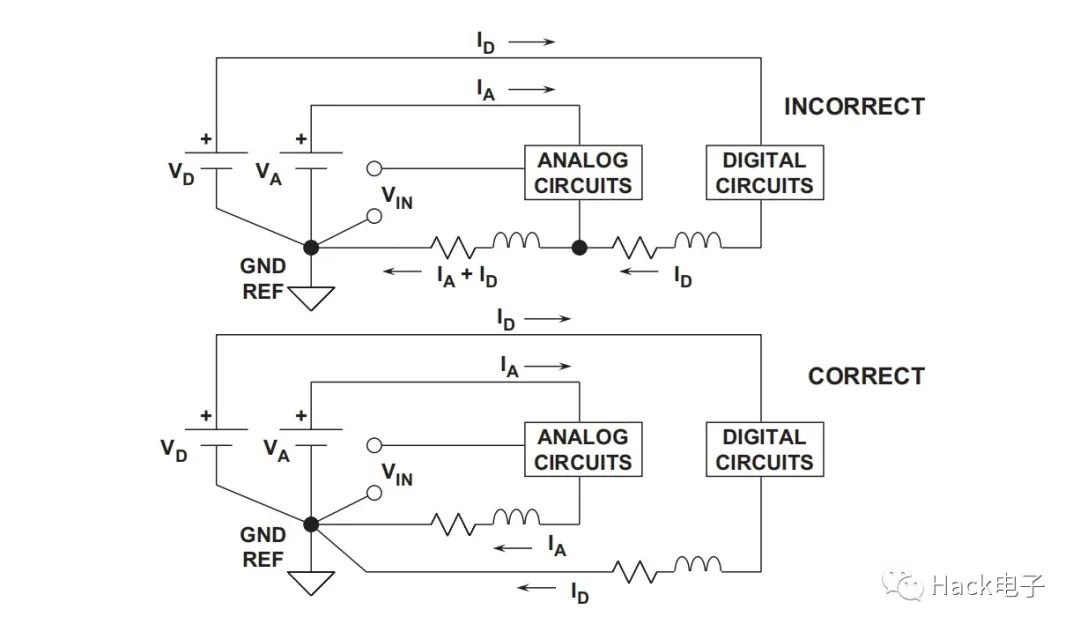

图 1 为数字返回电流调制模拟返回电流的典型情况(顶图)。接地返回导线电感和电阻由模拟和数字电路共享,这会造成相互影响,最终产生误差。一个可能的解决方案是让数字返回电流路径直接流向 GND REF,如底图所示。这就是“星型”或单点接地系统的基本概念。在包含多个高频返回路径的系统中很难实现真正的单点接地,因为各返回电流导线的物理长度将引入寄生电阻和电感,所以获得低阻抗高频接地就很困难。实际操作中,电流回路必须由大面积接地层组成,以便实现高频电流下的低阻抗。如果无低阻抗接地层,则几乎不可能避免上述共享阻抗,特别是在高频下。

图 1 :流入模拟返回路径的数字电流产生误差电压

所有集成电路接地引脚应直接焊接到低阻抗接地层,从而将串联电感和电阻降至最低。对于高速器件,不推荐使用传统 IC 插槽。即使是“小尺寸”插槽,额外电感和电容也可能引入无用的共享路径,从而破坏器件性能。如果插槽必须配合 DIP 封装使用,例如在制作原型时,个别“引脚插槽”或“笼式插座”是可以接受的。以上引脚插槽提供封盖和无封盖两种版本(AMP 产品型号 5-330808-3 和 5-330808-6)。由于使用弹簧加载金触点,确保了 IC 引脚具有良好的电气和机械连接。不过,反复插拔可能降低其性能。

3.低频和高频去耦

每个电源在进入 PC 板时,应通过高质量电解电容去耦至低阻抗接地层。这样可以将电源线路上的低频噪声降至最低。在每个独立的模拟级,各 IC 封装电源引脚需要更局部、仅针对高频的滤波。

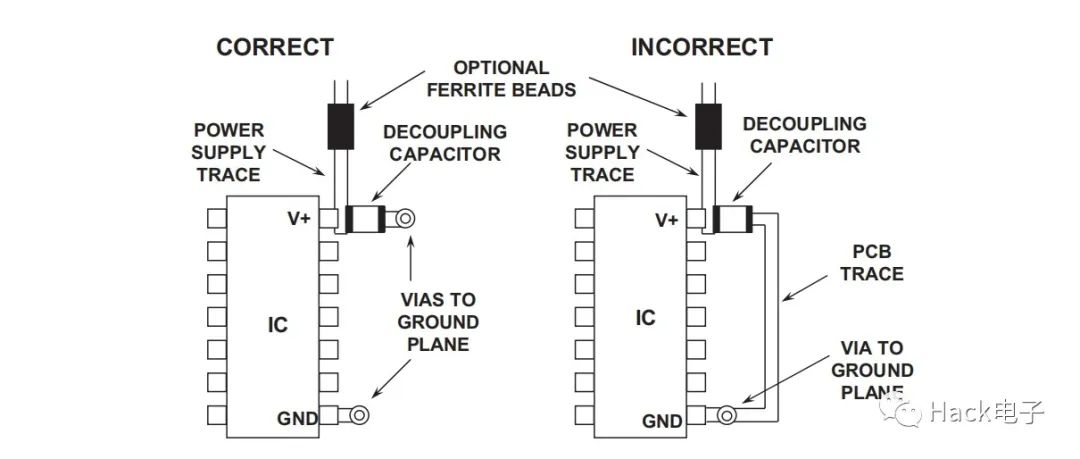

图 2 显示了此技术,图示左侧为正确实施方案,右侧为错误实施方案。左侧示例中,典型的 0.1 μF 芯片陶瓷电容借助过孔直接连接到 PCB 背面的接地层,并通过第二个过孔连接到 IC 的 GND 引脚上。相比之下,右侧的设置不太理想,给去耦电容的接地路径增加了额外的 PCB 走线电感,使有效性降低。

图 2 :局部高频电源滤波器通过较短的低电感路径(接地层)提供最佳滤波和去耦

所有高频(即≥ 10 MHz)IC 应使用类似于图 2 的旁路方案实现最佳性能。铁氧体磁珠并非 100% 必要,但会增强高频噪声隔离和去耦,通常较为有利。这里可能需要验证磁珠永远不会在 IC 处理高电流时饱和。

请注意,对于一些铁氧体,即使在完全饱和前,部分磁珠也可能变成非线性,所以如果需要功率级在低失真输出下工作,应检查这一点。

审核编辑:刘清

-

一文详解模数、数模转换器中的AGND和DGND2023-10-19 7050

-

ADC的AGND和DGND是一个地吗?2023-12-22 644

-

AD5348 DGND和AGND在芯片内部是连接的吗?2023-12-25 1255

-

VS1053的引脚AGND和DGND可以直接连接吗?2024-04-23 437

-

AD5560输入电源的GND为DGND,系统需要很高的精度,这种情况下AGND需要怎么做才好?2024-05-30 1879

-

AD9814如何与AGND和DGND连接?分别单点接地吗?2024-12-05 521

-

请问ADS8689 AGND和DGND如何进行处理?2024-12-26 490

-

AD模数转换器敷铜是AGND和DGND分开敷,还是只需要在顶层和底层敷AGND?2024-12-27 671

-

ADC的DGND与控制器的DGND是什么关系?2025-01-24 502

-

请问AD5348的DGND和AGND两个引脚在芯片内部是连接的吗2018-11-29 4045

-

请问VS1053的引脚AGND和DGND可以直接连接吗2019-02-20 3397

-

请问ADC的AGND和DGND是一个地吗?2019-06-12 1985

-

AGND和DGND引脚在100lqfp封装中为什么无法区分2020-04-01 1179

-

模拟开关,如CD4051,4052和4053,此处的地是用AGND好还是DGND好?2023-12-12 639

-

实现数据转换器的接地并揭开AGND和DGND的谜团2017-10-18 1067

全部0条评论

快来发表一下你的评论吧 !