ESD电流路径的分析

描述

好像任何一个行业的EMC都离不开ESD测试, ESD问题排查中,最重要最难的无疑是静电路径问题了。 本次就和大伙稍微探讨下ESD电流路径的分析,哪怕在为大家排查静电问题的时候提供一丝丝有益的思路,我就觉得没有白写。

静电波形

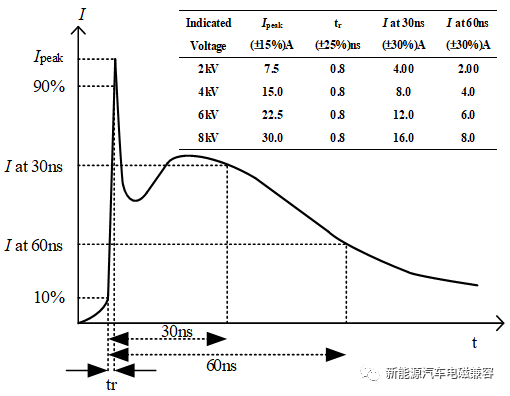

在试验室,通常使用电容加电阻的方式来模拟人体或其他金属尖端的静电效应,由于不同行业可能有不同的放电模型要求。本人仅从汽车电子的角度来分析静电放电模型(消费电子好像是同一个模型?因为这两行业最重要的静电源头都来自于人体放电),汽车电子的放电模型在IEC 61000-4-2中有明确规定,放电模型决定了静电放电电流波形,IEC中的静电放电波形如下图所示。

静电电流频谱分布

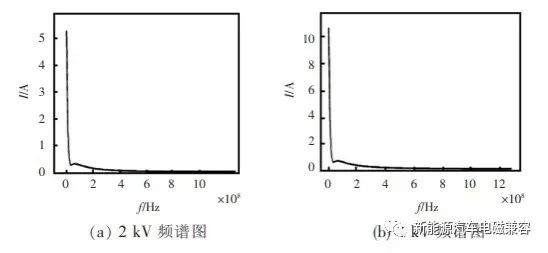

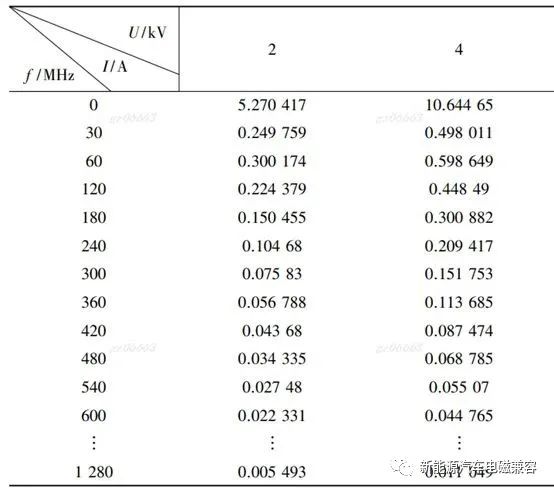

实际上静电放电效应可以简单的认为电容通过电阻放电的效应。都是在前段极短的时间内上升到高点,后慢慢减小。上升时间大概为1ns,持续大约为60ns。该波形确实可以通过数学公式进行标明,但是比较复杂,本文只注重结果,所有不进行表述。该数学公式可以通过傅里叶变换得到静电电流的频谱。如下图所示。

可见, 静电最大的能量还是集中在直流分量上面。 频谱分布从直流到1GHz,因此静电的电路路径会比较复杂。从传导到辐射,都有。但是 静电99%的能量都集中在300MHz之前。 因此,对于过高频率的路径我们可以忽略不计,将注意力集中在分析300MHz带宽的路径上面。大部分的汽车电子产品在进行静电放电测试时,都是通过电源负极对静电电流进行回流(通过金属外壳回流的一般风险也比较小,本文不阐述)。正是因为静电的电流频谱很宽,因此,要完全把握静电电流的路径非常困难,一般要借助二维场求解器。

但是在设计前期,必须要考虑到所有静电放电点到电源负极的直流路径, 为静电的直流分量提供一条低阻抗的路径, 避免该直流分量引起共阻抗耦合的风险!!另外在静电风险比较高的走线,必须在板内放置滤波电容,1nF的贴片电容是比较合适的值(因为谐振点在300MHz左右,对于静电整个频段都有较好的滤波效果)。还有,对于静电电流产生的辐射场导致的问题,非常难于把控,我自己也无法准确说出该类问题的辐射源头。但是基本上是由于高频分量路径过长导致。

仿真和芯片静电等级

另外,产品的静电风险是比较容易进行仿真的一个项目,我们只要仿真出放电点到预设泄放安全点的阻抗-频率曲线和放电点到被害点(敏感芯片管脚或信号)的阻抗-频率曲线,这两个阻抗进行比较,就能够得出到达被害点的静电能量,以评估该放电点的风险。 这个仿真还是比较准确,比较有设计参考意义的。建议静电设计有难度的产品进行开展。 当然,当产品已经设计出来之后,也可以使用网分或阻抗分析仪对放电点和泄放点之间进行测试,如满足一定的阻抗-频率曲线(每个公司都有该曲线的不同理解,需要根据产品情况进行进行约束),则该放电点的静电风险很低。

最后,需要注意的是芯片的datasheet中一般会指出该芯片能够满足的静电放电等级,一般标明的是HBM(人体放电模型)和CDM(带电体放电模型),这两个模型都是为了衡量芯片在生产和运输过程中可能遇到的ESD风险,不适用于产品在日常使用过程中可能遇到的静电问题。这两个模型和IEC中的模型是不同的。但是基本上可以将 IEC的模型认为是HBM模型和CDM模型的叠加。 因此,芯片上标明的ESD等级不能够等同试验中测试的等级,IEC的模型是更加严酷的。

审核编辑:汤梓红

-

ESD技术文档:芯片级ESD与系统级ESD测试标准介绍和差异分析2025-05-15 4899

-

什么是esd?esd的危害有哪些2024-02-16 13450

-

驱动器共模电流路径与数学模型分析2023-09-08 2327

-

案例分享:电单车电控模块ESD故障分析(下)?2023-08-15 3660

-

高速PCB设计——回流路径分析2021-02-05 5201

-

ArcGIS的路径分析2019-06-03 2543

-

ESD静电放电2018-09-21 2647

-

互感--连接器引起串扰的因素分析 如何改变返回电流路径2018-04-16 2235

-

短路径算法分析2016-01-14 817

-

ESD损坏PCB板的原理分析2013-12-25 3359

-

ESD设计与综合2013-09-04 6656

-

ESD保护方法的对比分析2011-07-05 5482

-

ESD保护元件的对比分析及大电流性能鉴定2008-07-29 5121

全部0条评论

快来发表一下你的评论吧 !