FPGA解码MIPI视频OV5647 2line CSI2 720P分辨率采集

电子说

描述

1、前言

FPGA图像采集领域目前协议最复杂、技术难度最高的应该就是MIPI协议了,MIPI解码难度之高,令无数英雄竞折腰,以至于Xilinx官方不得不推出专用的IP核供开发者使用,不然太高端的操作直接吓退一大批FPGA开发者,就没人玩儿了。

本设计基于Xilinx的Kintex7开发板,采集OV5647 摄像头的720P 2Line MIPI视频,OV5647 摄像头引脚接Kintex7的 BANK16 LVDS_25 差分引脚,经过纯vhdl实现的 CSI2 RX模块输出AXIS视频流,再将bayer数据转RGB,再经过FDMA将图像送入DDR3中做三帧缓存后读出,最后经HDMI发送模块输出显示器;

本文详细描述了设计方案,工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

关于MIPI协议,请自行搜索,csdn就有很多大佬讲得很详细,我就不多写这块了;

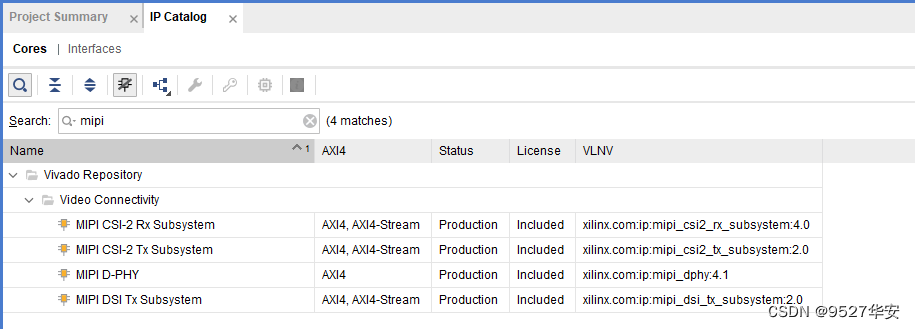

2、Xilinx官方主推的MIPI解码方案

Xilinx官方主推的MIPI解码方案是专用IP核,在vivado的ip仓库里输入MIPI就会看到如下的一堆IP:

Xilinx方案使用很简单,调用IP就行,用SDK配置即可使用,MIPI解码后的数据格式为AXIS,方便与他家的VDMA之类的IP对接,你无须关心复杂的MIPI协议即可畅玩儿MIPI,但问题就来了,如果你用的FPGA不是Xilinx家的怎么办?

3、本 MIPI CSI2 模块性能及其优越性

本方案MIPI解码后的视频时序为VGA时序,即行同步,场同步,数据有效,数据信号;方便后端直接处理;解串部分使用Xilinx源语,本工程用到的是7系列源语,更高级别的FPGA应用,需要更改源语参数,但问题不大;

一个字:牛逼,表现如下:

1:纯Vhdl代码实现,学习性和阅读性达到天花板;

2:移植性还可以,只要兼容Xilinx解串源语的FPGA均可移植;

3:算法达到天花板,标准的CSI2接收协议实现解码;

4:实用性达到天花板,采用OV4689摄像头作为输入,不同于市面上验证性和实验性的工程,本设计直接面向实用工程,贴近真实项目,MIPI输入,2路视频输出,做类似项目的兄弟可直接拿去用,一个月工资直接拿到手。。。

5:支持高达4K分辨率的MIPI视频解码;

6:时序收敛很到位,考虑到MIPI协议的复杂性和时序的高要求,所以没有采用时序收敛不强的verilog,而是VHDL,虽然阅读性可能会低一些,但用户只需要知道用户接口即可,并不需要去看内部的复杂代码;

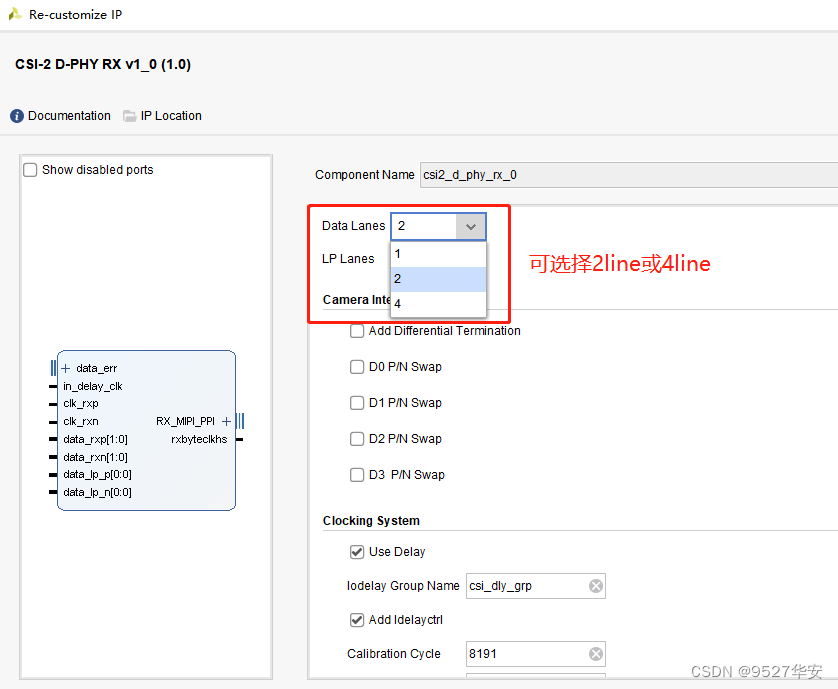

7:自定义IP封装,方便Xilinx系列FPGA用户使用,CSI-2自定义IP支持2line或4line输入,可在IP配置界面手动配置;

4、我这里已有的 MIPI 编解码方案

我这里目前已有丰富的基于FPGA的MIPI编解码方案,主要是MIPI解码的,既有纯vhdl实现的MIPI解码,也有调用Xilinx官方IP实现的MIPI解码,既有2line的MIPI解码,也有4line的MIPI解码,既有4K分辨率的MIPI解码,也有小到720P分辨率的MIPI解码,既有基于Xilinx平台FPGA的MIPI解码也有基于Altera平台FPGA的MIPI解码,还有基于Lattice平台FPGA的MIPI解码,后续还将继续推出更过国产FPGA的MIPI解码方案,毕竟目前国产化方案才是未来主流,后续也将推出更多MIPI编码的DSI方案,努力将FPGA的MIPI编解码方案做成白菜价。。。

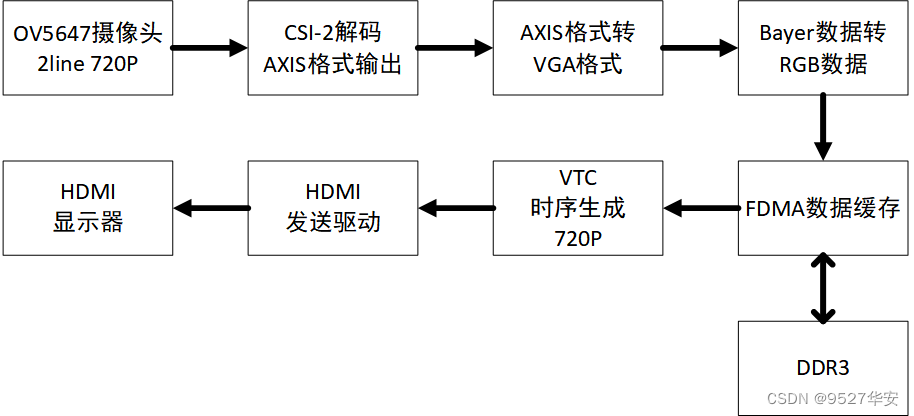

5、详细设计方案

详细设计方案如下:

视频输入:

OV5647摄像头输入,MIPI 2line,720P分辨率;

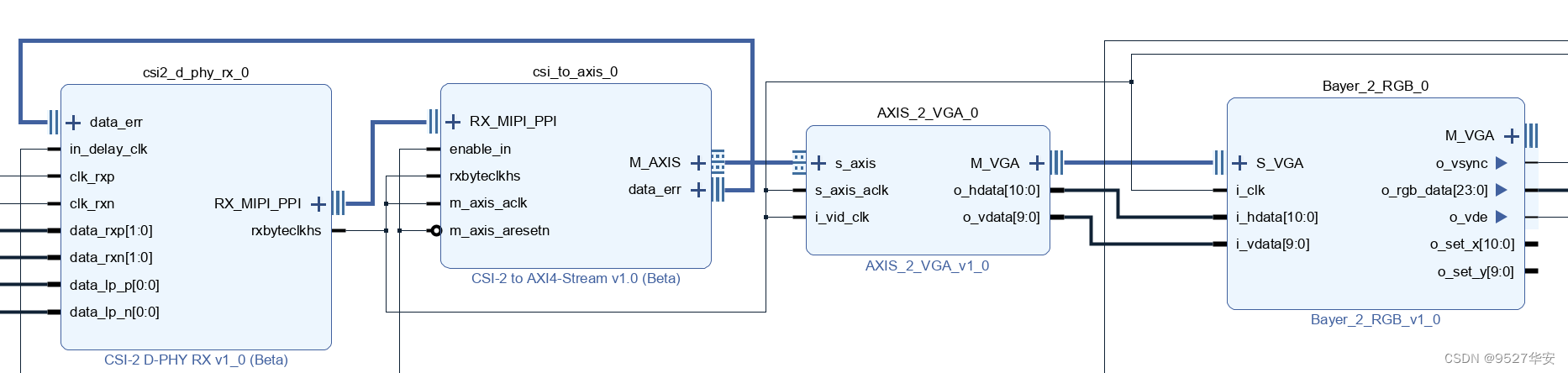

MIPI解码:

纯vhdl代码编写的CSI-2解码器,可针对2line或4line输入的MIPI视频解码,输出为AXIS数据流,经过AXIS转VGA输出VGA格式数据,经Bayer转RGB输出VGA格式的RGB888视频数据;

图像输出:

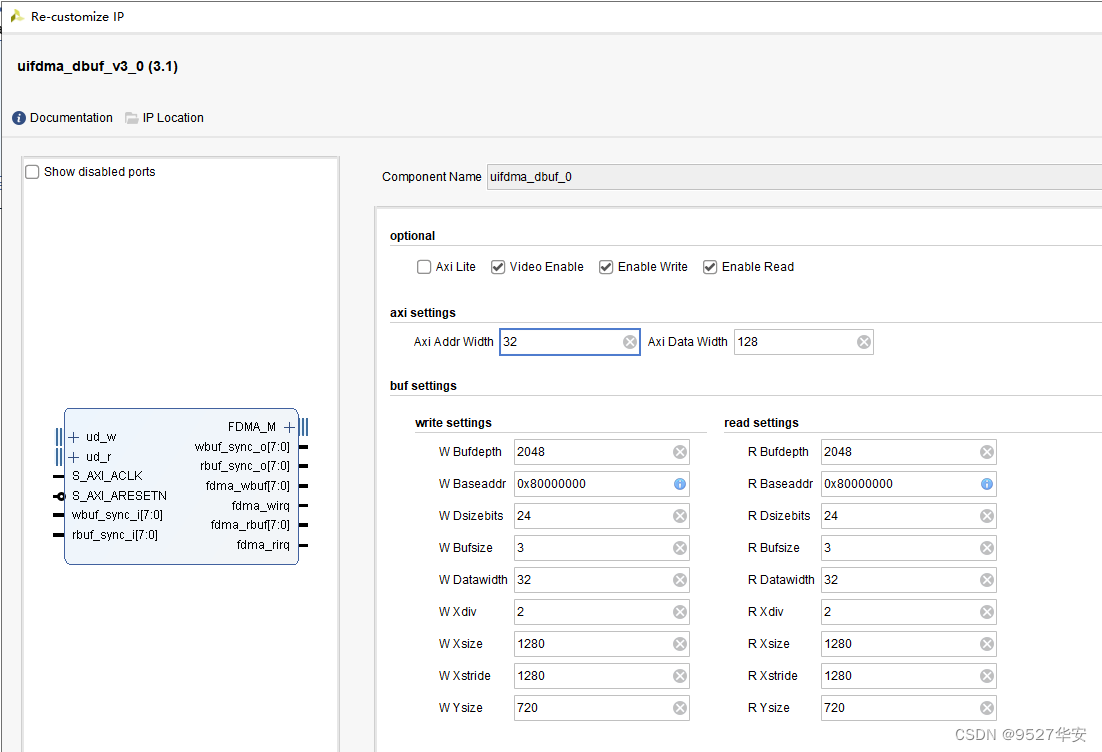

经FDMA图像3帧缓存后,相当于MIPI视频进DDR3逛了一圈又回来了,经过VGA时序发生器VTC和HDMI发送驱动输出显示器,HDMI发送驱动采用纯verilog代码编写,不含任何IP,输出稳定可靠,我项目一直都在用

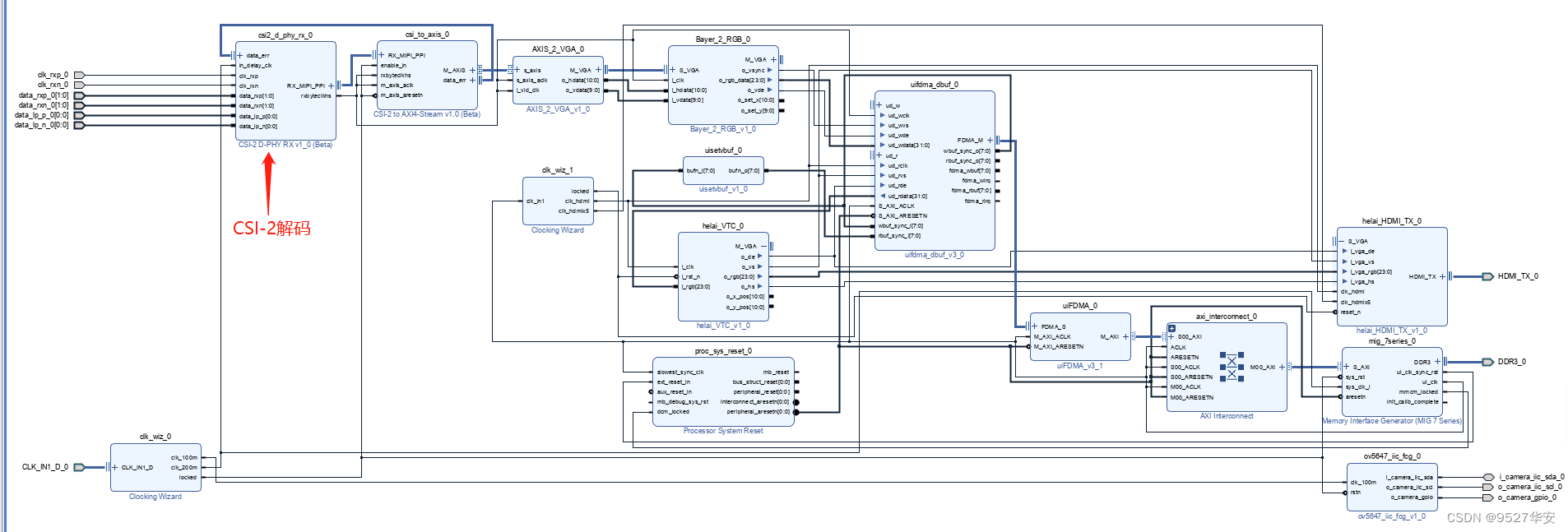

6、vivado工程介绍

开发板:Xilinx Kintex7开发板;

开发环境:vivado2020.2;

输入:OV5647摄像头输入,MIPI 2line,720P分辨率;

输出:HDMI,720P分辨率;

工程BD如下:

MIPI解码部分的IP搭建如下:

CSI-2 IP配置界面如下:

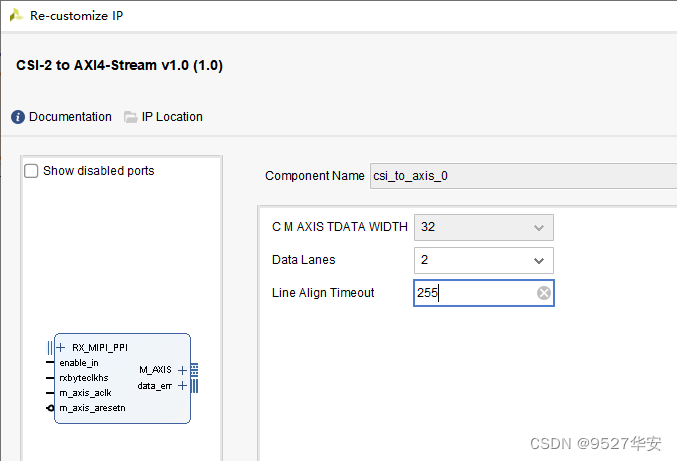

CSI-2转AXIS

FDMA配置如下:

综合后的工程代码架构如下:

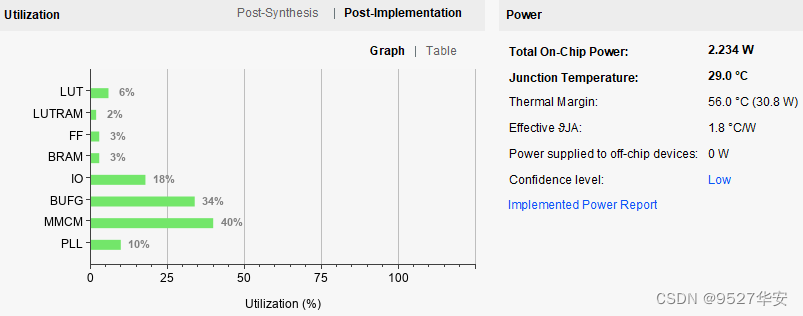

FPGA资源消耗和功耗预估如下:

-

【Milk-V Duo S 开发板免费体验】OV5647摄像头测试2025-07-11 642

-

说说分辨率的720P、1080P、HD、蓝光、2K、4K2023-01-05 136297

-

AN-1337:ADI视频解码器与MIPI CSI-2接收器连接的设计考虑2021-04-19 1053

-

CMOS图像传感器OV5647的数据手册免费下载2020-03-27 2537

-

OV5647传感器的数据手册2019-11-04 11338

-

怎么自动识别视频分辨率和帧频?2019-09-23 2154

-

请教DM6467关于1024x768分辨率的视频处理2018-06-21 2115

-

【小梅哥FPGA】OV5640摄像头资料,含应用手册,1280*720P分辨率,30帧应用工程2018-04-30 43801

-

RGB转MIPI CSI芯片方案TC358746XBG2017-07-10 4986

-

特权FPGA VIP视频图像开发套件例程详解5——VGA SVGA 720p 1080p多分辨率显示驱动2015-10-26 8465

-

无色块10M码流720P 推动高清MP4标准2008-12-30 3485

-

[艾诺]无色块10M码流720P 推动高清MP4标准2008-12-08 2830

全部0条评论

快来发表一下你的评论吧 !