QSPI Flash驱动功能解析和使用注意事项

描述

前言

首先,请问大家几个小小问题,你清楚:

QSPI协议的基本内容与功能应用场景吗?

QSPI Flash驱动读写过程中存在哪些不一样的操作模式呢?

基于AUTOSAR架构下Flash驱动接口有哪些?

在平常使用QSPI Flash接口的过程中存在哪些注意事项呢?

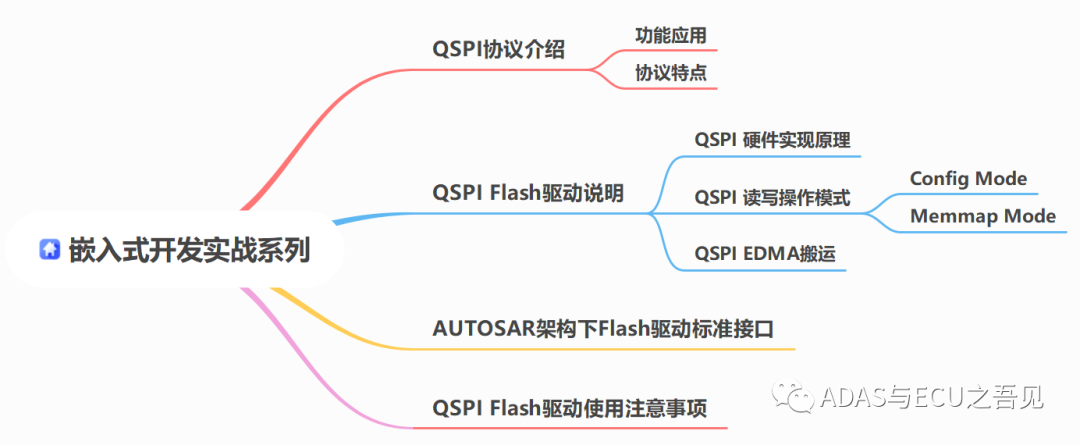

今天,我们来一起探索并回答这些问题。为了便于大家理解,以下是本文的主题大纲:

正文

QSPI协议介绍

QSPI全称为“Queued SPI”,本质上是属于SPI协议的一种,一般来说,SPI协议可以分为Standard SPI,Dual SPI,以及本文要讲解的Queued SPI。只不过Dual SPI,Queued SPI常用于作为SPI Flash的通信接口。

功能应用

QSPI作为一种队列串行外围接口协议,就是对SPI协议的扩展,可以通过单线,双线或四线模式与外部Flash存储器进行高速通信。其功能应用场景如下:

数据存储:可以用来实现大量数据的存储,如代码,图像,视频等,从而提高数据的读写速度与容量;

代码执行:QSPI用于执行外部Flash存储器的代码,这样可以节约内部Flash的空间,如通过QSPI XIP模式从而实现在Memmap下执行代码;

与其他外围设备进行通信:QSPI也可支持与其他QSPI协议的外围设备进行通信,如传感器,显示器等,可以提高通信的效率与灵活性;

协议特点

QSPI协议作为一种SPI协议的扩展,一般而言,可以分为两种工作模式,即设置模式与Memmap模式,虽然也有些芯片存在三种,如STM32,不同芯片存在些许差异可以理解,本质上可以归纳为上述两者;

QSPI协议的命令序列包括指令、地址、交替字节、空指令和数据这五个阶段,任一阶段均可跳过,但至少要包含指令、地址、交替字节或数据阶段之一;

一般而言,QSPI仅支持dual read 与quad read模式,不支持dual write与quad write两种模式,同时也不会存在QSPI 输入与输出的loop back模式;

QSPI Flash驱动说明

虽然市面上存在许多的Flash驱动供应商,但是基本都大同小异,本文已TI系列的QSPI Flash驱动介绍举例给大家介绍下其QSPI的硬件实现原理,读写操作模式以及EDMA搬运等操作。

QSPI硬件实现原理

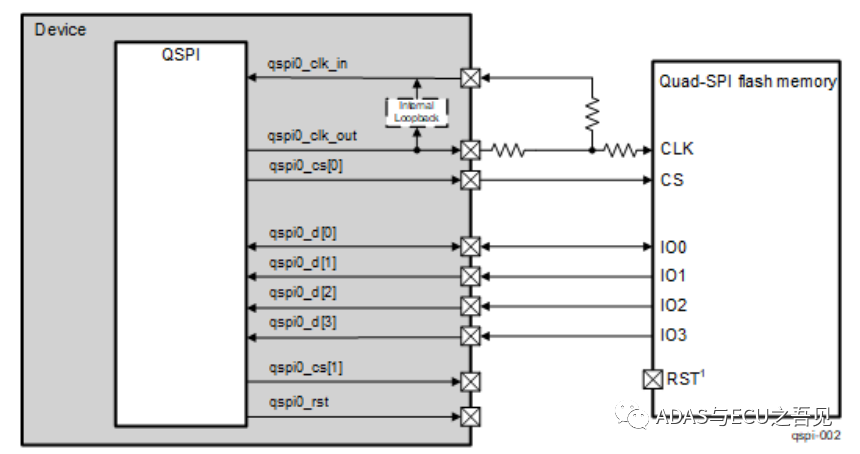

作为QSPI通信的双方,本质上来讲都是主芯片端作为主设备,可以通过控制CS引脚来决定与外围不同的Flash芯片进行通信,同时通过输出Clock时钟来完成针对从设备的通信传输控制,如下图所示:

图1 QSPI硬件连接原理(图片来源于TI官方文档)

左图为主芯片的内部QSPI的控制器,右图则为外部的支持QSPI协议的外部Flash,两者之间通过QSPI协议接口连接,包含1个CLK引脚,1个CS引脚与4个用于传输数据的IO引脚。

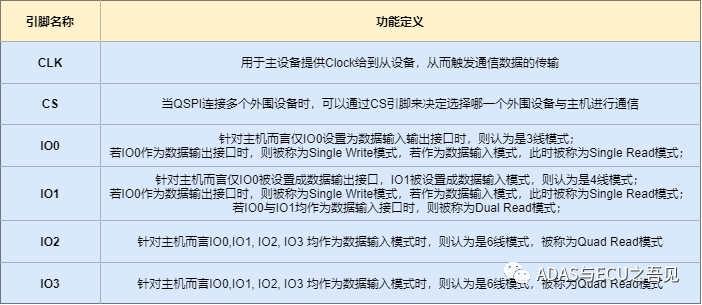

针对上图中的内容,小T将针对每个引脚做个较为详细的介绍,如下表所示:

图2 QSPI接口引脚功能定义

QSPI读写操作模式

通过上述文章我们了解到QSPI存在3线Single Write/Read模式,4线Single Write/ Read,Dual Read模式,6线Quad Read模式的6种QSPI读写方式,在具体的项目实际应用过程中,我们一般推荐正常的写入操作通过4线Single Write来写入,读取操作推荐采用6线Quad Read模式,这样才能最大效率的利用Flash硬件自身特性,从而提高通信效率。

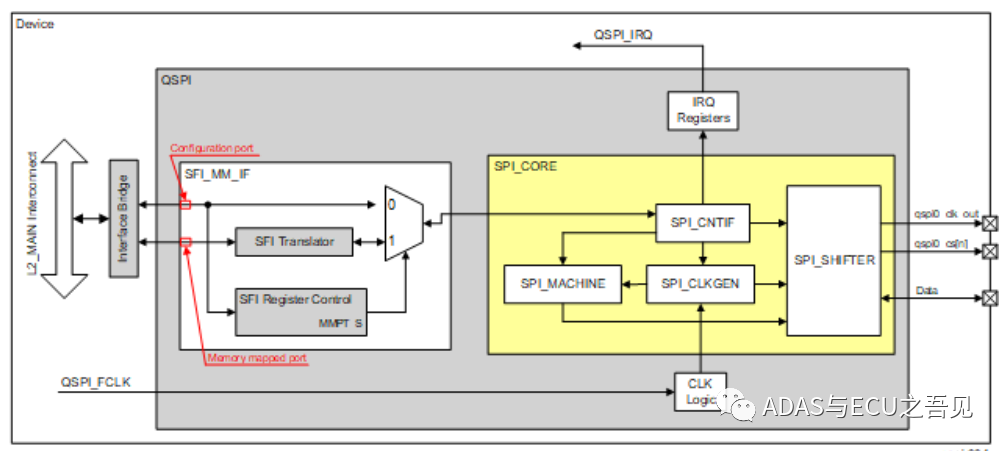

如下图所示为QSPI 控制器的内部组成关系,从中我们可以得出如下几个关键结论:

图3 QSPI控制器接口内部结构(来源于TI官方文档)

整个QSPI控制器可以分为SFI_MM_IF与SPI_CORE两个模块,其中SFI_MM_IF模块主要负责读写指令,地址以及dummy cycle的个数等,而SPI_CORE主要负责芯片的时钟极性与时钟相位以及传输的长度等;

SFI_MM_IF接口由以下两个部分组成:

SFI register control:用来实现上述读写指令的初始化设置;

SFI translator:将对应的SFI register control中的读写指令发送至SPI_CORE模块来外部Flash;

SPI_CORE模块则是由如下四个部分组成:

SPI_CNTIF:SPI Control Interface,用于设置对应的读写指令,时钟极性或相位等,在配置模式下会使用到;

SPI_CLKGEN:SPI Clock Generator,用于设置通信相关的时钟频率;

SPI_MACHINE:SPI State Machine,将SPI_CNTIF中的相关读写指令作为输入,然后控制数据的移位发送等;

SPI_SHIFTER:SPI Data Shifter,用来实现接口信号的捕捉与生成。

QSPI控制器支持两种配置方式,一种是Config模式,另外一种则是Memmap方式;对于写入操作不支持Memmap方式仅支持Config模式,对于读取操作推荐使用Memmap方式,这样便可以直接在芯片MCU的Memory Layout中看到相应的外部Flash空间的代码或者数据。

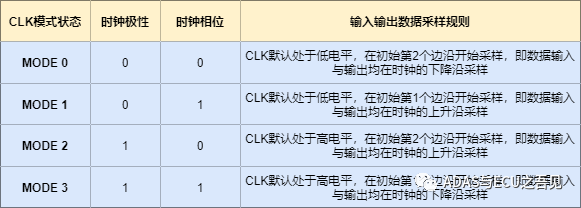

对于QSPI接口的通信双方而言,需要确保两者通信的时钟极性与时钟相位是一致的,时钟极性与时钟相位的组合有如下4种方式:

图4 QSPI时钟极性与时钟相位关系图

QSPI EDMA搬运

当通过QSPI去读取大量数据时,我们推荐使用Memmap方式读取+EDMA的方式来完成,因为通过该两种技术手段的结合,我们便可以减小CPU负担,直接让EDMA去执行对应的数据读取操作;

有关EDMA的具体实现机理就不再本文进行展开,后续将进行单独讲解,欢迎多多关注小T。

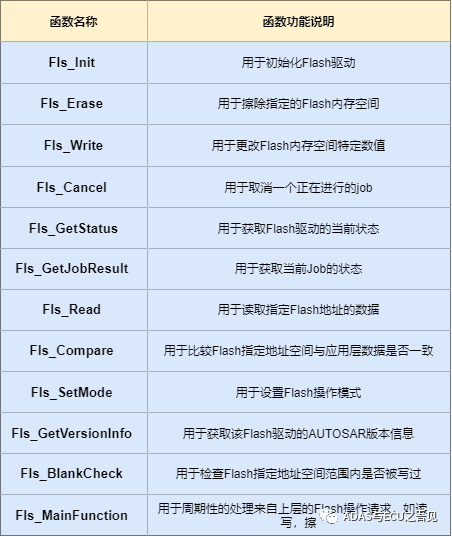

AUTOSASR架构下Flash驱动标准接口

小T将AUTOSAR架构下针对Flash驱动的标准接口以及相关需求列举如下,这样在我们使用Flash驱动过程我们能够快速的了解到Flash驱动的关键API的具体功能与作用。

图5 Flash驱动标准接口表

在使用上述标准的AUTOSAR Flash驱动API也有很多需要注意的地方,小T将自己觉得需要特别注意的点列举如下,这也是大家容易忽视的一些点:

在使用Flash驱动其他读,写等接口之前,务必需调用Fls_Init完成初始化,否则后续的Flash操作请求将会无效;

如果你使用的是外部Flash并采用QSPI驱动,请务必在Fls_Init之前执行QSPI驱动的初始化,保证一个有效的初始化过程;

在执行Flash写入操作时其写入地址与长度均需要与Flash的Page单位进行对齐,如一般为256字节,具体还是取决于Flash芯片型号;

在执行Flash擦除操作时,需确保其擦除地址与长度与Flash的sector单位进行对齐,如一般为4K,具体还是取决于Flash芯片型号;

Fls_Read, Fls_Write等关键API操作均属于异步操作且不可重入,因此需确保Flash驱动的被操作对象的唯一性,不要应用层与Fee模块冲突,统一通过NVM发送请求来完成Flash的操作;

QSPI Flash驱动使用注意事项

小T在具体的软件开发过程中,也遇到过很多跟Flash驱动操作有关的问题,这些问题往往解决起来非常棘手,因为非常偶发且极难复现。

这类问题更多时候还是我们缺乏防御性编程思维,没有针对Flash可能失效的场景进行全面的考虑,以下小T将我个人针对Flash驱动的几个常见的经验总结列举如下,希望能给大家后续的Flash驱动开发带来一些帮助与思考。

在每次系统启动或者复位的过程中,最为推荐的做法针对外部Flash同步进行reset操作,该操作可以一般存在如下三种方式:

每次启动或者复位的过程中可通过硬件来操作Flash的上下电操作来完成Flash自身的重置;

通过软件的方式来拉低Reset引脚来实现外部Flash复位,这种方式需要考虑到引脚复用功能是否可用的可能性;

通过软件的方式在初始化的过程中通过QSPI通信发送软复位指令让Flash芯片进行重置;

如果需要针对外部的SPI Flash通过QSPI进行通信,需要特别注意该SPI Flash芯片的QE位是否默认使能,如果没有使能,将无法采用QUAD SPI进行通信,因此建议工厂端刷写软件过程中均需要主动设置该QE位或者在软件初始化过程中设置该QE位,该QE位一旦写入掉电也会丢失,仅需写入一次即可;

在执行Flash初始化过程中需要针对Flash外部型号,如Manufacture ID等设备号进行校验,确保不会出现生产过程中出现芯片型号贴错的场景;

在软件运行过程中有时会偶发导致系统跑飞意外执行操作Flash驱动写或者擦除操作导致用户程序遭到破坏,从而软件无法正常启动,因此有必要针对关键应用程序代码空间进行Flash写保护,这样即使程序死机复位后整个系统也能够再次正常启动。

审核编辑:汤梓红

-

美国Odyssey奥德赛电池充电注意事项全解析2025-05-19 1284

-

深度剖析 IGBT 栅极驱动注意事项2023-11-24 2015

-

调制驱动器初次使用注意事项2023-07-10 1825

-

微控制器外置QSPI Flash选型的注意事项2023-04-07 3844

-

使用注意事项2023-03-17 750

-

IGBT 栅极驱动注意事项2022-11-15 782

-

APM32F030C8T6_Flash_Flash读写设计注意事项2022-11-09 678

-

门驱动的欠压保护功能及其注意事项2022-11-01 805

-

电调驱动原理是什么?有哪些注意事项?2021-09-24 5004

-

如何开发功能齐全的QSPI驱动2020-09-25 4937

-

继电器驱动电路的原理和注意事项2017-02-06 36670

-

IGBT驱动光耦TLP250的应用及注意事项2012-07-18 59622

-

胆机使用的注意事项2009-11-29 2485

-

IGBT驱动电路布线设计注意事项2008-11-05 4557

全部0条评论

快来发表一下你的评论吧 !